| Blog Icon | Blog Title | |

|---|---|---|

|

FPGAs Create the Optimal Data Accelerator– Achronix Staff,Sr Manager, Product Marketing and Business DevelopmentWith the programmability of a CPU or GPU and the speed of an ASIC, FPGAs offer the optimal efficiency of power and performance when flexibility is a requirement for compute, networking and storage acceleration use cases. |

> |

|

FPGA-Accelerated Large Language Models Used for ChatGPT– Bill Jenkins,Director of Product Marketing, AI/MLIn this blog, we will delve into the difficulties encountered with large language models and explore potential solutions that can pave the way for their enhanced usability and reliability. |

> |

|

FPGA 2022 Conference: Top Four Takeaways– Raymond Nijssen and Michael Riepe,Vice President, Chief Technologist and Sr. Principal EngineerAchronix's Raymond Nijssen and Michael Riepe attended this year's virtual FPGA 22 Conference — an event predominantly focused on the use of FPGAs as data accelerators in AI, ML, genomics, and high-level synthesis. In this blog, Raymond and Michael provide their Top Four Takeaways from the Virtual FPGA 22 Conference. |

> |

|

Four HPC Trends from SC22– Nick Ilyadis, Sr. Director, Product MarketingWith over 11,000 attendees, this year’s Supercomputing Conference was a huge success. After attending excellent sessions and engaging in discussions with both attendees and our fellow exhibitors, here are four major HPC trends from this year’s conference that were significant takeaways. |

> |

|

Five Reasons Why You Should Join Achronix at SC22 in Dallas– Alexandra Saavedra, Demand Generation ManagerSupercomputing 2022, the leading technical program in the high-performance computing community, is right around the corner. Get a sneak peek of some of the exciting topics we’ll be presenting at this year’s conference and five reasons why you should join us! |

> |

|

Enabling Scalable Processing with Achronix FPGAs and Bluespec's RISC-V Soft Processors– Alexandra Saavedra,Demand Generation ManagerAchronix Semiconductor and Bluespec, Inc. have unveiled a highly scalable suite of Linux-capable RISC-V soft processors specifically designed for the Achronix Speedster7t FPGA family. |

> |

|

Embedded FPGAs for Next-Generation Automotive ASICs– Bob SIller,Sr. Marketing ManagerFor anyone who has looked at new cars lately, it's hard not to notice how quickly automotive electronics are advancing. Looking at automotive safety technology from just three years ago vs. today, you see a significant increase in the number of cameras to support applications such as surround-view display, driver distraction monitors, stereo vision cameras, forward-facing and multiple rearview cameras.Speedcore |

> |

|

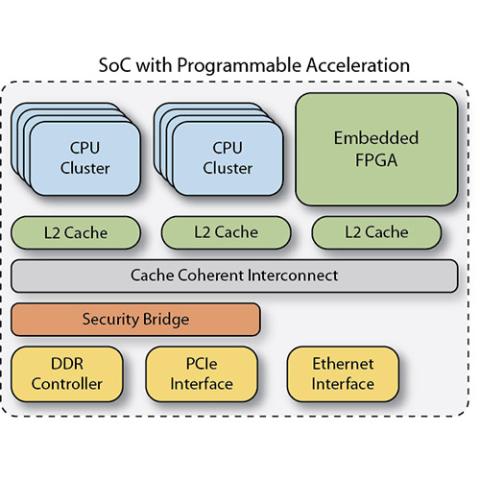

Embedded FPGA – The Ultimate Accelerator– Kent Orthner,Systems ArchitectAn embedded FPGA (eFPGA) is an IP core that you integrate into your ASIC or SoC to get the benefits of programmable logic without the cost, but with better latency, throughput, and power characteristics. With an eFPGA, you define the quantity of look-up-tables (LUTs), registers, embedded memory, and DSP blocks. You can also control the aspect ratio, number of I/O ports, making tradeoffs between power and performance. Achronix delivers a GDS II representation of the Speedcore IP that you can integrate directly into your SoC or ASIC. We also provide you with a custom, full-featured version of our ACE design tools, that you can use to design, verify and program the functionality of the Speedcore eFPGA. |

> |

|

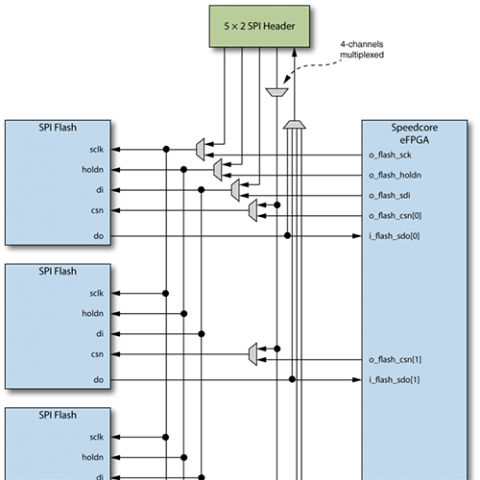

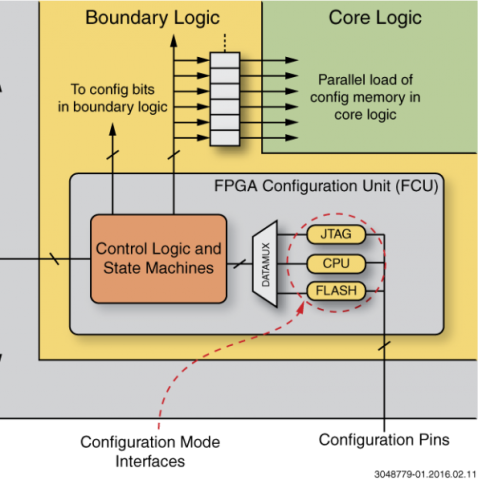

Configuring Your Speedcore eFPGA, Part 2: Configuration Time– Volkan Oktem,Sr. Director of ApplicationAs discussed in part 1 of this blog post, each instance of an Achronix Speedcore eFPGA in your ASIC or SoC design must be configured after the system powers up because Speedcore eFPGAs employ nonvolatile SRAM technology to store its configuration bits. The time required to program a bitstream into a Speedcore eFPGA depends on the configuration mode being used, the data width, clock frequency, and of course, the size of the configuration bitstream. |

> |

|

Configuring your Speedcore eFPGA, Part 1: Configuration Interfaces– Volkan Oktem,Sr. Director of ApplicationEach instance of an Achronix Speedcore eFPGA in your ASIC or SoC design must be configured after the system powers up because Speedcore eFPGAs employ nonvolatile SRAM technology to store the eFPGA’s configuration bits. Each Speedcore instance contains its own FPGA configuration unit (FCU) that initializes, configures, and manages the Speedcore eFPGA’s core logic array. For example, if you instantiate three Speedcore eFPGAs in your ASIC/SoC design, there will be three FCUs on the chip. |

> |