# Speedster7t Soft IP User Guide (UG103)

**Speedster FPGAs**

**Preliminary Data**

# Copyrights, Trademarks and Disclaimers

Copyright © 2021 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedster and VectorPath are registered trademarks, and Speedcore and Speedchip are trademarks of Achronix Semiconductor Corporation. All other trademarks are the property of their prospective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

### **Preliminary Data**

This document contains preliminary information and is subject to change without notice. Information provided herein is based on internal engineering specifications and/or initial characterization data.

### **Achronix Semiconductor Corporation**

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail: info@achronix.com

# Table of Contents

| Chapter - 1: Introduction            | . 8  |

|--------------------------------------|------|

| Chapter - 2: Instructions            | . 9  |

| IO Ring and Core                     | 9    |

| IO Ring                              | . 10 |

| Core                                 | . 11 |

| Chapter - 3: Available Configurators | . 12 |

| Memories                             | . 12 |

| MLPs                                 | . 12 |

| Logic                                | . 12 |

| NAP and AXI                          | . 12 |

| Encryption                           | . 12 |

| Device Management                    | . 12 |

| Chapter - 4: BRAM72K Soft IP         | . 13 |

| Description                          | . 13 |

| Configuration                        | . 13 |

| Write and Read Depth                 | . 15 |

| Examples                             | . 16 |

| Chapter - 5: LRAM Soft IP            | . 17 |

| Description                          | . 17 |

| Utilization                          | . 17 |

| Configuration                        |      |

| Write and Read Depth                 | . 19 |

| Examples                             | . 20 |

| Chapter - 6: ROM Soft IP             | . 21 |

| Description                          |      |

| Configuration                        |      |

| Examples                             | . 24 |

| Chapter - 7: Integer Complex Multiplier Soft IP        | 25 |

|--------------------------------------------------------|----|

| Description                                            | 25 |

| Configuration                                          | 25 |

| Examples                                               | 28 |

| Chapter - 8: Integer Multiplier Soft IP                | 29 |

| Description                                            | 29 |

| Configuration                                          | 29 |

| Examples                                               | 32 |

| Chapter - 9: Integer Parallel Multiplier Soft IP       |    |

| Description                                            | 33 |

| Configuration                                          | 33 |

| Input Format                                           |    |

| Output Format                                          |    |

| Examples                                               | 37 |

| Chapter - 10: Integer Parallel Sum of Products Soft IP | 38 |

| Description                                            | 38 |

| Configuration                                          |    |

| Examples                                               |    |

|                                                        |    |

| Chapter - 11: Integer Parallel Sum of Squares Soft IP  |    |

| Description                                            |    |

| Input Packing                                          |    |

| Examples                                               |    |

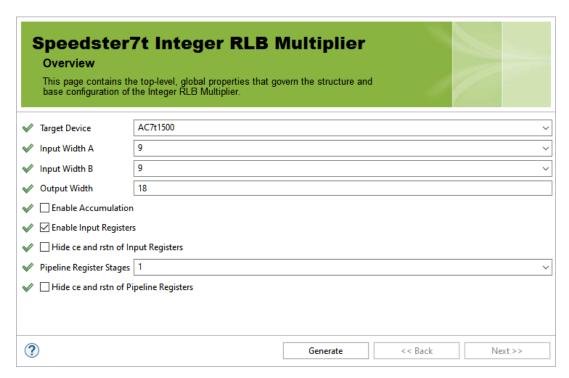

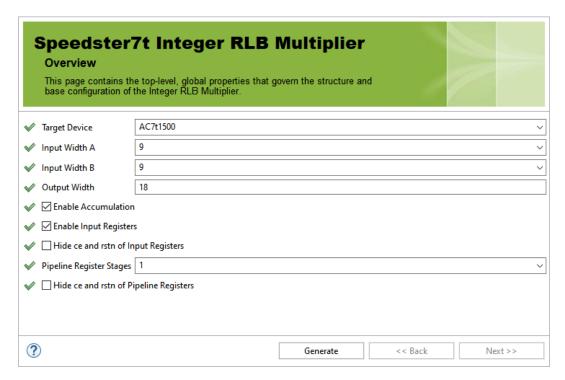

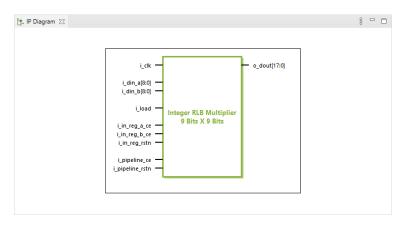

| Chapter - 12: Integer RLB Multiplier Soft IP           |    |

| Description                                            |    |

| Configuration                                          |    |

| Examples                                               |    |

| Chapter - 13: Floating Point Adder                     |    |

|                                                        |    |

| Description                                            |    |

| Ports                                                  |    |

| Files                                                  |    |

|                                                        |    |

| Examples                                         | 56 |

|--------------------------------------------------|----|

| Chapter - 14: Floating Point Multiplier          | 57 |

| Description                                      | 57 |

| Configuration                                    | 57 |

| Ports                                            | 59 |

| Files                                            | 60 |

| Examples                                         | 61 |

| Chapter - 15: Floating Point Multiplier Plus     | 62 |

| Description                                      | 62 |

| Configuration                                    | 62 |

| Ports                                            |    |

| Files                                            | 65 |

| Examples                                         | 66 |

| Chapter - 16: Floating Point Parallel Multiplier | 67 |

| Description                                      | 67 |

| Configuration                                    | 67 |

| Ports                                            |    |

| Files                                            |    |

| Examples                                         |    |

| Chapter - 17: Floating Point Sum of Products     |    |

| Description                                      | 72 |

| Configuration                                    | 72 |

| Ports                                            |    |

| Files                                            |    |

| Examples                                         |    |

| Chapter - 18: Shift Register                     |    |

| Description                                      |    |

| Configuration                                    |    |

| Examples                                         | 80 |

| Chapter - 19: Speedster7t AXI Initiator NAP      | 81 |

| Description                                      | 81 |

| Configuration                                    | 81 |

|                                                  |    |

| Files                                       | 83  |

|---------------------------------------------|-----|

| Examples                                    | 84  |

| Chapter - 20: Speedster7t AXI Responder NAP | 86  |

| Description                                 |     |

| Configuration                               |     |

| Files                                       |     |

| Examples                                    | 89  |

| Chapter - 21: Speedster7t Device Manager    | 91  |

| Description                                 |     |

| Configuration                               |     |

| File Generation                             |     |

| Ports                                       | 94  |

| Examples                                    | 96  |

| Using the JTAG Interface                    | 97  |

| JTAG Connection                             |     |

| Accessing the ACX_DEVICE_MANAGER with ACE   | 98  |

| ACX_DEVICE_MANAGER Commands                 |     |

| use_acx_device_manager                      |     |

| mcu_status                                  |     |

| mcu_info                                    |     |

| noc_delay                                   |     |

| set_csr_clock                               |     |

| fpga_temp                                   |     |

| fpga_temp_to_c                              |     |

| fpga_c_to_temp                              |     |

| Sharing the JTAG Interface with Snapshot    | 107 |

| FPGA Temperature                            |     |

| Simulation                                  | 108 |

| Instantiation Example                       | 109 |

| Example Template                            |     |

| Using Without Snapshot                      | 110 |

| Using With Snapshot                         | 111 |

| Revision History                            | 112 |

# Chapter - 1: Introduction

There are a number of available soft IP cores for the Speedster®7t family of FPGAs. Each of these cores has an IP configurator within ACE that allows configuration of the soft IP core. When configured, the generated wrapper for the core can be instantiated within a user project enabling both synthesis and simulation of the design.

This document describes the available soft IP cores and the methods for configuration and instantiation of each. Soft IP cores are primarily implemented using the components present in the FPGA programmable fabric. For details of these components, refer to the *Speedster7t IP Component Library User Guide* (UG086).

# Chapter - 2: Instructions

Within ACE, all IP cores are accessed using the IP perspective (see the "Perspectives" chapter in the *ACE User Guide* (UG070). The flow and method for generating user IP cores is fully detailed in the "Creating an IP Configuration" chapter in the ACE User Guide. Unless directed otherwise in the following sections, follow the instructions in the ACE User Guide.

# **IO Ring and Core**

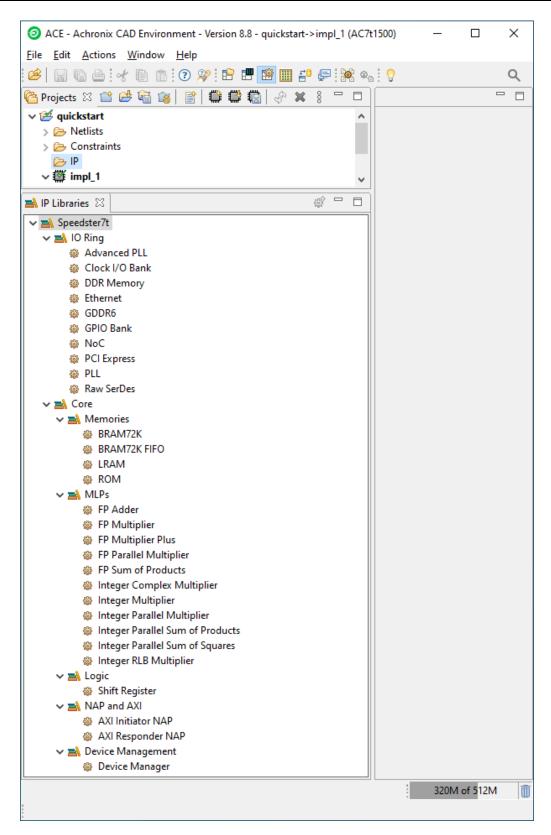

Within the Speedster7t FPGA there are two categories of IP core. These are listed within the IP Libraries pane as **IO Ring** and **Core**. For the Speedster7t family of FPGAs, the following soft IP cores are available:

Figure 1: Speedster7t IP Libraries View

### 10 Ring

The I/O ring contains the configuration for each of the IP cores located in the I/O ring of the FPGA such as the clock banks, PLLs, GDDR, DDR, GPIO, PCIe, 2D NoC, SerDes and Ethernet. The configuration of each of these IP cores is detailed in its respective User Guide.

### Core

The **Core** view contains the available IP configurators for the selected target FPGA used in the project. For the Speedster7t FPGAs, the available soft cores are shown above (see page 10), and listed in the Available Configurators (see page 12) chapter. The details of how to configure each of these cores are given in the appropriate chapter.

# Chapter - 3: Available Configurators

### **Memories**

- BRAM72K Soft IP (see page 13) for creating large block RAM memory arrays

- LRAM Soft IP (see page 17) for creating large logic RAM memory arrays

- ROM Soft IP (see page 21) for creating ROMs constructed of either block RAM or logic RAM

### **MLPs**

- Integer Complex Multiplier Soft IP (see page 25) for creating a complex multiplier with a single machine learning processing block.

- Integer Multiplier Soft IP (see page 29) for creating a single multiplier of up to 32 × 32

- Integer Parallel Multiplier Soft IP (see page 33) for creating parallel multipliers of up to 32 × 32

- Integer Parallel Sum of Products Soft IP (see page 38) for integer sum of products from up to 24 multipliers

- Integer Parallel Sum of Squares Soft IP (see page 43) for integer sum of squares inputs

- Integer RLB Multiplier Soft IP (see page 48) for creating a single multiplier using RLBs in the fabric logic

### Logic

• Shift Register Soft IP (see page 77) – for creating DFF-based shift registers

### NAP and AXI

- AXI Initiator NAP Soft IP (see page 81) for creating a NAP that initiates AXI traffic

- AXI Responder NAP Soft IP (see page 86) for creating a NAP that responds to AXI traffic

# Encryption

Cryptographic Engine Soft IP – for creating the cryptographic engine required in the Speedster7t AC7t1550 FPGA

### **Device Management**

Device Manager Soft IP (see page 91) – for creating the Achronix Device Manager to run GDDR6 training and used in all builds to manage JTAG communication

# Chapter - 4: BRAM72K Soft IP

### Description

The Speedster7t BRAM72K soft IP core creates an arbitrary sized memory array, comprised of ACX\_BRAM72K primitives. The macro employs the embedded data and address cascade paths between ACX\_BRAM72K primitives enabling fast connections for both address and data paths.

If only a single ACX\_BRAM72K is required, this primitive can be inferred or instantiated in the code directly. However, if a memory array comprising multiple BRAM72K blocks is required, it is recommended to use the soft IP configuration to enable the optimum architecture.

# Configuration

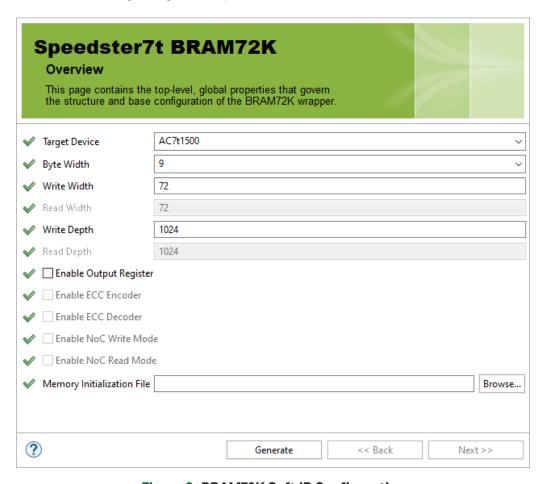

The user macro has the following configuration options:

Figure 2: BRAM72K Soft IP Configuration

**Table 1: Configuration Options**

| Name                                          | Default  | Range                         | Description                                                                                                                                                                                                                                                          |

|-----------------------------------------------|----------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Device                                 | AC7t1500 | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                                       |

| Byte Width                                    | 9        | 8, 9                          | Determines whether fields should be set to 8-bit or 9-bit.                                                                                                                                                                                                           |

| Write Width                                   | 72       | 1 to 9216                     | Write port data width. Values greater than 144 limit the write depth to 16K words.                                                                                                                                                                                   |

| Read Width                                    | 72       | 1 to 9216                     | Read port data width. Currently set to match the write width. This value cannot be changed by the user. Future releases of this user macro are planned to allow configuring different write and read widths.                                                         |

| Write Depth                                   | 1024     | 512 to<br>1048576             | Write port address depth. The maximum value is limited by the number of BRAM72K blocks in a column in the target device. The maximum value is also dependant on the write width as detailed in Write and Read Depths versus Data Width (see page 15)                 |

| Read Depth                                    | 1024     | 512 to<br>1048576             | Read port address depth. Currently set to match the write depth. This value cannot be changed by the user. Future releases of this user macro are planned to allow configuring different write and read depths.                                                      |

| Enable Output Register                        | Off      | On, Off                       | Determines whether the output register in each of the BRAM72K primitives is enabled. Adds an additional cycle of latency to any read operation.                                                                                                                      |

| Enable ECC Encoder                            | Off      | On, Off                       | Determines whether the ECC encoder is enabled for writes to the memory array. This option is currently disabled and cannot be set by the user.                                                                                                                       |

| Enable ECC Decoder                            | Off      | On, Off                       | Determines whether the ECC encoder is enabled for reads from the memory array. This option is currently disabled and cannot be set by the user.                                                                                                                      |

| Enable NoC Write Mode                         | Off      | On, Off                       | Determines whether the BRAM can be written directly from the NoC. This option is currently disabled and cannot be set by the user.                                                                                                                                   |

| Enable NoC Read Mode                          | Off      | On, Off                       | Determines whether the BRAM can be read directly from the NoC. This option is currently disabled and cannot be set by the user.                                                                                                                                      |

| Use Memory Initialization File <sup>(1)</sup> | Off      | On, Off                       | Determines whether a memory initialization file is used to initialize the memory contents. This initialization occurs for both synthesis and simulation. When this option is enabled, entry of the file location in the associated file browser dialog is permitted. |

### **Table Notes**

1. If relative paths are used for the memory initialization file location, the same relative paths must be valid from both the ACE project directory and the simulation directory. It is recommended to locate both of these directories at the same relative depth in the project tree, and to use relative paths that navigate up the tree to the first common directory, before descending the tree to the location of the files.

### Write and Read Depth

### **Absolute Limits**

The write and read depths are related to the write and read widths. The absolute limit on these values is detailed in the following table:

Table 2: Write and Read Depths Versus Data Width

| Memory Width | Maximum Memory Depth |

|--------------|----------------------|

| 1 to 144     | 1048576              |

| 145 to 9216  | 16384                |

### **Device Specific Limits**

Within a device, the largest memory that can be generated is limited by the number of ACX\_BRAM72K primitives in a column. For example, if there are 64 ACX\_BRAM72K primitives in a column, then the maximum memory size is  $64 \times 72$ K bits = 4,718,592 bits. This would support a configuration of 72-bits  $\times 64$ K depth, or 36-bits  $\times 128$ K depth.

# Examples

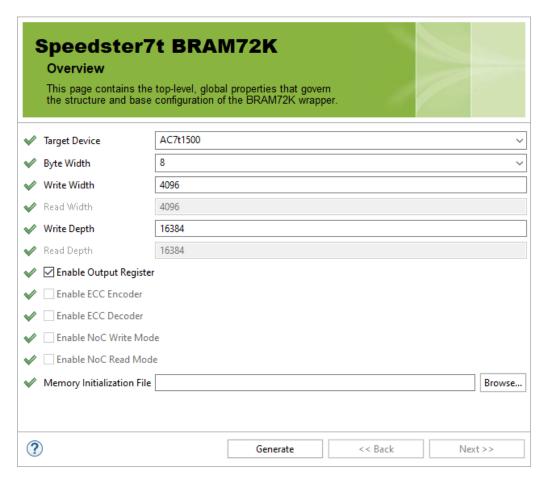

The following figure shows the macro configured for a 4096-bit by 16,384 entry memory with the memory output register enabled:

Figure 3: 4096 × 16K Memory Configuration

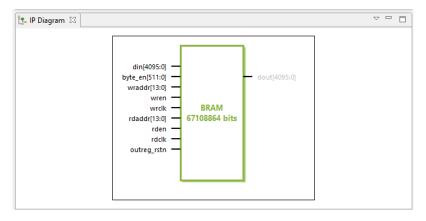

The following figure shows the IP diagram for the above configuration:

Figure 4: 4096 × 16K Memory IP Diagram

# Chapter - 5: LRAM Soft IP

### Description

The LRAM soft IP core creates an arbitrary sized memory array comprised of LRAM primitives.

If only a single LRAM is required, this primitive can be inferred or instantiated into the code directly. However, if a memory array consisting of multiple LRAM primitives is required, it is recommended to use the soft IP configurator to achieve the optimum architecture.

### Utilization

### Note

Within the Speedster7t family, the LRAM and MLP primitives share a site. Therefore if a site is allocated for use as an LRAM primitive, the MLP on that same site cannot be used.

### Configuration

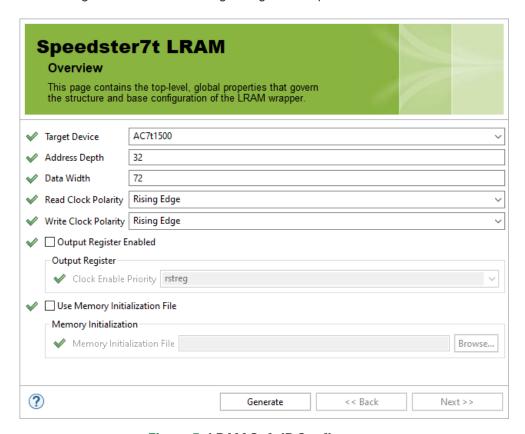

The LRAM2K soft IP configurator has the following configuration options:

Figure 5: LRAM Soft IP Configurator

**Table 3: Configuration Options**

| Name                                          | Default     | Range                         | Description                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------|-------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Device                                 | AC7t1500    | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                                                                                  |

| Address Depth                                 | 32          | 4 to 4096                     | Address depth of the memory array in words. The depth imposes limitations on the maximum data width. The limits are detailed in Read and Write Depths Versus Data Widths (see page 19).                                                                                                                         |

| Data Width                                    | 72          | 1 to 184320                   | Data port width in bits of both din and dout.                                                                                                                                                                                                                                                                   |

| Read Clock Polarity                           | Rising Edge | Falling or<br>Rising Edge     | The rdclk active edge on which all read transactions will occur.                                                                                                                                                                                                                                                |

| Write Clock Polarity                          | Rising Edge | Falling or<br>Rising Edge     | The wrclk active edge on which all write transactions will occur.                                                                                                                                                                                                                                               |

| Output Register Enabled                       | Off         | On, Off                       | Determines whether the output register in each of the LRAM primitives is enabled. This adds an additional cycle of latency to any read operation. If the output register is disabled, the memory array is combinatorial. The output changes when the input address changes.                                     |

| Output Register Clock<br>Enable Priority      | rstreg      | rstreg, rstce                 | Controls the clock enable input of the output register.  • rstreg: The outregce input is ignored when rstregn = 1'b0. The output register is reset on the next active rdclk edge.  • rstce:outregce must be equal to 1'b1 and rstregn = 1'b0 for the output register to be reset on the next active rdclk edge. |

| Use Memory Initialization File <sup>(1)</sup> | Off         | On, Off                       | Determines whether a memory initialization file is used to initialize the memory contents. This initialization occurs for both synthesis and simulation. When this option is enabled, entry of the file location in the associated file browser dialog is permitted.                                            |

### **Table Notes**

1. If relative paths are used for the memory initialization file location, the same relative paths must be valid from both the ACE project directory and the simulation directory. It is recommended to locate both these directories at the same relative depth in the project tree, and to use relative paths that navigate up the tree to the first common directory, before descending the tree to the location of the files.

For example, the Achronix reference designs locate the ACE project in cproject root>/src/ace. The simulation directories are located in cproject root>/sim/vcs or cproject root>/sim/questa. The memory initialization files are located in cproject root>/src/mem\_init\_files. A relative path correct for both simulation and ACE is " ../../src/mem\_init\_files/filename.txt".

# Write and Read Depth

### **Absolute Limits**

The write and read depths are related to the write and read widths. The absolute limit on these values is detailed in the following table:

Table 4: Write and Read Depths versus Data Width

| Memory Width | Maximum Memory Depth |

|--------------|----------------------|

| 4 to 32      | 184320               |

| 33 to 64     | 92160                |

| 65 to 96     | 61416                |

| 97 to 128    | 46080                |

| 129 to 144   | 36864                |

### **Device Specific Limits**

Within a device, the largest memory that can be generated is limited by the number of ACX\_LRAM primitives in a column. For example, if there are 64 ACX\_LRAM2K primitives in a column, the maximum memory size is 64 × 2K bits = 131,027 bits. This would support a configuration of 64-bits x 2K depth, or 32-bits × 4K depth.

Alternatively, if there are 64 ACX\_LRAM4K in a column, the maximum memory size is 64 × 4K bits = 262,144 bits. This would support a configuration of 64-bits × 4K depth, or 32-bits × 8K depth.

The type of LRAM used by the Speedster7t LRAM configurator is dependent upon the device chosen and the available LRAM types within the fabric.

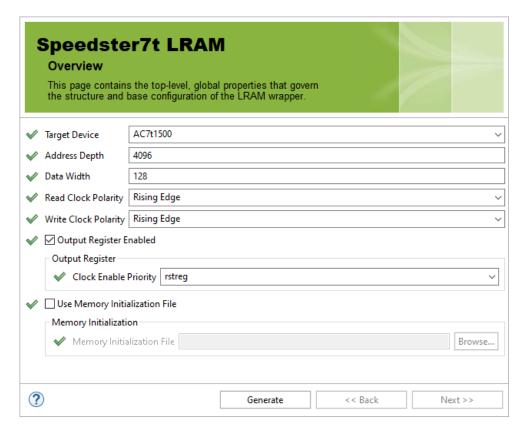

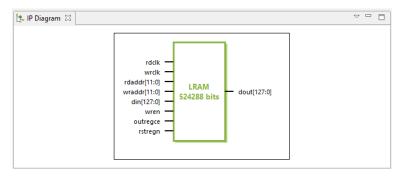

# Examples

The following figure shows the soft IP configured for a 128-bit × 4096-word LRAM memory with the memory output register enabled:

Figure 6: 128-Bit x 4096-Word LRAM Memory Configuration

The following figure shows the IP diagram for the above configuration:

Figure 7: 128-Bit x 4096-Word LRAM Memory IP Diagram

# Chapter - 6: ROM Soft IP

# Description

The Speedster7t ROM soft IP core creates an arbitrary sized ROM, using either BRAM or LRAM primitives.

### Utilization

### Note

Within the Speedster7t family, the LRAM and MLP primitives share a site. Therefore, if using a Speedster7t device, and if the ROM soft IP configuration selects an LRAM to implement the ROM, the MLPs on the sites used by the ROM cannot be used.

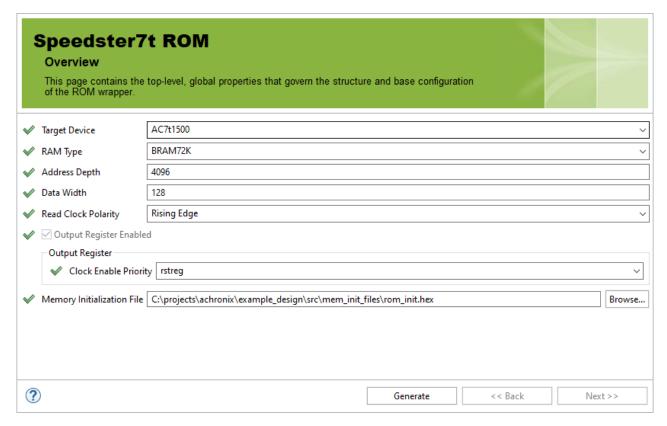

# Configuration

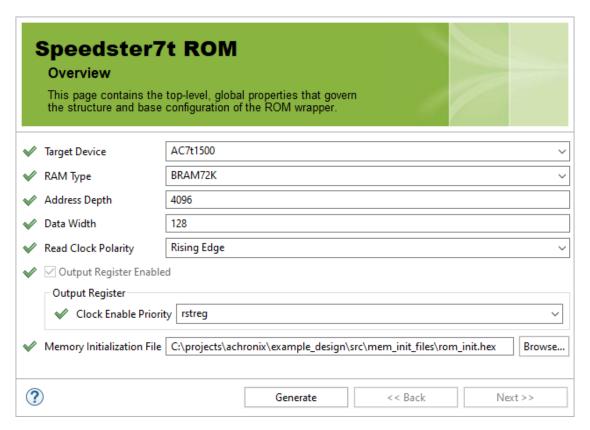

The soft IP has the following configuration options:

Figure 8: ROM Soft IP Configuration

**Table 5: Configuration Options**

| Name                                          | Default     | Range                         | Description                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------|-------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Device                                 | AC7t1500    | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                                                                                   |

| RAM Type                                      | BRAM72K     | BRAM72K,<br>LRAM2K            | Determines which type of RAM primitives used to form the ROM.                                                                                                                                                                                                                                                    |

| Address Depth                                 | 1024        | 4 to 16384                    | Address depth of the ROM in words.                                                                                                                                                                                                                                                                               |

| Data Width                                    | 20          | 1 to 184320                   | Port width in bits of the dout port. The width selected affects the available address depth. The maximum values of width versus depth are detailed in Rea d and Write Depths Versus Data Widths (see page 23).                                                                                                   |

| Read Clock Polarity                           | Rising Edge | Falling or<br>Rising Edge     | The rdclk active edge on which all read transactions will occur.                                                                                                                                                                                                                                                 |

| Enable Output Register                        | Off         | On, Off                       | Determines whether the output register in each of the LRAM2K primitives is enabled. Adds an additional cycle of latency to any read operation. If the output register is disabled, the memory array is combinatorial. The output changes when the input address changes.                                         |

| Output Register Clock<br>Enable Priority      | rstreg      | rstreg, rstce                 | Controls the clock enable input of the output register.  • rstreg: The outregce input is ignored when rstregn = 1'b0. The output register is reset on the next active rdclk edge.  • rstce: outregce must be equal to 1'b1 and rstregn = 1'b0 for the output register to be reset on the next active rdclk edge. |

| Use Memory Initialization File <sup>(1)</sup> | On          | On                            | Location of the memory initialization file used to initialize the memory contents. This initialization occurs for both synthesis and simulation.                                                                                                                                                                 |

### **Table Notes**

1. If relative paths are used for the memory initialization file location, the same relative paths must be valid from both the ACE project directory and the simulation directory. It is recommended to locate both of these directories at the same relative depth in the project tree, and to use relative paths that navigate up the tree to the first common directory, before descending the tree to the location of the files.

### Write and Read Depth

### **Absolute Limits**

The write and read depths are related to the write and read widths. The absolute limit of these values is detailed in the following table:

Table 6: Write and Read Depths Versus Data Width

| RAM Type    | Memory Width    | Maximum Memory Depth |

|-------------|-----------------|----------------------|

|             | 1 to 11520      | 16384                |

|             | 11521 to 23040  | 8096                 |

| ACX_BRAM72K | 23041 to 46080  | 4096                 |

|             | 46081 to 92160  | 2048                 |

|             | 92161 to 184320 | 1024                 |

|             |                 |                      |

|             | 1–1440          | 4096                 |

|             | 1441 to 2880    | 2048                 |

|             | 2881 to 5760    | 1024                 |

| ACV I DAMOK | 5761 to 11520   | 512                  |

| ACX_LRAM2K  | 11521 to 23040  | 256                  |

|             | 23041 to 46080  | 128                  |

|             | 46081 to 92160  | 64                   |

|             | 92161 to 184320 | 32                   |

### **Device Specific Limits**

Within a device, the largest memory that can be generated is limited by the number of RAM primitives in a column, and the choice of RAM type. The overall ROM limit in bits is equivalent to the number of RAM primitives in a column multiplied by the number of bits in the primitive, (72K for ACX\_BRAM72K, and 2K for ACX\_LRAM2K).

# Examples

The following figure shows the soft IP configured for a 128-bit × 4096-word ROM formed of BRAM72K primitives with the memory output register enabled.

Figure 9: 128-bit × 4096-word ROM Configuration

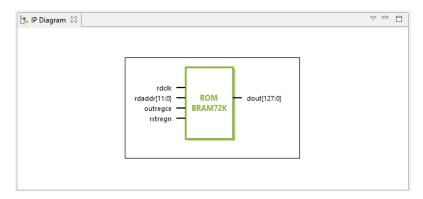

The following figure shows the soft IP I/O diagram for the above configuration.

Figure 10: 128-Bit × 4096-Word ROM IP Diagram

# Chapter - 7: Integer Complex Multiplier Soft IP

# Description

The Integer Complex Multiplier Soft IP implements a complex multiplication with a single machine learning processing block.

# Configuration

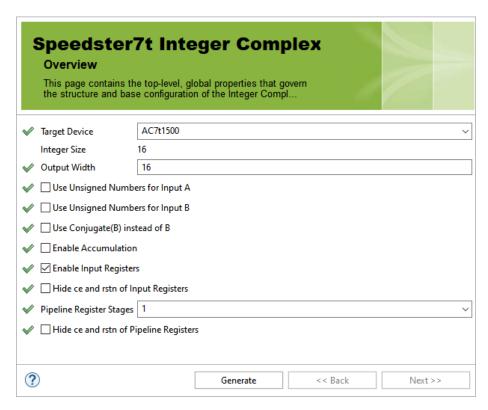

The integer complex multiplier soft IP configurator has the following options:

Figure 11: Complex Integer Multiplier Soft IP Configurator

**Table 7: Configuration Options**

| Name                                   | Default  | Range                         | Description                                                                                                                                                                                                                                               |

|----------------------------------------|----------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Device                          | AC7t1500 | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                            |

| Use Unsigned Numbers for Input A       | No       | Yes, No                       | 0 - i_din_a_re and i_din_a_im are signed (two's complement). 1 - i_din_a_re and i_din_a_im are unsigned.                                                                                                                                                  |

| Use Unsigned Numbers for Input B       | No       | Yes, No                       | 0 - i_din_b_re and i_din_b_im are signed (two's complement). 1 - i_din_b_re and i_din_b_im are unsigned.                                                                                                                                                  |

| Use Conjugate(B) instead of B          | No       | Yes, No                       | Compute A × conjugate(B) instead of A × B.                                                                                                                                                                                                                |

| Enable Accumulation                    | No       | Yes, No                       | 0 - No accumulation: (dout_re + dout_im · j) = (i_din_a_re + i_din_a_im · j) × (i_din_b_re + i_din_b_im · j).  1 - Accumulation: dout_re + dout_im · j is the accumulated value. The start of accumulation is signaled by asserting i_load = 1.           |

| Enable Input Registers                 | No       | Yes, No                       | 0 - No input registers.  1 - i_din_a_re, i_din_a_im, i_din_b_re, and i_din_b_im are registered. The input registers are controlled by the i_in_reg_a_ce, i_in_r eg_b_ce, and i_in_reg_rstn inputs. Enabling the input register adds one cycle of latency. |

| Hide ce and rstn of Input Registers    | No       | Yes, No                       | If selected, the i_in_reg_a_ce, i_in_reg_b_ce, and i_in_reg_rstn inputs will be automatically tied high (1 'b1).                                                                                                                                          |

| Pipeline Register Stages               | 0        | 0, 1, 2                       | The number of pipeline registers, not counting the input register. The total latency is pipeline_regs + in_reg_enable.                                                                                                                                    |

| Hide ce and rstn of Pipeline Registers | No       | Yes, No                       | If selected, the i_pipeline_ce and i_pipeline_rstn inputs will be automatically tied high (1'b1).                                                                                                                                                         |

### **Table 8: Ports**

| Name                             | Direction | Description                                                                                                                                      |

|----------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| i_clk                            | Input     | Clock input, used for the (optional) registers and accumulator.                                                                                  |

| i_din_a_re[(Integer Size - 1):0] | Input     | Real coefficient of A data input to multiplier.                                                                                                  |

| i_din_a_im[(Integer Size - 1):0] | Input     | Imaginary coefficient of A data input to multiplier.                                                                                             |

| i_din_b_re[(Integer Size - 1):0] | Input     | Real coefficient of B data input to multiplier.                                                                                                  |

| i_din_b_im[(Integer Size - 1):0] | Input     | Imaginary coefficient of B data input to multiplier.                                                                                             |

| i_load                           | Input     | Resets the accumulator to A × B, ignoring the previous value. This signal is internally pipelined to have the same latency as A × B.             |

| i_in_reg_a_ce                    | Input     | (Optional) Clock enable for i_din_a_re and i_din_a_im. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                          |

| i_in_reg_b_ce                    | Input     | (Optional) Clock enable for i_din_b_re and i_din_b_im. Present when <b>Enable</b> Input Registers is set to <b>On</b> .                          |

| i_in_reg_rstn                    | Input     | (Optional) Synchronous active-low reset for input registers. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                    |

| i_pipeline_ce                    | Input     | (Optional) Clock enable for pipeline and accumulator registers. Present when <b>Pipeline Register Stages</b> is greater than 0.                  |

| i_pipeline_rstn                  | Input     | (Optional) Synchronous active-low reset for pipeline and accumulator registers.  Present when <b>Pipeline Register Stages</b> is greater than 0. |

| o_dout_re[(Output Width - 1):0]  | Output    | Real coefficient of the result of multiplication and accumulation. Always signed (2's complement).                                               |

| o_dout_im[(Output Width - 1):0]  | Output    | Imaginary coefficient of the result of multiplication and accumulation. Always signed (2's complement).                                          |

# Examples

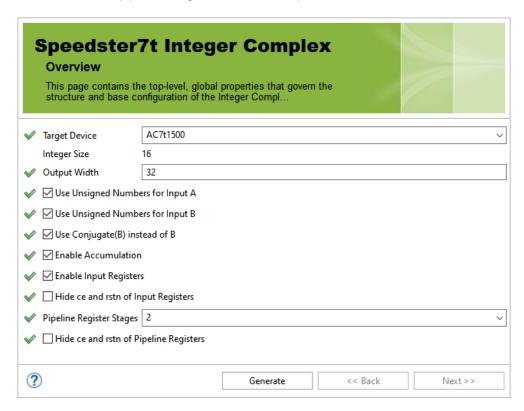

The following example shows the integer complex multiplier configured for 16-bit unsigned inputs with input registers, accumulation and two pipeline stages, and 32-bit output:

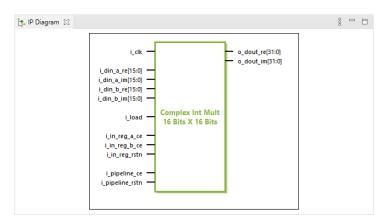

Figure 12: Two Pipeline Stage Integer Multiplier Configuration

The following figure shows the IP diagram for the above configuration:

Figure 13: Two Pipeline Stage Integer Multiplier I/O

# Chapter - 8: Integer Multiplier Soft IP

# Description

The Integer Multiplier soft IP core configures a two-input integer multiplier using either RLB (logic) based multipliers or MLP primitives. The multiplier also supports optional result accumulation. The configurator supports sizes of up to 32 × 32 integers, with both signed and unsigned numerical formats.

# Configuration

The Integer Multiplier soft IP configurator has the following options:

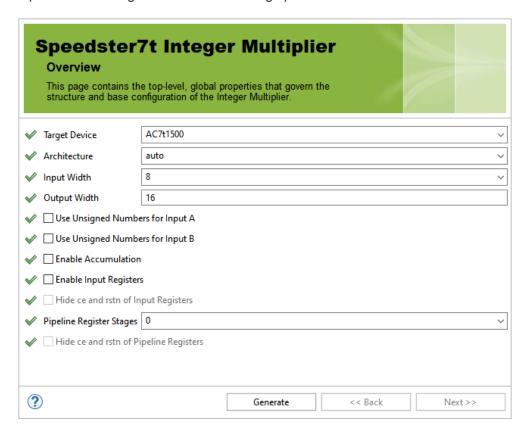

Figure 14: Integer Multiplier Soft IP Configurator

**Table 9: Configuration Options**

| Name                                   | Default  | Range                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------|----------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Device                          | AC7t1500 | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Architecture                           | auto     | auto, rlb,<br>mlp             | Determines which primitives should be used to implement the multiplier.  auto: Allow the tool to choose the most appropriate primitive based on the number formats and sizes selected.  rlb: Implement the multiplier in fabric logic. The Speedster7t FPGA has a unique MLUT structure which supports very efficient multiplier arrays using logic.  mlp: Use the MLP primitive to implement the multiplier.                                                                                                                                                                          |

| Input Width                            | 8        | 3, 4, 5, 6, 7,<br>8, 16 or 32 | Width of both a and b inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Use Unsigned Numbers for Input A/B     | Off      | On, Off                       | When set, configures the appropriate input to use unsigned numbers. By default, the inputs are set to signed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Enable Input Registers                 | Off      | On, Off                       | When set, enables a register stage for both A and B inputs. This stage adds a cycle of latency to all results. Enabling the input registers adds the inputs i_in _reg_a_ce, i_in_reg_b_ce and i_in_reg_rstn to the resultant soft IP.                                                                                                                                                                                                                                                                                                                                                  |

| Hide ce and rstn of Input Registers    | No       | Yes, No                       | If selected, the i_in_reg_a_ce, i_in_reg_b_ce, and i_in_reg_rstn inputs are automatically tied high (1'b1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Enable Accumulator                     | Off      | On, Off                       | The output is the accumulation of the result from each clock cycle. Enabling accumulation adds the input <code>i_load</code> to the resultant soft IP.  The accumulation is cleared when <code>i_load</code> is asserted, the output is reset to <code>i_din_a × i_din_b</code> .  The <code>i_load</code> signal has the same pipeline delay to the accumulator as the <code>i_din_a</code> and <code>i_din_b</code> inputs. Therefore it should be applied on the same cycle as the <code>i_din_a</code> and <code>i_din_b</code> inputs that are to start a new accumulation cycle. |

| Pipeline Register Stages               | 0        | 0, 1, 2, 3                    | Add pipeline register stages through the multiplication process. Enabling pipeline registers improves timing performance at the cost of an additional cycle of latency for each stage enabled.  When any pipeline stages are enabled, the inputs i_pipeline_ce and i_pipeline_rstn are added to the resultant soft IP.                                                                                                                                                                                                                                                                 |

| Hide ce and rstn of Pipeline Registers | No       | Yes, No                       | If selected, the i_pipeline_ce and i_pipeline_rstn inputs are automatically tied high (1'b1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Output Width                           | 16       | 8 to 128                      | Width of the data output. Automatically updated by the configurator when Input Width is updated. In addition, the value can be modified to meet requirements.  The valid range changes dependent upon the Input Width and Architecture. (1)                                                                                                                                                                                                                                                                                                                                            |

1. When accumulation is enabled, it might be necessary to increase the data output width to account for the growth in the result over multiple accumulation cycles. The minimum output width can be calculated as (2 × Input Width) + (number of accumulation cycles).

### Table 10: Ports

| Name                         | Direction | Description                                                                                                                                                               |

|------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i_clk                        | Input     | Clock input, used for the (optional) registers and accumulator.                                                                                                           |

| i_din_a[(Input Width - 1):0] | Input     | 'A' data input to the multiplier.                                                                                                                                         |

| i_din_b[(Input Width - 1):0] | Input     | 'B' data input to the multiplier.                                                                                                                                         |

| i_in_reg_a_ce                | Input     | (Optional) Clock enable for i_din_a. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                     |

| i_in_reg_b_ce                | Input     | (Optional) Clock enable for i_din_b. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                     |

| i_in_reg_rstn                | Input     | (Optional) Synchronous active-low reset for input registers. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                             |

| i_pipeline_ce                | Input     | (Optional) Clock enable for pipeline and accumulator registers. Present when <b>Pipeline Register Stages</b> is greater than 0.                                           |

| i_pipeline_rstn              | Input     | (Optional) Synchronous active-low reset for pipeline and accumulator registers. Present when <b>Pipeline Register Stages</b> is greater than 0.                           |

| i_load <sup>(1)</sup>        | Input     | (Optional) When asserted to 1 'b1, resets the accumulator to i_din_a × i_din_b, ignoring the previous value. Present when <b>Enable Accumulator</b> is set to <b>On</b> . |

| o_dout[(Output Width - 1):0] | Output    | Result of multiplication and accumulation.                                                                                                                                |

### **Table Notes**

1. This signal is internally pipelined to have the same latency as  $i\_din\_a$  and  $i\_din\_b$ .

# Examples

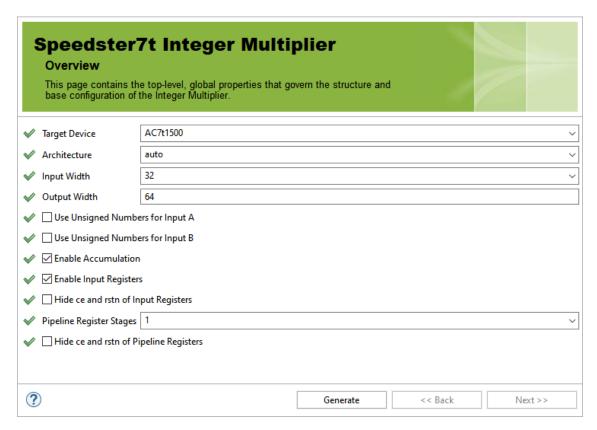

The following example shows the integer multiplier configured for signed 32 × 32 inputs, with accumulation and a single pipeline stage:

Figure 15: 32 × 32 Signed Integer Multiplier Configuration

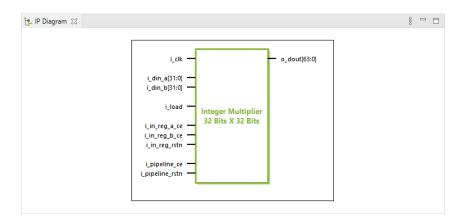

The following figure shows the IP diagram for this configuration:

Figure 16: 32 x 32 Signed Integer Multiplier I/O

# Chapter - 9: Integer Parallel Multiplier Soft IP

### Description

The Integer Parallel Multiplier soft IP core configures multiple integer multipliers. This soft IP core is implemented with the MLP primitive which contains an array of integer multipliers. There can be up to 8 separate multipliers ranging from 3 × 3 to 16 × 16 bits. The multipliers support both signed and unsigned arithmetic.

# Configuration

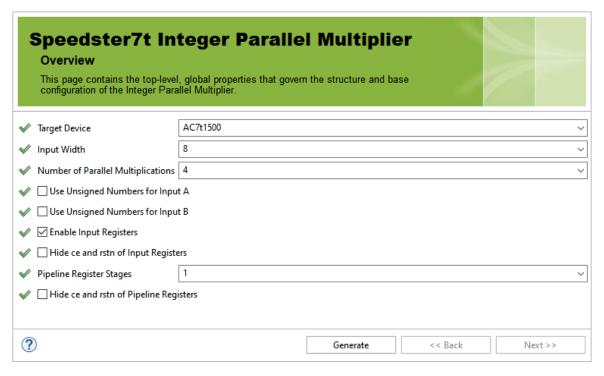

The Integer Parallel Multiplier soft IP configurator has the following options:

Figure 17: Integer Parallel Multiplier Soft IP Configurator

**Table 11: Configuration Options**

| Name                                   | Default  | Range                         | Description                                                                                                                                                                                                                                                                                          |

|----------------------------------------|----------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Device                          | AC7t1500 | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                                                                       |

| Input Width                            | 8        | 3, 4, 5, 6, 7,<br>8 or 16     | Width of the two inputs to each multiplier                                                                                                                                                                                                                                                           |

| Number of Parallel<br>Multiplications  | 4        | 2 to 8                        | The number of parallel multipliers to be implemented. The maximum number of multipliers is determined by the Input Width. Refer to the Number of Multipliers Per Input Width (see page 35) table for details.                                                                                        |

| Use Unsigned Numbers for Input A/B     | Off      | On, Off                       | When set, configures the appropriate inputs to use unsigned numbers. By default, the inputs are set to signed.                                                                                                                                                                                       |

| Enable Input Registers                 | Off      | On, Off                       | When set, enables a register stage for all multiplier inputs. This adds a cycle of latency to all results. Enabling the input registers adds these inputs to the resultant soft IP core:  • i_in_reg_a_ce  • i_in_reg_b_ce  • i_in_reg_rstn                                                          |

| Hide ce and rstn of Input Registers    | No       | Yes, No                       | If selected, the i_in_reg_a_ce, i_in_reg_b_ce, and i_in_reg_rstn inputs are automatically tied high (1'b1).                                                                                                                                                                                          |

| Pipeline Register Stages               | 0        | 0, 1                          | Adds a pipeline register stage to the multiplication process. Enabling pipeline registers improves timing performance at the cost of an additional cycle of latency. When any pipeline stages are enabled, these inputs are added to the resultant soft IP core:  • i_pipeline_ce  • i_pipeline_rstn |

| Hide ce and rstn of Pipeline Registers | No       | Yes, No                       | If selected, the i_pipeline_ce and i_pipeline_rstn inputs are automatically tied high (1'b1).                                                                                                                                                                                                        |

Table 12: Number of Multipliers Per Input Width

| Input Width | Maximum Number of Multipliers |

|-------------|-------------------------------|

| 3           | 8                             |

| 4           | 8                             |

| 5           | 4                             |

| 6           | 4                             |

| 7           | 4                             |

| 8           | 4                             |

| 16          | 2                             |

Table 13: Ports

| Name                         | Direction | Description                                                                                                                                                                                                                                   |

|------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i_clk                        | Input     | Clock input to drive the (optional) registers and accumulator.                                                                                                                                                                                |

| i_din_a[(Input Width - 1):0] | Input     | Packed (see page 36) vector of data to 'A' inputs of multipliers.                                                                                                                                                                             |

| i_din_b[(Input Width - 1):0] | Input     | Packed (see page 36) vector of data to 'B' inputs of multipliers.                                                                                                                                                                             |

| i_in_reg_a_ce                | Input     | (Optional) Clock enable for i_din_a. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                                                                                         |

| i_in_reg_b_ce                | Input     | (Optional) Clock enable for i_din_b. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                                                                                         |

| i_in_reg_rstn                | Input     | (Optional) Synchronous active-low reset for input registers. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                                                                 |

| i_pipeline_ce                | Input     | (Optional) Clock enable for pipeline registers. Present when Pipeline Register Stages is set to 1.                                                                                                                                            |

| i_pipeline_rstn              | Input     | (Optional) Synchronous active-low reset for pipeline registers.  Present when <b>Pipeline Register Stages</b> is set to <b>1</b> .                                                                                                            |

| o_dout[(Output Width – 1):0] | Output    | Output bus consisting of the results from all the multipliers in parallel. Output Width is dynamically calculated by the configurator. See Output Format (see page 36) for details of how the results are assembled in the single output bus. |

### Input Format

Each multiplier input is formed from an array of the individual inputs packed in a single input vector:

```

Code

i_din_a/b(i) = i_din_a/b[i * int_size +: int_size];

```

### **Output Format**

For each multiplier, the result width in bits is equal to 2 × Input Width.

The results from all the parallel multiplications are output as a concatenation on the o\_dout output. The width of this output is calculated as follows:

Output Width = Number of Parallel Multiplications × 2 × Input Width.

The bit lanes used for the result of an individual multiplier are found by multiplying the number of the multiplier (starting at 0) by the result width.

### **Example**

If four 8 × 8 multipliers are configured:

Result Width =  $2 \times 8 = 16$  bits

Output Width =  $4 \times 16 = 64$  bits

Each individual multiplier result appears in the lanes detailed in the following table.

Table 14: Output Bus Organization

| Multiplier Number | Result        |

|-------------------|---------------|

| 0                 | o_dout[15:0]  |

| 1                 | o_dout[31:16] |

| 2                 | o_dout[47:32] |

| 3                 | o_dout[63:48] |

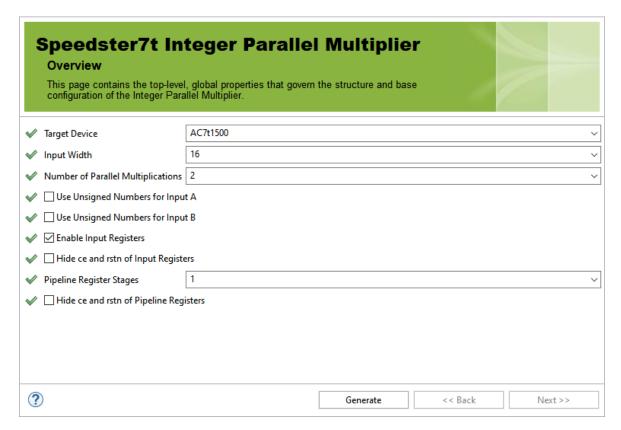

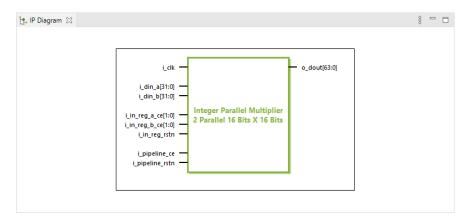

The following example shows the integer parallel multiplier configured for two signed 16 × 16 multiplications, with input registers and and an internal pipeline stage:

Figure 18: Two 16 × 16 Signed Parallel Integer Multiplier Configuration

Figure 19: Two 16 × 16 Signed Parallel Integer Multiplier I/O

## Chapter - 10: Integer Parallel Sum of Products Soft IP

#### Description

The Integer Parallel Sum of Products soft IP core configures multiple parallel integer multipliers with a single summed result. This soft IP core is implemented with the MLP primitive which contains an array of integer multipliers and associated adders. Up to 24 parallel multipliers, ranging from 3 × 3 to 16 × 16 bits can be used. The multipliers support both signed and unsigned arithmetic. The final output can optionally be accumulated.

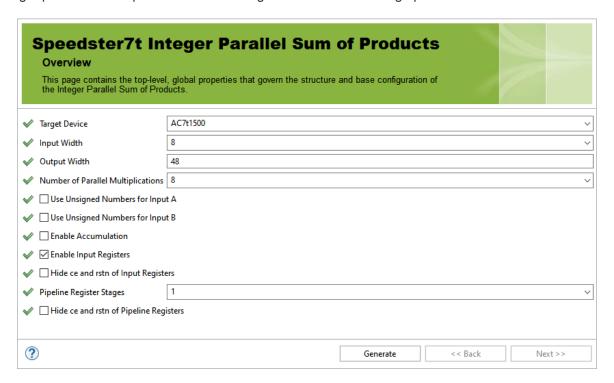

#### Configuration

The integer parallel sum of products soft IP configurator has the following options:

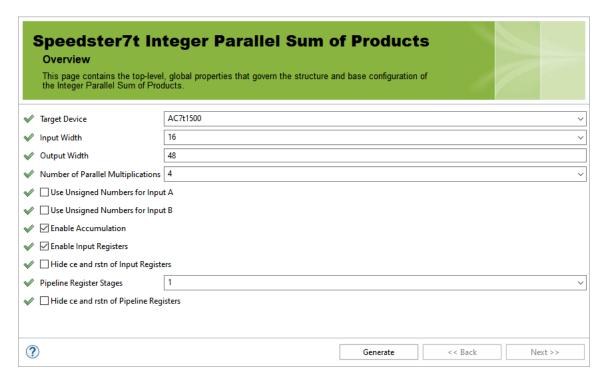

Figure 20: Integer Parallel Sum of Products Configurator

**Table 15: Configuration Options**

| Name                                   | Default  | Range                         | Description                                                                                                                                                                                                                                                                                                         |

|----------------------------------------|----------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Device                          | AC7t1500 | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                                                                                      |

| Input Width                            | 8        | 3, 4, 5, 6, 7,<br>8 or 16     | Width of the two inputs to each multiplier.                                                                                                                                                                                                                                                                         |

| Number of Parallel<br>Multiplications  | 8        | 1 to 24                       | The number of parallel multipliers to be implemented and their results summed. The maximum number of multipliers is determined by the Input Width. Refer to the Maximum Number of Multipliers Per Input Width table for details.                                                                                    |

| Use Unsigned Numbers for Input A/B     | Off      | On, Off                       | When set, configures the appropriate inputs to use unsigned numbers. The inputs are signed by default.                                                                                                                                                                                                              |

| Enable Input Registers                 | Off      | On, Off                       | When set, enables a register stage for all multiplier inputs. This adds a cycle of latency to all results. Enabling the input registers adds these inputs to the resultant soft IP core:  • i_in_reg_a_ce  • i_in_reg_b_ce  • i_in_reg_rstn                                                                         |

| Hide ce and rstn of Input<br>Registers | No       | Yes, No                       | If selected, the i_in_reg_a_ce, i_in_reg_b_ce, and i_in_reg_rstn inputs are automatically tied high (1'b1).                                                                                                                                                                                                         |

| Enable Accumulator                     | Off      | On, Off                       | The output is the accumulation of the result from each clock cycle. Enabling accumulation adds the input i_load to the resultant soft IP core. The accumulation is cleared when i_load is asserted.                                                                                                                 |

| Pipeline Register Stages               | 0        | 0, 1 or 2                     | Adds pipeline register stages to the multiplication process. Enabling pipeline register stages improves timing performance at the cost of an additional cycle of latency per stage. When any pipeline stages are enabled, these inputs are added to the resultant soft IP core:  • i_pipeline_ce  • i_pipeline_rstn |

| Hide ce and rstn of Pipeline Registers | No       | Yes, No                       | If selected, the i_pipeline_ce and i_pipeline_rstn inputs are automatically tied high (1'b1).                                                                                                                                                                                                                       |

| Output Width <sup>(1)</sup>            | 48       | 3 to 48                       | Width of the data output. By default, this value is set to 48 bits. This value can be reduced if required.                                                                                                                                                                                                          |

1. Ensure that **Output Width** is sufficient to represent the maximum result that can be accumulated. In the event of overflow, the higher order bits of any result are truncated.

When accumulation is enabled, it might be necessary to increase the data output width to account for the growth in the result over multiple accumulation cycles. The minimum output width can be calculated as:

(2 × Input Width × Number of Parallel Multiplications) + (number of accumulation cycles)

Table 16: Maximum Number of Multipliers Per Input Width

| Input Width | Maximum Number of Multipliers |

|-------------|-------------------------------|

| 3           | 24                            |

| 4           | 16                            |

| 5           | 12                            |

| 6           | 12                            |

| 7           | 10                            |

| 8           | 8                             |

| 16          | 4                             |

Table 17: Ports

| Name                         | Direction | Description                                                                                                                                                       |

|------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i_clk                        | Input     | Clock input, used for the (optional) registers and accumulator.                                                                                                   |

| i_din_a[(data width - 1):0]  | Input     | Packed (see page 41) data vector to the 'A' inputs of the multipliers where data width = Input Width × Number of Parallel Multiplications.                        |

| i_din_b[(data width - 1):0]  | Input     | Packed (see page 41) data vector to the 'B' inputs of the multipliers where data width = Input Width × Number of Parallel Multiplications.                        |

| i_in_reg_a_ce                | Input     | (Optional) Clock enable for i_din_a. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                             |

| i_in_reg_b_ce                | Input     | (Optional) Clock enable for i_din_b. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                             |

| i_in_reg_rstn                | Input     | (Optional) Synchronous active-low reset for input registers. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                     |

| i_pipeline_ce                | Input     | (Optional) Clock enable for pipeline registers. Present when <b>Pipeline Register Stages</b> is greater than 0.                                                   |

| i_pipeline_rstn              | Input     | (Optional) Synchronous active-low reset for pipeline registers.  Present when <b>Pipeline Register Stages</b> is greater than 0.                                  |

| i_load <sup>(1)</sup>        | Input     | (Optional) When asserted to 1 'b1, resets the accumulator to i_din_a × i_din_b, ignoring the previous value. Present when <b>Enable Accumulator</b> is set to On. |

| o_dout[(Output Width – 1):0] | Output    | Output bus consisting of the sum of products from all of the multipliers in parallel.                                                                             |

1. This signal is internally pipelined to have the same latency as i\_din\_a and i\_din\_b.

## Input Format

Each multiplier input is formed from an array of the individual inputs, packed in a single input vector.

```

i_din_a / b(i) = i_din_a / b[i*int_size +: int_size];

```

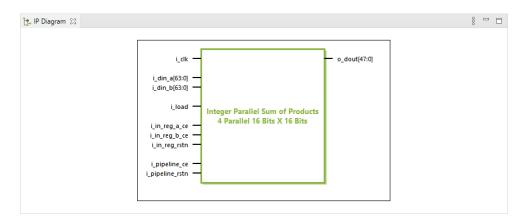

The following example shows the integer parallel sum of products configured for four signed 16 × 16 multiplications with input registers, accumulation and a single internal pipeline stage.

Figure 21: Four 16 × 16 Signed Multiplier Sum of Products Configuration

Figure 22: Four 16 × 16 Signed Multiplier Sum of Products I/O

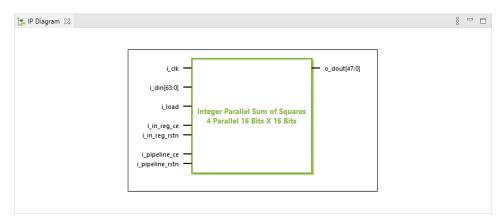

## Chapter - 11: Integer Parallel Sum of Squares Soft IP

#### Description

The Integer Parallel Sum of Squares soft IP core configures multiple parallel integer square ( $n^2$ ) multipliers with a single summed result. This soft IP core is implemented with the MLP primitive which contains an array of integer multipliers and associated adders. Up to 32 parallel multipliers, ranging from 3 × 3 to 16 × 16 bits can be configured. The multipliers support both signed and unsigned arithmetic. The final output can optionally be accumulated.

### Configuration

The integer parallel sum of squares soft IP configurator has the following options:

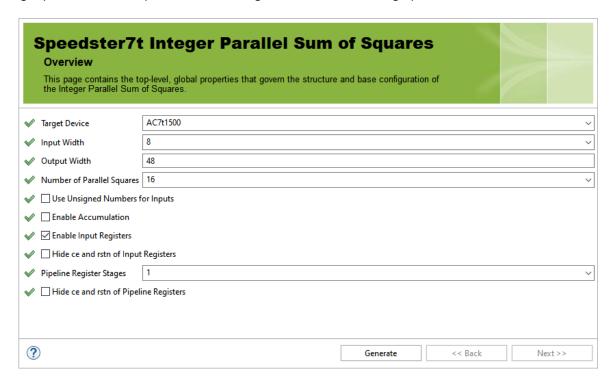

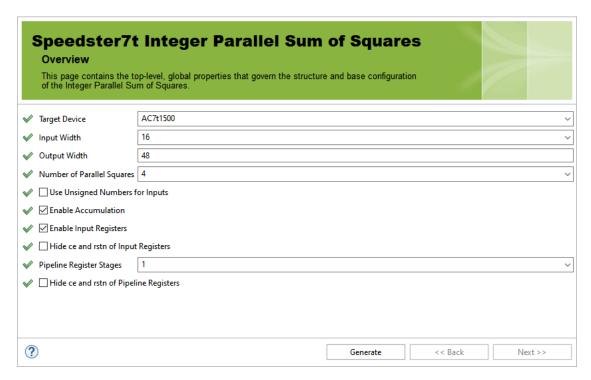

Figure 23: Integer Parallel Sum of Squares Configurator

**Table 18: Configuration Options**

| Name                                   | Default  | Range                         | Description                                                                                                                                                                                                                                                                                                         |

|----------------------------------------|----------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Device                          | AC7t1500 | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                                                                                      |

| Input Width                            | 8        | 3, 4, 5, 6, 7,<br>8 or 16     | Width of the input to be squared.                                                                                                                                                                                                                                                                                   |

| Number of Parallel<br>Squares          | 8        | 1 to 32                       | The number of parallel squaring multipliers to be implemented and their results summed. The maximum number of multipliers is determined by the Input Width. Refer to the Maximum Number of Multipliers Per Input Width table, for details.                                                                          |

| Use Unsigned Numbers for Input         | Off      | On, Off                       | When set, configures the input to use unsigned numbers. The input is signed by default.                                                                                                                                                                                                                             |

| Enable Input Registers                 | Off      | On, Off                       | When set, enables a register stage for the input. Adds a cycle of latency to all results. Enabling the input registers adds these inputs to the resultant soft IP core:  • i_in_reg_ce • i_in_reg_rstn                                                                                                              |

| Hide ce and rstn of Input Registers    | No       | Yes, No                       | If selected, the i_in_reg_ce and i_in_reg_rstn inputs are automatically tied high (1 'b1).                                                                                                                                                                                                                          |

| Enable Accumulator                     | Off      | On, Off                       | Output is the accumulation of the result from each clock cycle. Enabling accumulation adds these inputs to the resultant soft IP core:  • i_load  • i_pipeline_ce  • i_pipeline_rstn  The accumulation is cleared when i_load is asserted.                                                                          |

| Pipeline Register Stages               | 0        | 0, 1 or 2                     | Adds pipeline register stages to the multiplication process. Enabling pipeline register stages improves timing performance at the cost of an additional cycle of latency per stage. When any pipeline stages are enabled, these inputs are added to the resultant soft IP core:  • i_pipeline_ce  • i_pipeline_rstn |

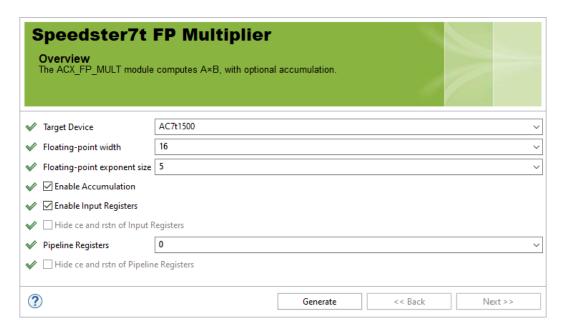

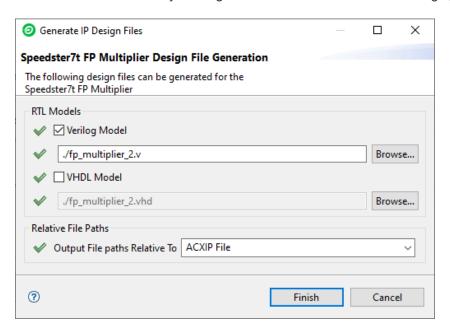

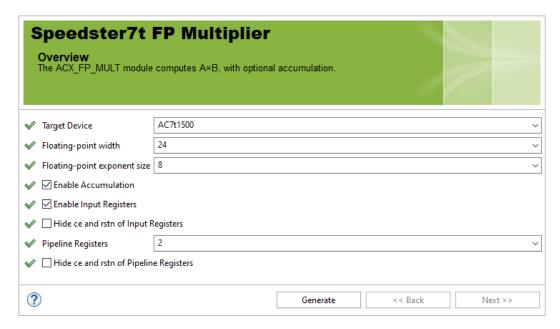

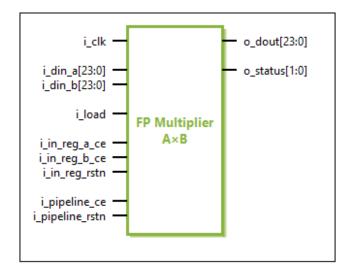

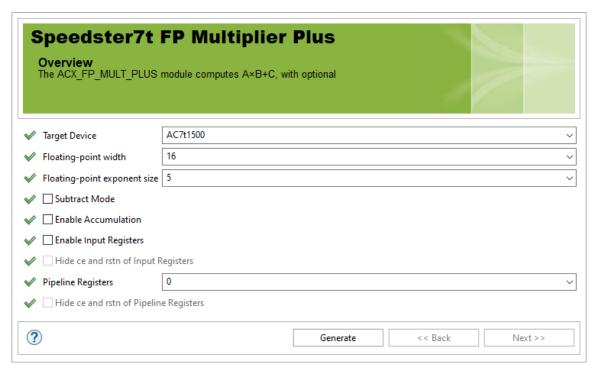

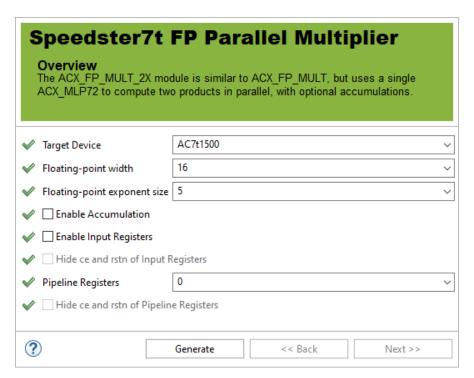

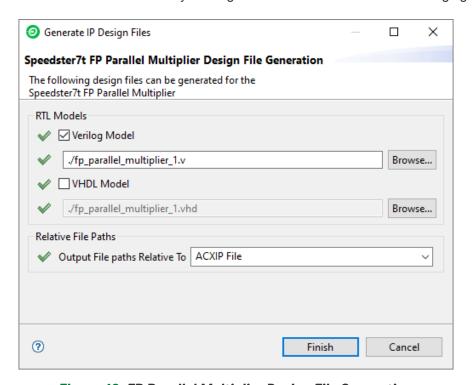

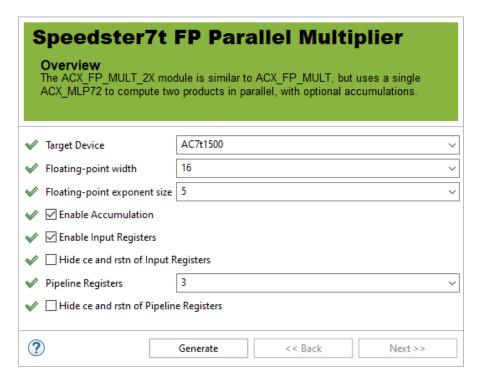

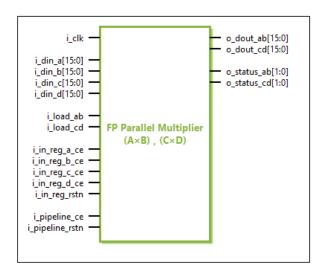

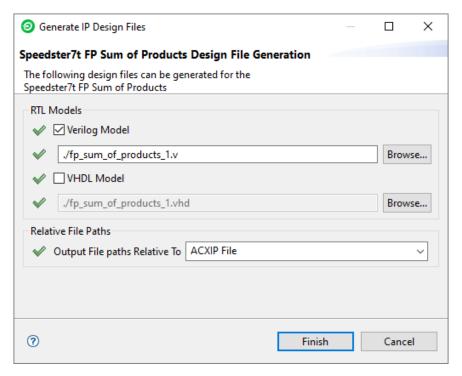

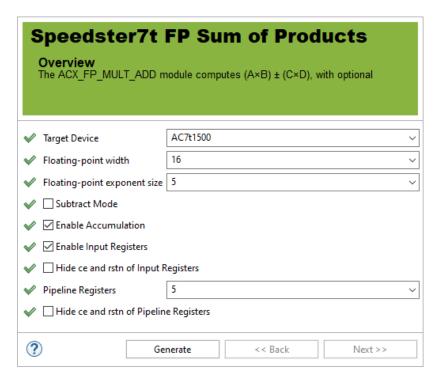

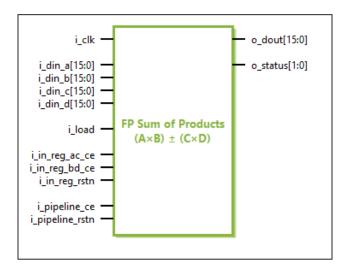

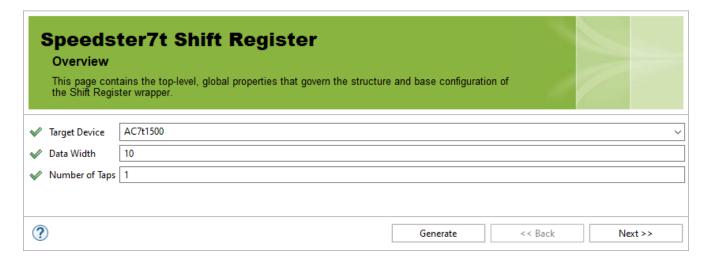

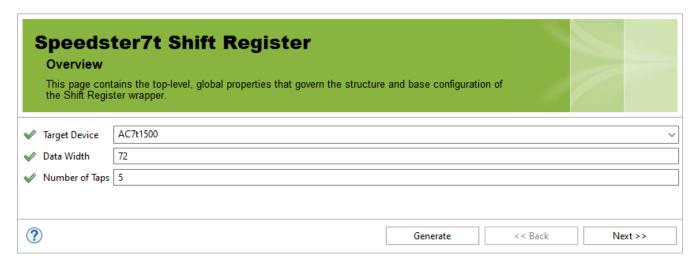

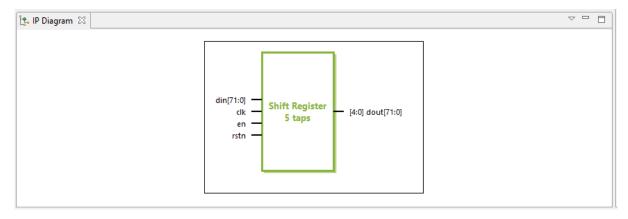

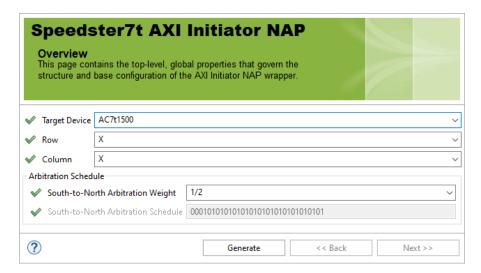

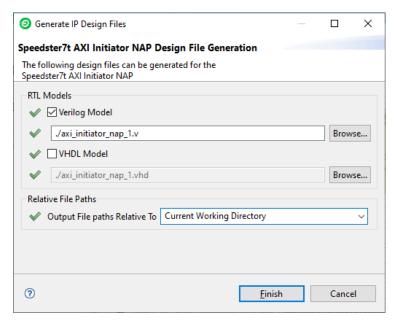

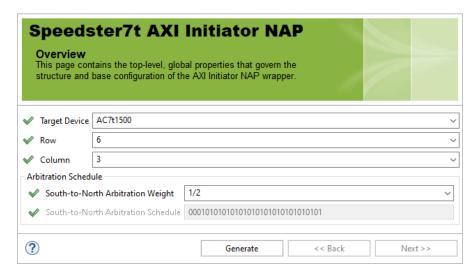

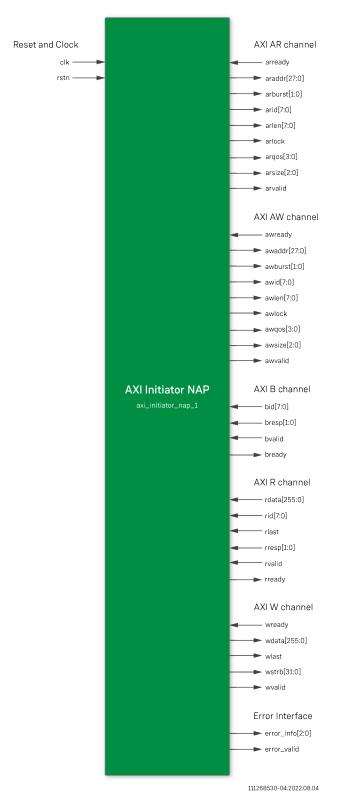

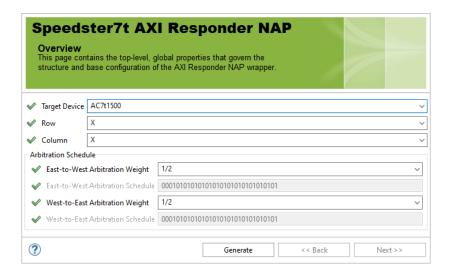

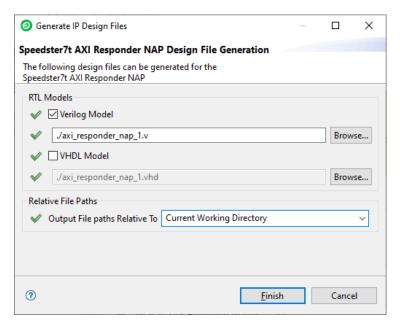

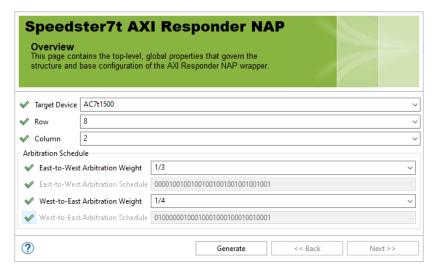

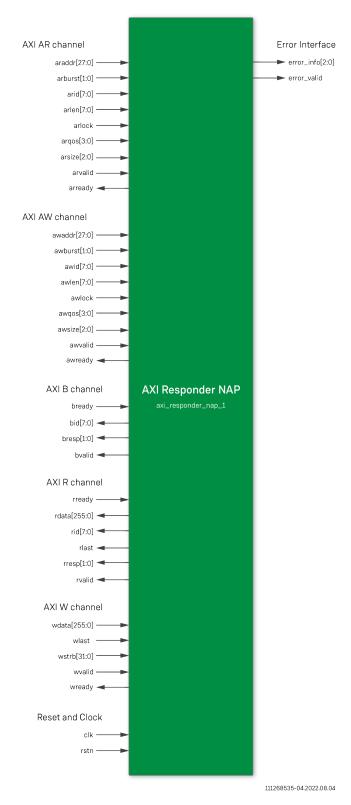

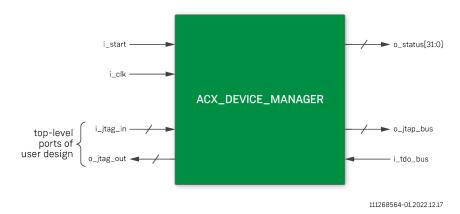

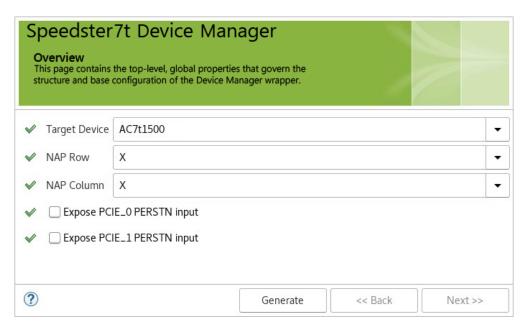

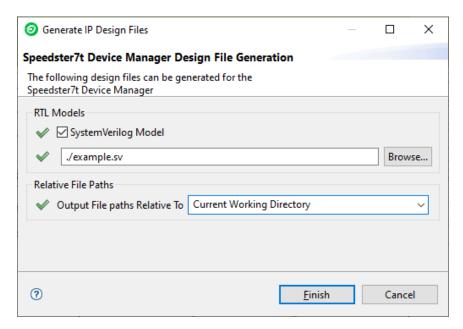

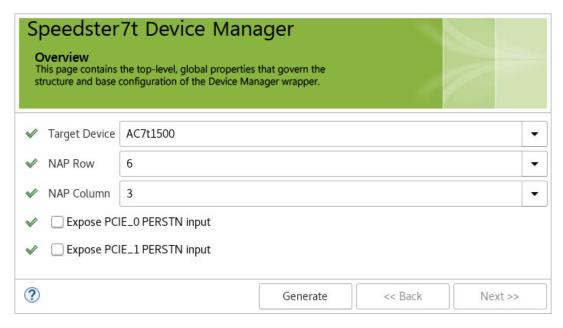

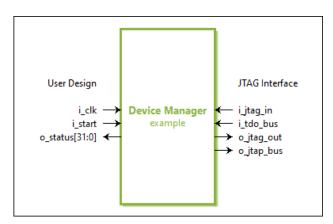

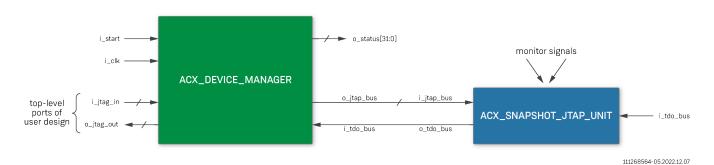

| Hide ce and rstn of Pipeline Registers | No       | Yes, No                       | If selected, the i_pipeline_ce and i_pipeline_rstn inputs are automatically tied high (1'b1).                                                                                                                                                                                                                       |