# Speedster7t Soft IP User Guide (UG103)

**Speedster FPGAs**

**Preliminary Data**

# Copyrights, Trademarks and Disclaimers

Copyright © 2021 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedcore, Speedster, and ACE are trademarks of Achronix Semiconductor Corporation in the U.S. and/or other countries All other trademarks are the property of their respective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

#### **Preliminary Data**

This document contains preliminary information and is subject to change without notice. Information provided herein is based on internal engineering specifications and/or initial characterization data.

#### **Achronix Semiconductor Corporation**

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail: info@achronix.com

# Table of Contents

| Chapter - 1: Introduction               | 6  |

|-----------------------------------------|----|

| Chapter - 2: Instructions               | 7  |

| IO Ring and Core                        | 7  |

| IO Ring                                 |    |

| Core                                    | 8  |

| Chapter - 3: Available Configurators    | 9  |

| Memories                                | 9  |

| MLPs                                    | 9  |

| Logic                                   | 9  |

| Chapter - 4: BRAM72K Soft IP            | 10 |

| Description                             | 10 |

| Configuration                           |    |

| Write and Read Depth                    | 14 |

| Examples                                |    |

| Chapter - 5: LRAM Soft IP               | 17 |

| Description                             |    |

| Configuration                           | 18 |

| Write and Read Depth                    | 20 |

| Examples                                | 22 |

| Chapter - 6: ROM Soft IP                | 24 |

| Description                             |    |

| Configuration                           |    |

| Examples                                | 29 |

| Chapter - 7: Integer Multiplier Soft IP | 31 |

| Description                             |    |

| Configuration                           | 32 |

|                                         |    |

| Examples                                              | 35 |

|-------------------------------------------------------|----|

| Chapter - 8: Integer Parallel Multiplier Soft IP      |    |

| ·                                                     |    |

| Configuration                                         |    |

| Output Format                                         |    |

| Examples                                              |    |

| Chapter - 9: Integer Parallel Sum of Products Soft IP | 44 |

| Description                                           | 44 |

| Configuration                                         | 45 |

| Input Format                                          | 48 |

| Examples                                              | 49 |

| Chapter - 10: Integer Parallel Sum of Squares Soft IP | 50 |

| Description                                           | 50 |

| Configuration                                         | 51 |

| Input Packing                                         | 54 |

| Examples                                              | 55 |

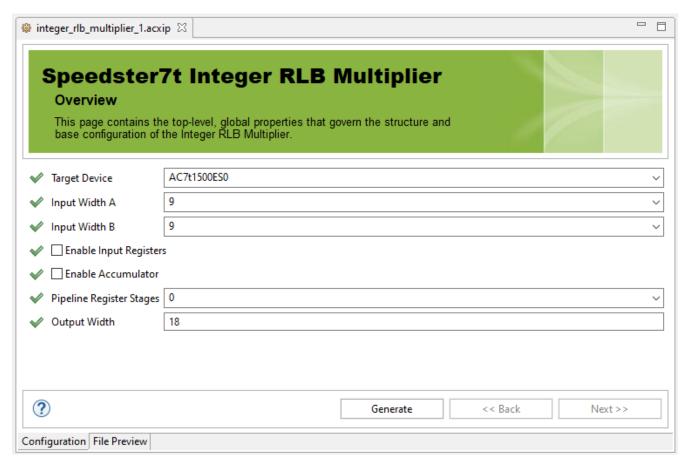

| Chapter - 11: Integer RLB Multiplier Soft IP          | 56 |

| Description                                           | 56 |

| Configuration                                         | 57 |

| Examples                                              | 60 |

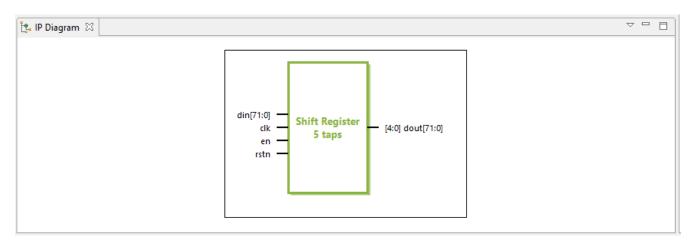

| Chapter - 12: Shift Register Soft IP                  | 62 |

| Description                                           | 62 |

| Configuration                                         | 63 |

| Examples                                              | 65 |

| Revision History                                      |    |

# Chapter - 1: Introduction

There are a number of available soft IP cores for the Speedster®7t family of devices. Each of these cores has an IP configurator within ACE that allows configuration of the soft IP core to the user's specifications. When configured, the generated wrapper for the core can be instantiated within a user project enabling both synthesis and simulation of the design.

This document describes the available soft IP cores and the methods for configuration and instantiation of each. Soft IP cores are primarily implemented using the components present in the FPGA programmable fabric. For details of these components, see the *Speedster7t IP Component Library User Guide* (UG086).

## Chapter - 2: Instructions

Within ACE, all IP cores are accessed using the IP perspective (see the "Perspectives" chapter in the *ACE User Guide* (UG070). The flow and method for generating user IP cores is fully detailed in the "Creating an IP Configuration" chapter in the ACE User Guide. Unless directed otherwise below, use the instructions in the ACE User Guide.

## 10 Ring and Core

Within the Speedster7t device there are two categories of IP core. These are listed within the IP Libraries pane as **IO Ring** and **Core**. For the Speedster7t family of devices, the following soft IP cores are available:

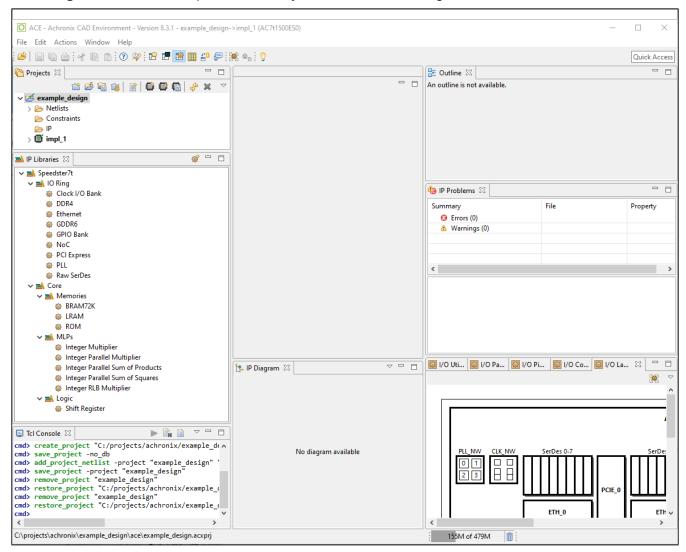

Figure 1: Speedster7t IP Libraries View

## IO Ring

The IO Ring contains the configuration for each of the IP cores located in the IO ring of the device such as the Clock Banks, PLLs, GDDR, DDR, GPIO, PCIe, NoC, SerDes and Ethernet. The configuration of each of these IP cores is detailed in its respective User Guide.

### Core

The **Core** view contains the available IP configurators for the selected target device used in the project. For the Speedster7t devices, the soft cores shown above (see page 7), and listed below (see page 9) are available. The details of how to configure each of these cores are given on the appropriate page.

# Chapter - 3: Available Configurators

## **Memories**

- BRAM72K Soft IP (see page 10) For creating large block RAM memory arrays

- LRAM Soft IP (see page 17) For creating large logic RAM memory arrays

- ROM Soft IP (see page 24) For creating ROMs constructed of either block RAM or logic RAM

## **MLPs**

- Integer Multiplier Soft IP (see page 31) For creating a single multiplier of up to 32 × 32

- Integer Parallel Multiplier Soft IP (see page 37) For creating parallel multipliers of up to 32 × 32

- Integer Parallel Sum of Products Soft IP (see page 44) For integer sum of products from up to 24 multipliers

- Integer Parallel Sum of Squares Soft IP (see page 50) For integer sum of squared inputs

- Integer RLB Multiplier Soft IP (see page 56) For creating a single multiplier using RLBs in the fabric logic

## Logic

Speedster7t Shift Register Soft IP (see page 62) - For creating DFF-based shift registers

# Chapter - 4: BRAM72K Soft IP

## Description

The Speedster7t BRAM72K soft IP core creates an arbitrary sized memory array, comprised of ACX\_BRAM72K primitives. The macro employs the embedded data and address cascade paths between ACX\_BRAM72K primitives enabling fast connections for both address and data paths.

If only a single ACX\_BRAM72K is required, this primitive can be inferred or instantiated in the code directly. However, if a memory array comprising multiple BRAM72K blocks is required, it is recommended to use the soft IP configuration to enable the optimum architecture.

## Configuration

The user macro has the following configuration options:

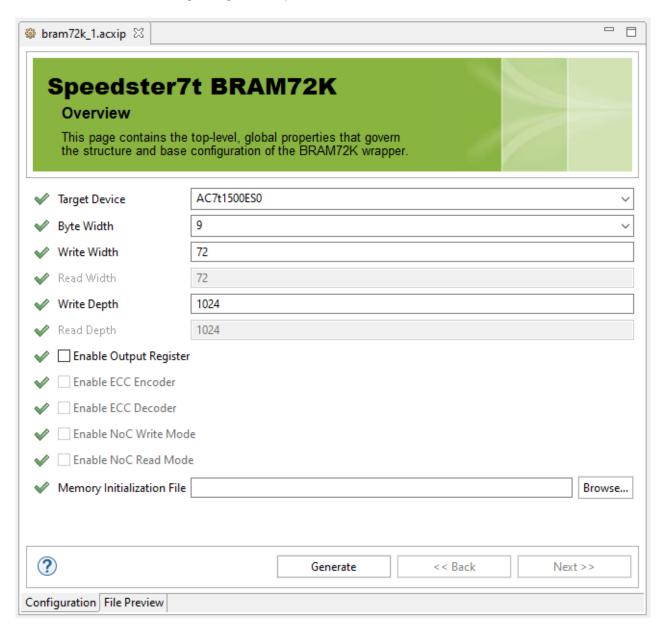

Figure 2: BRAM72K Soft IP Configuration

**Table 1: Configuration Options**

| Name                         | Default     | Range                         | Description                                                                                                                                                                                                                                          |

|------------------------------|-------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target<br>Device             | AC7t1500ES0 | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                       |

| Byte Width                   | 9           | 8, 9                          | Determines whether fields should be set to 8-bit or 9-bit.                                                                                                                                                                                           |

| Write Width                  | 72          | 1 to 9216                     | Write port data width. Values greater than 144 limit the write depth to 16K words.                                                                                                                                                                   |

| Read<br>Width                | 72          | 1 to 9216                     | Read port data width. Currently set to match the write width. This value cannot be changed by the user. Future releases of this user macro will allow the user to configure different write and read widths.                                         |

| Write<br>Depth               | 1024        | 512 to<br>1048576             | Write port address depth. The maximum value is limited by the number of BRAM72K blocks in a column in the target device. The maximum value is also dependant on the write width as detailed in Write and Read Depths versus Data Width (see page 14) |

| Read<br>Depth                | 1024        | 512 to<br>1048576             | Read port address depth. Currently set to match the write depth. This value cannot be changed by the user. Future releases of this user macro will allow the user to configure different write and read depths.                                      |

| Enable<br>Output<br>Register | Off         | On, Off                       | Determines whether the output register in each of the BRAM72K primitives is enabled. Adds an additional cycle of latency to any read operation.                                                                                                      |

| Enable<br>ECC<br>Encoder     | Off         | On, Off                       | Determines whether the ECC encoder is enabled for writes to the memory array. This option is currently disabled and cannot be set by the user.                                                                                                       |

| Enable<br>ECC<br>Decoder     | Off         | On, Off                       | Determines whether the ECC encoder is enabled for reads from the memory array. This option is currently disabled and cannot be set by the user.                                                                                                      |

| Enable<br>NoC Write<br>Mode  | Off         | On, Off                       | Determines whether the BRAM can be written directly from the NoC. This option is currently disabled and cannot be set by the user.                                                                                                                   |

| Enable<br>NoC Read<br>Mode   | Off         | On, Off                       | Determines whether the BRAM can be read directly from the NoC. This option is currently disabled and cannot be set by the user.                                                                                                                      |

| Name                                    | Default | Range                                                                                                                                                                                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Use<br>Memory<br>Initialization<br>File | Off     | On, Off                                                                                                                                                                                                                                                                                                                                     | Determines whether a memory initialization file is used to initialize the memory contents. This initialization occurs for both synthesis and simulation.  When this option is enabled, entry of the file location in the associated file browser dialog is permitted.  Note  If relative paths are used for the memory initialization file location, the same relative paths must be valid from both the ACE project directory and the simulation directory. It is recommended to locate both of these directories at the same relative depth in the project tree, and to use relative paths that navigate up the tree to the first common directory, before descending the tree to the location of the files.  For example: The Achronix reference designs locate the ACE project in <pre>project root&gt;/src/ace</pre> . The simulation directories are located in <pre>project root&gt;/sim/ycs Of</pre> <pre><pre>project root&gt;/sim/questa</pre>. The memory initialization files are located in <pre>project root&gt;/src/mem_init_files</pre>. A relative path correct for both simulation and ACE is "//src/mem_init_files/filename.txt"</pre> |

|                                         |         | project in <pre> project root&gt;/src/ace. The simulation directories are located in <pre> project root&gt;/sim/vcs or <pre> project root&gt;/sim/questa. The memory initialization files are located in <pre> project root&gt;/src/mem_init_files. A  relative path correct for both simulation and ACE is "//src </pre></pre></pre></pre> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Write and Read Depth

#### **Absolute Limits**

The write and read depths are related to the write and read widths. The absolute limit on these values is detailed in the table below:

Table 2: Write and Read Depths Versus Data Width

| Memory Width | Maximum Memory Depth |

|--------------|----------------------|

| 1 to 144     | 1048576              |

| 145 to 9216  | 16384                |

## **Device Specific Limits**

Within a device, the largest memory that can be generated is limited by the number of ACX\_BRAM72K primitives in a column. For example, if there are 64 ACX\_BRAM72K primitives in a column, then the maximum memory size is  $64 \times 72$ K bits = 4,718,592 bits. This would support a configuration of 72-bits  $\times 64$ K depth, or 36-bits  $\times 128$ K depth.

## Examples

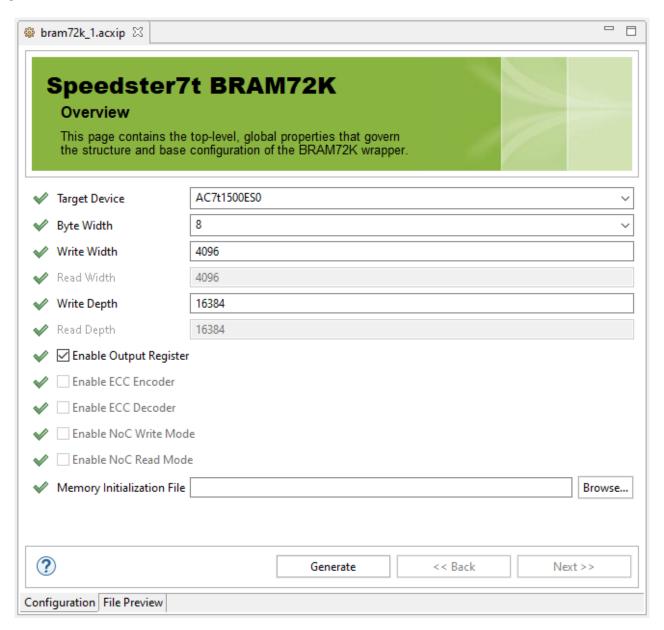

The following figure shows the macro configured for a 4096-bit by 16,384 entry memory with the memory output register enabled:

Figure 3: 4096 × 16K Memory Configuration

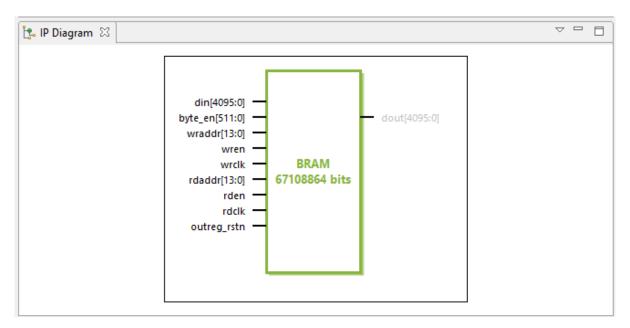

The following figure shows the IP diagram for the above configuration:

Figure 4: 4096 × 16K Memory IP Diagram

# Chapter - 5: LRAM Soft IP

## Description

The LRAM soft IP core creates an arbitrary sized memory array comprised of LRAM primitives.

If only a single LRAM is required, this primitive can be inferred or instantiated into the code directly. However, if a memory array consisting of multiple LRAM primitives is required, it is recommended to use the soft IP configurator to achieve the optimum architecture.

## Utilization

#### Note

Within the Speedster7t family, the LRAM and MLP primitives share a site. Therefore if a site is allocated for use to an LRAM primitive, the MLP on that same site cannot be used.

## Configuration

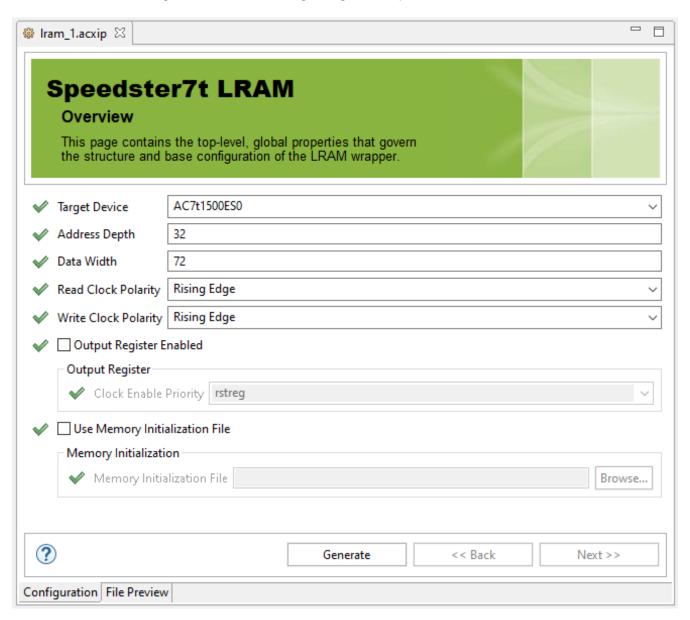

The LRAM2K soft IP configurator has the following configuration options:

Figure 5: LRAM Soft IP Configurator

**Table 3: Configuration Options**

| Name                                              | Default     | Range                                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                 |  |

|---------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Target<br>Device                                  | AC7t1500ES0 | All<br>Speedster7t<br>devices                                                                                                                                                         | Set to match the target device of the project.                                                                                                                                                                                                                                              |  |

| Address<br>Depth                                  | 32          | Address depth of the memory array in words. The depth imposes limitations on the maximum data width. The limits are detailed in Re and Write Depths Versus Data Widths (see page 20). |                                                                                                                                                                                                                                                                                             |  |

| Data Width                                        | 72          | 1 to 184320                                                                                                                                                                           | Data port width in bits of both din and dout.                                                                                                                                                                                                                                               |  |

| Read Clock<br>Polarity                            | Rising Edge | Falling or<br>Rising Edge                                                                                                                                                             | The rdclk active edge on which all read transactions will occur.                                                                                                                                                                                                                            |  |

| Write Clock<br>Polarity                           | Rising Edge | Falling or<br>Rising Edge                                                                                                                                                             | The wrclk active edge on which all write transactions will occur.                                                                                                                                                                                                                           |  |

| Output<br>Register<br>Enabled                     | Off         | On, Off                                                                                                                                                                               | Determines whether the output register in each of the LRAM primitive is enabled. This adds an additional cycle of latency to any read operation. If the output register is disabled, the memory array is combinatorial. The output changes when the input address changes                   |  |

| Output<br>Register<br>Clock<br>Enable<br>Priority | rstreg      | rstreg, rstce                                                                                                                                                                         | <ul> <li>rstreg: The outregce input is ignored when rstregn = 1'b0.         The output register is reset on the next active rdclk edge.     </li> <li>rstce:outregce must be equal to 1'b1 and rstregn = 1'b0 for the output register to be reset on the next active rdclk edge.</li> </ul> |  |

| Name                                    | Default | Range   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Use<br>Memory<br>Initialization<br>File | Off     | On, Off | Determines whether a memory initialization file is used to initialize the memory contents. This initialization occurs for both synthesis and simulation.  When this option is enabled, entry of the file location in the associated file browser dialog is permitted.  Note  If relative paths are used for the memory initialization file location, the same relative paths must be valid from both the ACE project directory and the simulation directory. It is recommended to locate both these directories at the same relative depth in the project tree, and to use relative paths that navigate up the tree to the first common directory, before descending the tree to the location of the files.  For example, the Achronix reference designs locate the ACE project in <pre>project root&gt;/src/ace</pre> . The simulation directories are located in <pre>project root&gt;/sim/ycs or</pre> <pre><pre>project root&gt;/sim/questa</pre>. The memory initialization files are located in <pre>project root&gt;/src/mem_init_files</pre>. A relative path correct for both simulation and ACE is "//src/mem_init_files/filename.txt".</pre> |

| Initialization                          |         |         | the files.  For example, the Achronix reference designs locate the ACE project in <pre>project root&gt;/src/ace</pre> . The simulation directories are located in <pre>project root&gt;/sim/vcs</pre> or <pre><pre>project root&gt;/sim/questa</pre>. The memory initialization files are located in <pre>project root&gt;/src/mem_init_files</pre>. A relative path correct for both simulation and ACE is "//src</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## Write and Read Depth

#### **Absolute Limits**

The write and read depths are related to the write and read widths. The absolute limit on these values is detailed in the table below:

Table 4: Write and Read Depths versus Data Width

| Memory Width | Maximum Memory Depth |

|--------------|----------------------|

| 4 to 32      | 184320               |

| 33 to 64     | 92160                |

| 65 to 96     | 61416                |

| 97 to 128    | 46080                |

| 129 to 144   | 36864                |

#### **Device Specific Limits**

Within a device, the largest memory that can be generated is limited by the number of ACX\_LRAM primitives in a column. For example, if there are 64 ACX\_LRAM2K primitives in a column, the maximum memory size is 64 × 2K bits = 131,027 bits. This would support a configuration of 64-bits x 2K depth, or 32-bits × 4K depth.

Alternatively, if there are 64 ACX\_LRAM4K in a column, the maximum memory size is 64 × 4K bits = 262,144 bits. This would support a configuration of 64-bits × 4K depth, or 32-bits × 8K depth.

The type of LRAM used by the Speedster7t LRAM configurator is dependent upon the device chosen and the available LRAM types within the fabric.

## Examples

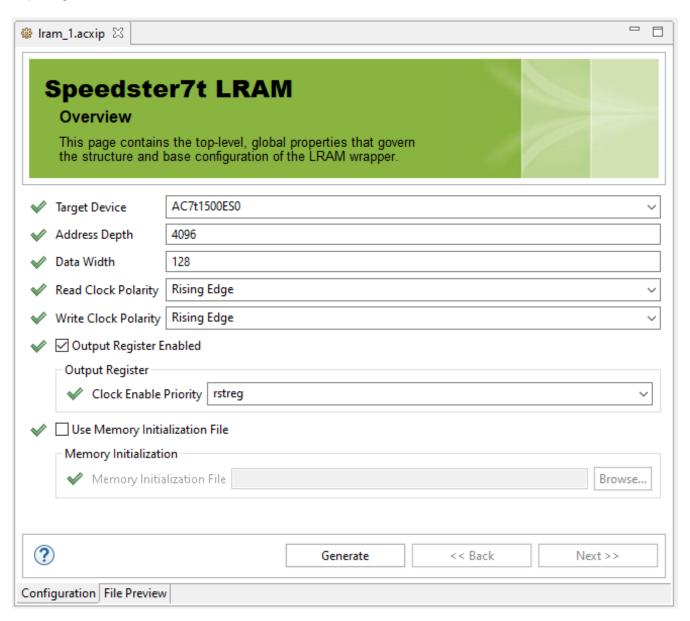

The following figure shows the soft IP configured for a 128-bit × 4096-word LRAM memory with the memory output register enabled:

Figure 6: 128-Bit x 4096-Word LRAM Memory Configuration

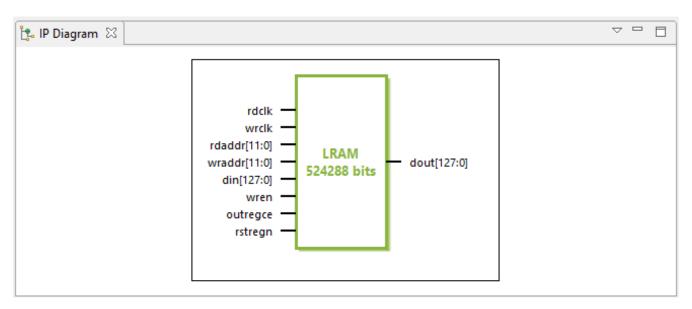

The following figure shows the IP diagram for the above configuration:

Figure 7: 128-Bit x 4096-Word LRAM Memory IP Diagram

# Chapter - 6: ROM Soft IP

## Description

The Speedster7t ROM soft IP core creates an arbitrary sized ROM, using either BRAM or LRAM primitives.

## Utilization

#### Note

Within the Speedster7t family, the LRAM and MLP primitives share a site. Therefore, if using a Speedster7t device, and if the ROM soft IP configuration selects an LRAM to implement the ROM, the MLPs on the sites used by the ROM cannot be used.

# Configuration

The soft IP has the following configuration options:

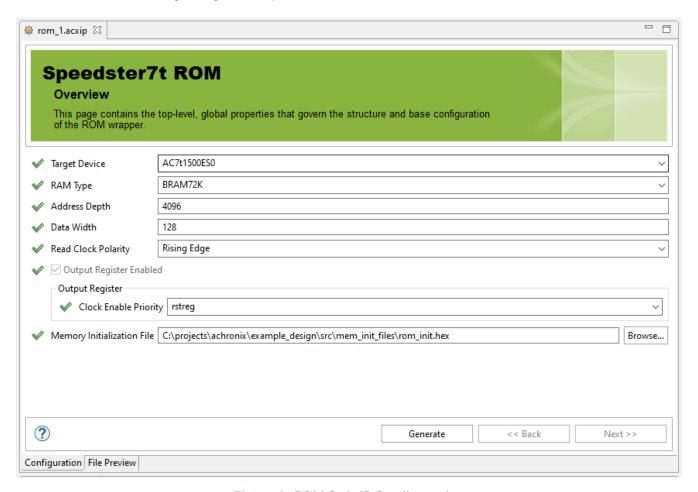

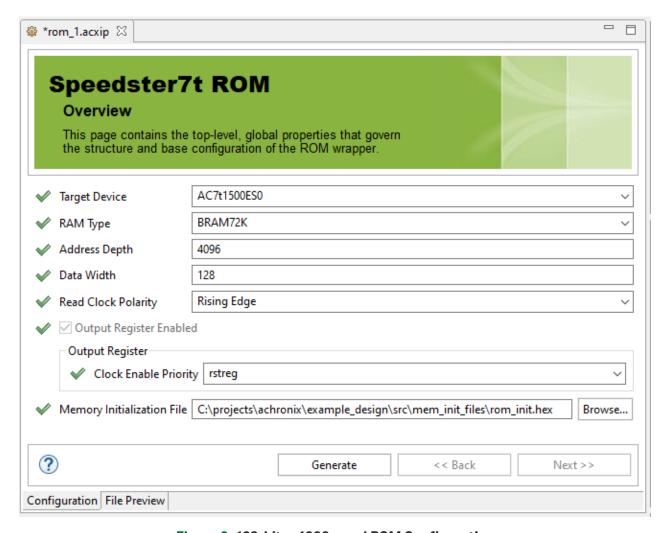

Figure 8: ROM Soft IP Configuration

**Table 5: Configuration Options**

| Name                                              | Default     | Range                         | Description                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------|-------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target<br>Device                                  | AC7t1500ES0 | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                                                               |

| RAM Type                                          | BRAM72K     | BRAM72K,<br>LRAM2K            | Determines which type of RAM primitives used to form the ROM.                                                                                                                                                                                                                                |

| Address<br>Depth                                  | 1024        | 4 to 16384                    | Address depth of the ROM in words.                                                                                                                                                                                                                                                           |

| Data Width                                        | 20          | 1 to 184320                   | Port width in bits of the dout port. The width selected affects the available address depth. The maximum values of width versus depth are detailed in Read and Write Depths Versus Data Widths (see page 28).                                                                                |

| Read Clock<br>Polarity                            | Rising Edge | Falling or<br>Rising Edge     | The rdclk active edge on which all read transactions will occur.                                                                                                                                                                                                                             |

| Enable<br>Output<br>Register                      | Off         | On, Off                       | Determines whether the output register in each of the LRAM2K primitives is enabled. Adds an additional cycle of latency to any read operation. If the output register is disabled, the memory array is combinatorial. The output changes when the input address changes.                     |

| Output<br>Register<br>Clock<br>Enable<br>Priority | rstreg      | rstreg, rstce                 | <ul> <li>rstreg: The outregce input is ignored when rstregn = 1'b0.         The output register is reset on the next active rdclk edge.     </li> <li>rstce: outregce must be equal to 1'b1 and rstregn = 1'b0 for the output register to be reset on the next active rdclk edge.</li> </ul> |

| Name                                    | Default           | Range           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |

|-----------------------------------------|-------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Use<br>Memory<br>Initialization<br>File | <b>Default</b> On | <b>Range</b> On | Location of the memory initialization file used to initialize the memory contents. This initialization occurs for both synthesis and simulation.  Note  If relative paths are used for the memory initialization file location, the same relative paths must be valid from both the ACE project directory and the simulation directory. It is recommended to locate both of these directories at the same relative depth in the project tree, and to use relative paths that navigate up the tree to the first common directory, before descending the tree to the location of the files.  For example, the Achronix reference designs locate the ACE project in <pre>project root&gt;/src/ace</pre> . The simulation directories are located in <pre>project root&gt;/sim/vcs</pre> or <pre><pre><pre>project root&gt;/sim/questa</pre>. The memory initialization files</pre></pre> |                                       |

|                                         |                   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <pre>are located in <pre></pre></pre> |

## Write and Read Depth

#### **Absolute Limits**

The write and read depths are related to the write and read widths. The absolute limit of these values is detailed in the table below:

Table 6: Write and Read Depths Versus Data Width

| RAM Type    | Memory Width    | Maximum Memory Depth |

|-------------|-----------------|----------------------|

|             | 1 to 11520      | 16384                |

|             | 11521 to 23040  | 8096                 |

| ACX_BRAM72K | 23041 to 46080  | 4096                 |

|             | 46081 to 92160  | 2048                 |

|             | 92161 to 184320 | 1024                 |

|             |                 |                      |

|             | 1–1440          | 4096                 |

|             | 1441 to 2880    | 2048                 |

|             | 2881 to 5760    | 1024                 |

| ACV I DAMOK | 5761 to 11520   | 512                  |

| ACX_LRAM2K  | 11521 to 23040  | 256                  |

|             | 23041 to 46080  | 128                  |

|             | 46081 to 92160  | 64                   |

|             | 92161 to 184320 | 32                   |

## **Device Specific Limits**

Within a device, the largest memory that can be generated is limited by the number of RAM primitives in a column, and the choice of RAM type. The overall ROM limit in bits is equivalent to the number of RAM primitives in a column multiplied by the number of bits in the primitive, (72K for ACX\_BRAM72K, and 2K for ACX\_LRAM2K).

## Examples

The following figure shows the soft IP configured for a 128-bit × 4096-word ROM formed of BRAM72K primitives with the memory output register enabled.

Figure 9: 128-bit × 4096-word ROM Configuration

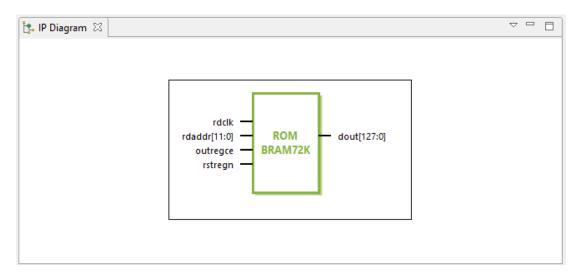

The following figure shows the soft IP IO diagram for the above configuration.

Figure 10: 128-Bit × 4096-Word ROM IP Diagram

# Chapter - 7: Integer Multiplier Soft IP

## Description

The Integer Multiplier soft IP core configures a two input integer multiplier using either RLB (logic) based multipliers or MLP primitives. The multiplier also supports optional result accumulation. The configurator supports sizes of up to 32 × 32 integers, with both signed and unsigned numerical formats.

## Configuration

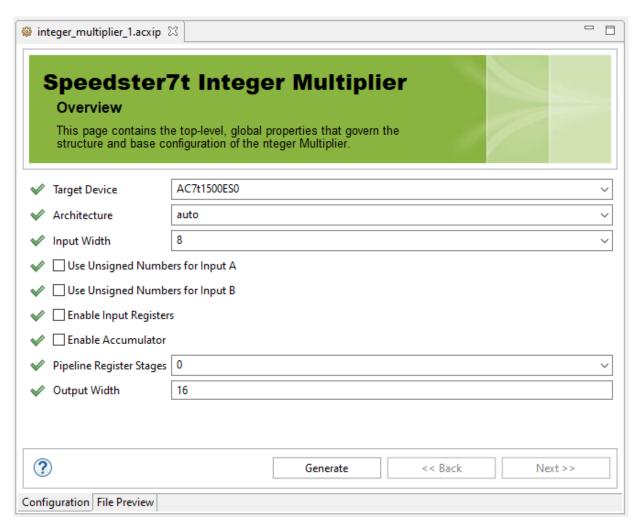

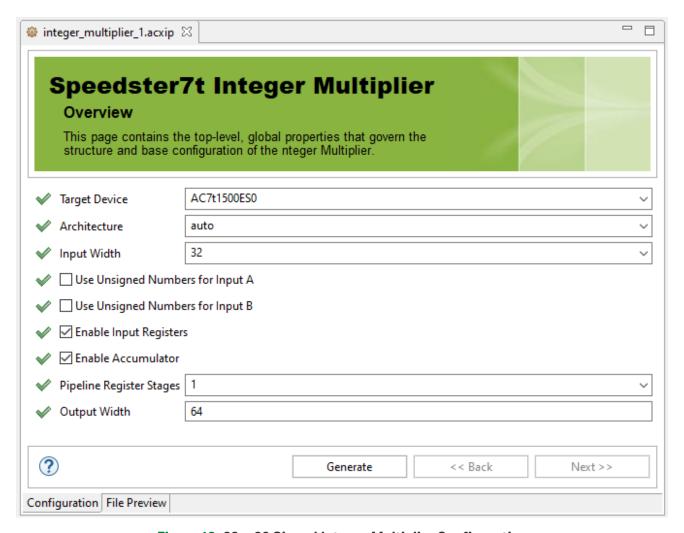

The Integer Multiplier soft IP configurator has the following options:

Figure 11: Integer Multiplier Soft IP Configurator

**Table 7: Configuration Options**

| Name                                        | Default     | Range                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------|-------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target<br>Device                            | AC7t1500ES0 | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Architecture                                | auto        | auto, rlb,<br>mlp             | Determines which primitives should be used to implement the multiplier.  • auto: Allow the tool to choose the most appropriate primitive based on the number formats and sizes selected.  • rlb: Implement the multiplier in fabric logic. The Speedster7t FPGA has a unique MLUT structure which supports very efficient multiplier arrays using logic.  • mlp: Use the MLP primitive to implement the multiplier.                                                          |

| Input Width                                 | 8           | 3, 4, 5, 6, 7,<br>8, 16 or 32 | Width of both a and b inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Use<br>Unsigned<br>Numbers for<br>Input A/B | Off         | On, Off                       | When set, configures the appropriate input to use unsigned numbers. By default, the inputs are set to signed.                                                                                                                                                                                                                                                                                                                                                                |

| Enable<br>Input<br>Registers                | Off         | On, Off                       | When set, enables a register stage for both A and B inputs. This stage adds a cycle of latency to all results. Enabling the input registers adds the inputs i_in_reg_a_ce, i_in_reg_b_ce and i_in_reg_rstn to the resultant soft IP.                                                                                                                                                                                                                                         |

| Enable<br>Accumulator                       | Off         | On, Off                       | The output is the accumulation of the result from each clock cycle. Enabling accumulation adds the input i_load to the resultant soft IP. The accumulation is cleared when i_load is asserted, the output is reset to i_din_a * i_din_b.  The i_load signal has the same pipeline delay to the accumulator as the i_din_a and i_din_b inputs. Therefore it should be applied on the same cycle as the i_din_a and i_din_b inputs that are to start a new accumulation cycle. |

| Pipeline<br>Register<br>Stages              | 0           | 0, 1, 2, 3                    | Add pipeline register stages through the multiplication process.  Enabling pipeline registers improves timing performance at the cost of an additional cycle of latency for each stage enabled.  When any pipeline stages are enabled, the inputs i_pipeline_ce and i_pipeline_rstn are added to the resultant soft IP.                                                                                                                                                      |

## Speedster7t Soft IP User Guide (UG103)

| Name            | Default | Range    | Description                                                                                                                                                                                                                                                     |

|-----------------|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output<br>Width | 16      | 8 to 128 | Width of the data output. Automatically updated by the configurator when Input Width is updated. In addition, the value can be modified to meet requirements.  The valid range changes dependent upon the Input Width and Architecture.                         |

|                 |         |          | When accumulation is enabled, it might be necessary to increase the data output width to account for the growth in the result over multiple accumulation cycles. The minimum output width can be calculated as (2*Input Width)+(number of accumulation cycles). |

#### Table 8: Ports

| Name                         | Direction | Description                                                                                                                                                                                             |

|------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i_clk                        | Input     | Clock input, used for the (optional) registers and accumulator.                                                                                                                                         |

| i_din_a[(Input Width - 1):0] | Input     | 'A' data input to the multiplier.                                                                                                                                                                       |

| i_din_b[(Input Width - 1):0] | Input     | 'B' data input to the multiplier.                                                                                                                                                                       |

| i_in_reg_a_ce                | Input     | (Optional) Clock enable for i_din_a. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                                                   |

| i_in_reg_b_ce                | Input     | (Optional) Clock enable for i_din_b. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                                                   |

| i_in_reg_rstn                | Input     | (Optional) Synchronous active-low reset for input registers. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                           |

| i_pipeline_ce                | Input     | (Optional) Clock enable for pipeline and accumulator registers.  Present when either <b>Enable Accumulator</b> is set to <b>On</b> or <b>Pipeline Register Stages</b> is greater than 0.                |

| i_pipeline_rstn              | Input     | (Optional) Synchronous active-low reset for pipeline and accumulator registers. Present when either <b>Enable Accumulator</b> is set to <b>On</b> or <b>Pipeline Register Stages</b> is greater than 0. |

| Name                         | Direction | Description                                                                                                                                                            |

|------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | Input     | (Optional) When asserted to 1'b1, resets the accumulator to i_din_a*i_din_b, ignoring the previous value. Present when <b>Enable Accumulator</b> is set to <b>On</b> . |

| i_load                       |           | Note  This signal is internally pipelined to have the same latency as i_din_a and i_din_b.                                                                             |

| o_dout[(Output Width - 1):0] | Output    | Result of multiplication and accumulation.                                                                                                                             |

## Examples

The following example shows the integer multiplier configured for signed 32 × 32 inputs, with accumulation and a single pipeline stage:

Figure 12: 32 × 32 Signed Integer Multiplier Configuration

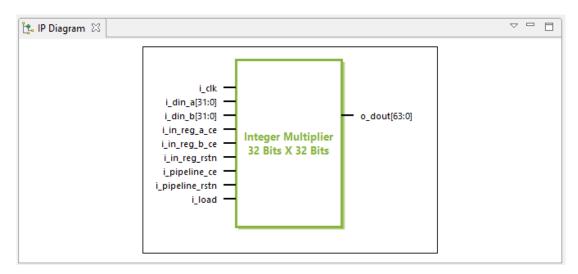

The following figure shows the IP diagram for the above configuration:

Figure 13: 32 x 32 Signed Integer Multiplier IO

## Chapter - 8: Integer Parallel Multiplier Soft IP

### Description

The Integer Parallel Multiplier soft IP core configures multiple integer multipliers. This soft IP core is implemented with the MLP primitive which contains an array of integer multipliers. There can be up to 8 separate multipliers ranging from 3 × 3 to 16 × 16 bits. The multipliers support both signed and unsigned arithmetic.

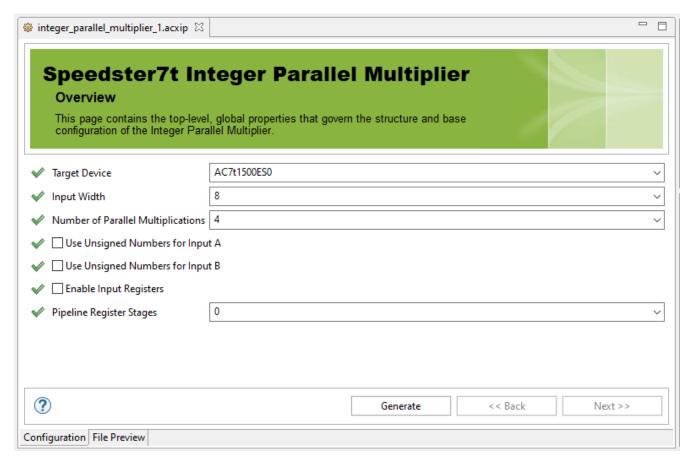

The Integer Parallel Multiplier soft IP configurator has the following options:

Figure 14: Integer Parallel Multiplier Soft IP Configurator

**Table 9: Configuration Options**

| Name                                     | Default     | Range                         | Description                                                                                                                                                                                                                                                                                         |

|------------------------------------------|-------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Device                            | AC7t1500ES0 | All<br>Speedster7t<br>devices | Set to match the target device of the project                                                                                                                                                                                                                                                       |

| Input Width                              | 8           | 3, 4, 5, 6, 7,<br>8 or 16     | Width of the two inputs to each multiplier                                                                                                                                                                                                                                                          |

| Number of<br>Parallel<br>Multiplications | 4           | 2 to 8                        | The number of parallel multipliers to be implemented. The maximum number of multipliers is determined by the Input Width. Refer to the table Number of Multipliers Per Input Width (see page 40), below, for details.                                                                               |

| Use Unsigned<br>Numbers for<br>Input A/B | Off         | On, Off                       | When set, configures the appropriate inputs to use unsigned numbers. By default, the inputs are set to signed.                                                                                                                                                                                      |

| Enable Input<br>Registers                | Off         | On, Off                       | When set, enables a register stage for all multiplier inputs. This adds a cycle of latency to all results. Enabling the input registers adds these inputs to the resultant soft IP core:  • i_in_reg_a_ce  • i_in_reg_b_ce  • i_in_reg_rstn                                                         |

| Pipeline<br>Register<br>Stages           | 0           | 0, 1                          | Adds a pipeline register stage to the multiplication process. Enabling pipeline registers improves timing performance at the cost of an additional cycle of latency. When any pipeline stages are enabled, these inputs are added to the resultant soft IP core:  • i_pipeline_ce • i_pipeline_rstn |

Table 10: Number of Multipliers Per Input Width

| Input Width | Maximum Number of Multipliers |

|-------------|-------------------------------|

| 3           | 8                             |

| 4           | 8                             |

| 5           | 4                             |

| 6           | 4                             |

| 7           | 4                             |

| 8           | 4                             |

| 16          | 2                             |

Table 11: Ports

| Name                         | Direction | Description                                                                                                                                                                                                                                   |

|------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i_clk                        | Input     | Clock input to drive the (optional) registers and accumulator.                                                                                                                                                                                |

| i_din_a[(Input Width - 1):0] | Input     | Packed (see page 41) vector of data to 'A' inputs of multipliers.                                                                                                                                                                             |

| i_din_b[(Input Width - 1):0] | Input     | Packed (see page 41) vector of data to 'B' inputs of multipliers.                                                                                                                                                                             |

| i_in_reg_a_ce                | Input     | (Optional) Clock enable for i_din_a. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                                                                                         |

| i_in_reg_b_ce                | Input     | (Optional) Clock enable for i_din_b. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                                                                                         |

| i_in_reg_rstn                | Input     | (Optional) Synchronous active-low reset for input registers. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                                                                 |

| i_pipeline_ce                | Input     | (Optional) Clock enable for pipeline registers. Present when Pipeline Register Stages is set to 1.                                                                                                                                            |

| i_pipeline_rstn              | Input     | (Optional) Synchronous active-low reset for pipeline registers.  Present when <b>Pipeline Register Stages</b> is set to <b>1</b> .                                                                                                            |

| o_dout[(Output Width – 1):0] | Output    | Output bus consisting of the results from all the multipliers in parallel. Output Width is dynamically calculated by the configurator. See Output Format (see page 41) for details of how the results are assembled in the single output bus. |

#### Input Format

Each multiplier input is formed from an array of the individual inputs packed in a single input vector:

```

Code

i_din_a/b(i) = i_din_a/b[i * int_size +: int_size];

```

#### **Output Format**

For each multiplier, the result width in bits is equal to 2 × Input Width.

The results from all the parallel multiplications are output as a concatenation on the o\_dout output. The width of this output is calculated as follows:

Output Width = Number of Parallel Multiplications × 2 × Input Width.

The bit lanes used for the result of an individual multiplier are found by multiplying the number of the multiplier (starting at 0) by the result width.

#### **Example**

If four 8 × 8 multipliers are configured:

Result Width =  $2 \times 8 = 16$  bits

Output Width =  $4 \times 16 = 64$  bits

Each individual multiplier result appears in the lanes detailed in the table below.

Table 12: Output Bus Organization

| Multiplier Number | Result        |

|-------------------|---------------|

| 0                 | o_dout[15:0]  |

| 1                 | o_dout[31:16] |

| 2                 | o_dout[47:32] |

| 3                 | o_dout[63:48] |

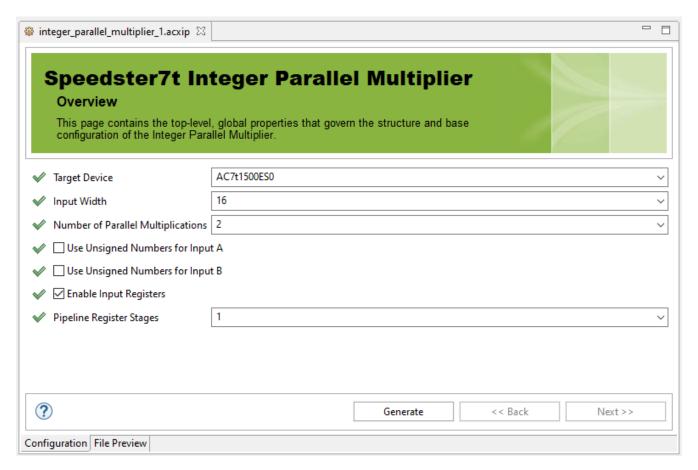

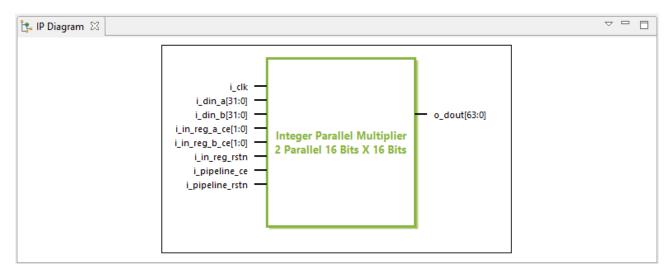

The following example shows the integer parallel multiplier configured for two signed  $16 \times 16$  multiplications, with input registers and and an internal pipeline stage:

Figure 15: Two 16 × 16 Signed Parallel Integer Multiplier Configuration

Figure 16: Two 16 × 16 Signed Parallel Integer Multiplier I/O

# Chapter - 9: Integer Parallel Sum of Products Soft IP

### Description

The Integer Parallel Sum of Products soft IP core configures multiple parallel integer multipliers with a single summed result. This soft IP core is implemented with the MLP primitive which contains an array of integer multipliers and associated adders. Up to 24 parallel multipliers, ranging from 3 × 3 to 16 × 16 bits can be used. The multipliers support both signed and unsigned arithmetic. The final output can optionally be accumulated.

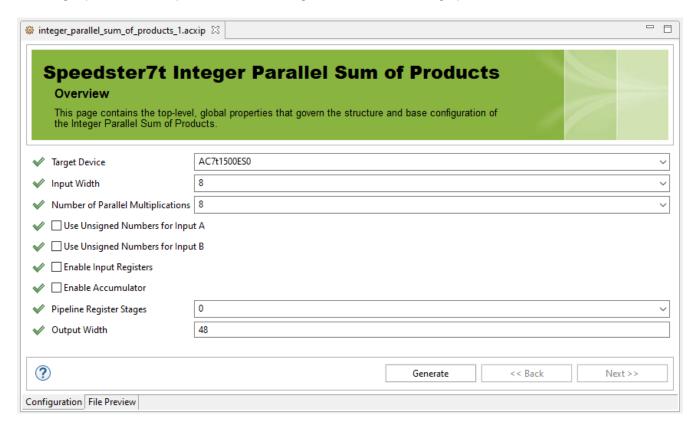

The integer parallel sum of products soft IP configurator has the following options:

Figure 17: Integer Parallel Sum of Products Configurator

**Table 13: Configuration Options**

| Name                                     | Default     | Range                         | Description                                                                                                                                                                                                                      |

|------------------------------------------|-------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Device                            | AC7t1500ES0 | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                   |

| Input Width                              | 8           | 3, 4, 5, 6, 7,<br>8 or 16     | Width of the two inputs to each multiplier.                                                                                                                                                                                      |

| Number of<br>Parallel<br>Multiplications | 8           | 1 to 24                       | The number of parallel multipliers to be implemented and their results summed. The maximum number of multipliers is determined by the Input Width. Refer to the Maximum Number of Multipliers Per Input Width table for details. |

| Use Unsigned<br>Numbers for<br>Input A/B | Off         | On, Off                       | When set, configures the appropriate inputs to use unsigned numbers. The inputs are signed by default.                                                                                                                           |

| Name                           | Default | Range     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable Input<br>Registers      | Off     | On, Off   | When set, enables a register stage for all multiplier inputs. This adds a cycle of latency to all results. Enabling the input registers adds these inputs to the resultant soft IP core:  • i_in_reg_a_ce  • i_in_reg_b_ce  • i_in_reg_rstn                                                                                                                                                                                                                                                   |

| Enable<br>Accumulator          | Off     | On, Off   | The output is the accumulation of the result from each clock cycle. Enabling accumulation adds the input i_load to the resultant soft IP core. The accumulation is cleared when i_load is asserted.                                                                                                                                                                                                                                                                                           |

| Pipeline<br>Register<br>Stages | 0       | 0, 1 or 2 | Adds pipeline register stages to the multiplication process. Enabling pipeline register stages improves timing performance at the cost of an additional cycle of latency per stage. When any pipeline stages are enabled, these inputs are added to the resultant soft IP core:  • i_pipeline_ce  • i_pipeline_rstn                                                                                                                                                                           |

| Output Width                   | 48      | 3 to 48   | Width of the data output. By default, this value is set to 48 bits. This value can be reduced if required.                                                                                                                                                                                                                                                                                                                                                                                    |

|                                |         |           | Ensure that <b>Output Width</b> is sufficient to represent the maximum result that can be accumulated. In the event of overflow, the higher order bits of any result are truncated. When accumulation is enabled, it might be necessary to increase the data output width to account for the growth in the result over multiple accumulation cycles. The minimum output width can be calculated as:  (2 × Input Width × Number of Parallel Multiplications) + (number of accumulation cycles) |

Table 14: Maximum Number of Multipliers Per Input Width

| Input Width | Maximum Number of Multipliers |

|-------------|-------------------------------|

| 3           | 24                            |

| 4           | 16                            |

| 5           | 12                            |

| 6           | 12                            |

| 7           | 10                            |

| 8           | 8                             |

| 16          | 4                             |

Table 15: Ports

| Name                         | Direction | Description                                                                                                                                                                              |

|------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i_clk                        | Input     | Clock input, used for the (optional) registers and accumulator.                                                                                                                          |

| i_din_a[(data width - 1):0]  | Input     | Packed (see page 48) data vector to the 'A' inputs of the multipliers where data width = Input Width × Number of Parallel Multiplications.                                               |

| i_din_b[(data width - 1):0]  | Input     | Packed (see page 48) data vector to the 'B' inputs of the multipliers where data width = Input Width × Number of Parallel Multiplications.                                               |

| i_in_reg_a_ce                | Input     | (Optional) Clock enable for i_din_a. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                                    |

| i_in_reg_b_ce                | Input     | (Optional) Clock enable for i_din_b. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                                                    |

| i_in_reg_rstn                | Input     | (Optional) Synchronous active-low reset for input registers. Present when <b>Enable Input Registers</b> is set to <b>On</b> .                                                            |

| i_pipeline_ce                | Input     | (Optional) Clock enable for pipeline registers. Present when either <b>Enable Accumulator</b> is set to <b>On</b> or <b>Pipeline Register Stages</b> is greater than 0.                  |

| i_pipeline_rstn              | Input     | (Optional) Synchronous active-low reset for pipeline registers.  Present when either <b>Enable Accumulator</b> is set to <b>On</b> or <b>Pipeline Register Stages</b> is greater than 0. |

|                              | Input     | (Optional) When asserted to 1'b1, resets the accumulator to i_din_a × i_din_b, ignoring the previous value. Present when <b>Enable Accumulator</b> is set to On.                         |

| i_load                       |           | Note  This signal is internally pipelined to have the same latency as i_din_a and i_din_b.                                                                                               |

| o_dout[(Output Width - 1):0] | Output    | Output bus consisting of the sum of products from all of the multipliers in parallel.                                                                                                    |

#### Input Format

Each multiplier input is formed from an array of the individual inputs, packed in a single input vector.

```

Code

i_din_a / b(i) = i_din_a / b[i*int_size +: int_size];

```

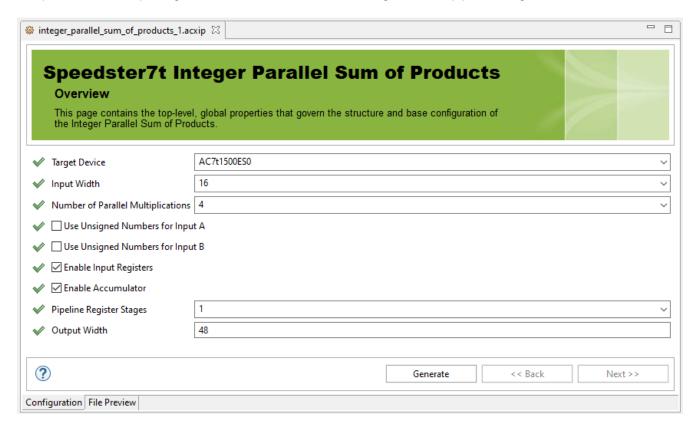

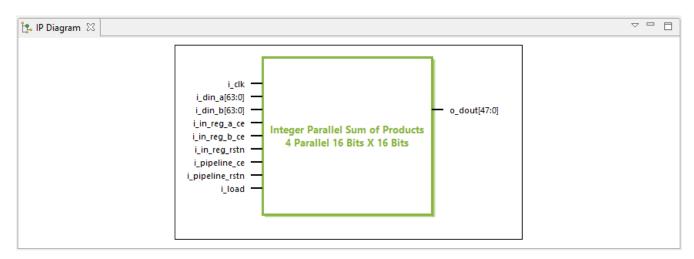

The following example shows the integer parallel sum of products configured for four signed 16 × 16 multiplications with input registers, accumulation and and a single internal pipeline stage.

Figure 18: Four 16 × 16 Signed Multiplier Sum of Products Configuration

Figure 19: Four 16 × 16 Signed Multiplier Sum of Products I/O

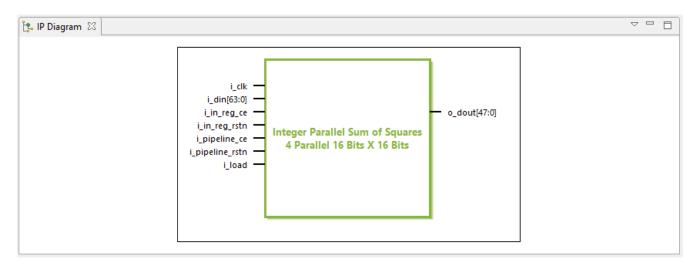

# Chapter - 10: Integer Parallel Sum of Squares Soft IP

#### Description

The Integer Parallel Sum of Squares soft IP core configures multiple parallel integer square ( $n^2$ ) multipliers with a single summed result. This soft IP core is implemented with the MLP primitive which contains an array of integer multipliers and associated adders. Up to 32 parallel multipliers, ranging from 3 × 3 to 16 × 16 bits can be configured. The multipliers support both signed and unsigned arithmetic. The final output can optionally be accumulated.

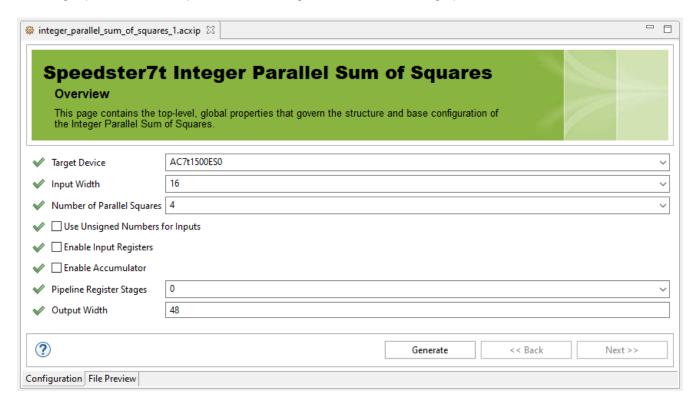

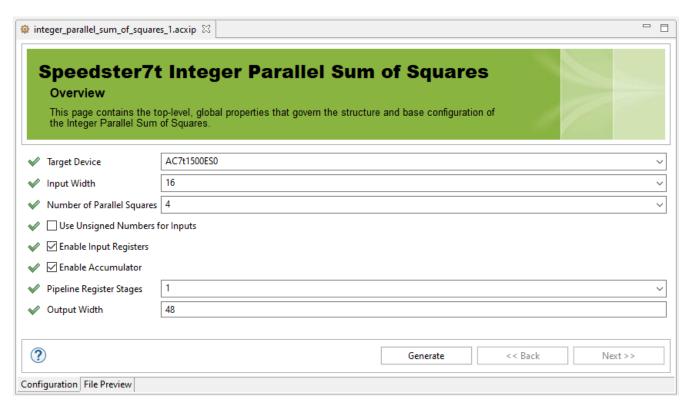

The integer parallel sum of squares soft IP configurator has the following options:

Figure 20: Integer Parallel Sum of Squares Configurator

**Table 16: Configuration Options**

| Name                                    | Default     | Range                         | Description                                                                                                                                                                                                                                     |

|-----------------------------------------|-------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target<br>Device                        | AC7t1500ES0 | All<br>Speedster7t<br>devices | Set to match the target device of the project.                                                                                                                                                                                                  |

| Input Width                             | 8           | 3, 4, 5, 6, 7,<br>8 or 16     | Width of the input to be squared.                                                                                                                                                                                                               |

| Number of<br>Parallel<br>Squares        | 8           | 1 to 32                       | The number of parallel squaring multipliers to be implemented and their results summed. The maximum number of multipliers is determined by the Input Width. Refer to the Maximum Number of Multipliers Per Input Width table below for details. |

| Use<br>Unsigned<br>Numbers for<br>Input | Off         | On, Off                       | When set, configures the input to use unsigned numbers. The input is signed by default.                                                                                                                                                         |

| Name                           | Default | Range     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable<br>Input<br>Registers   | Off     | On, Off   | When set, enables a register stage for the input. Adds a cycle of latency to all results. Enabling the input registers adds these inputs to the resultant soft IP core:  • i_in_reg_ce • i_in_reg_rstn                                                                                                                                                                                                                                                                                                                                                                                            |

| Enable<br>Accumulator          | Off     | On, Off   | Output is the accumulation of the result from each clock cycle.  Enabling accumulation adds these inputs to the resultant soft IP core:  • i_load  • i_pipeline_ce  • i_pipeline_rstn  The accumulation is cleared when i_load is asserted.                                                                                                                                                                                                                                                                                                                                                       |

| Pipeline<br>Register<br>Stages | 0       | 0, 1 or 2 | Adds pipeline register stages to the multiplication process. Enabling pipeline register stages improves timing performance at the cost of an additional cycle of latency per stage. When any pipeline stages are enabled, these inputs are added to the resultant soft IP core:  • i_pipeline_ce  • i_pipeline_rstn                                                                                                                                                                                                                                                                               |

| Output<br>Width                | 48      | 3 to 48   | Width of the data output. By default, this value is set to 48 bits. This value can be reduced if required.  Note  Ensure that Output Width is sufficient to represent the maximum result that can be accumulated. In the event of overflow, the higher order bits of any result are truncated.  When accumulation is enabled, it might be necessary to increase the data output width to account for the growth in the result over multiple accumulation cycles. The minimum output width can be calculated as:  (2 × Input Width × Number of Parallel Squares) + (number of accumulation cycles) |

Table 17: Maximum Number of Multipliers Per Input Width

| Input Width | Maximum Number of Multipliers |

|-------------|-------------------------------|

| 3           | 32                            |

| 4           | 32                            |

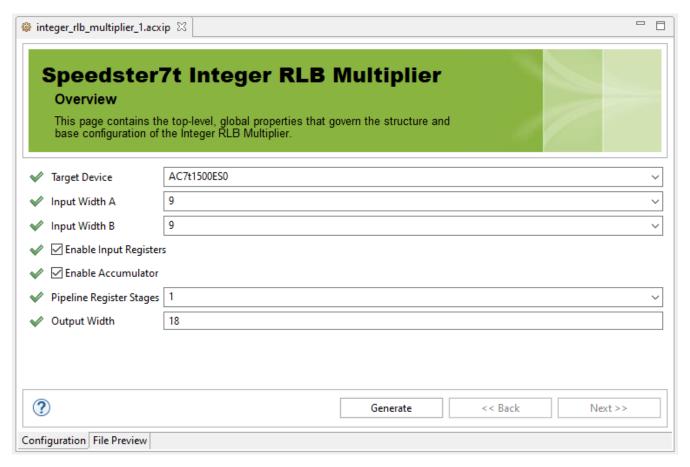

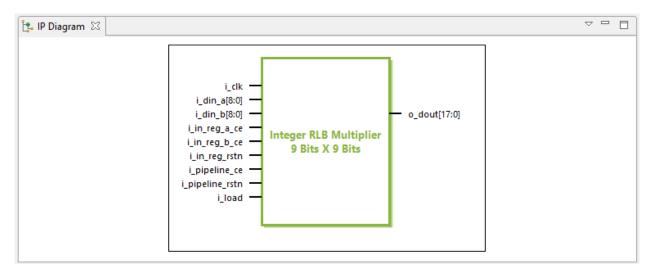

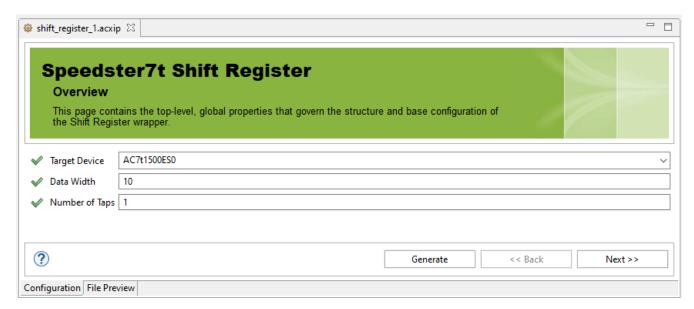

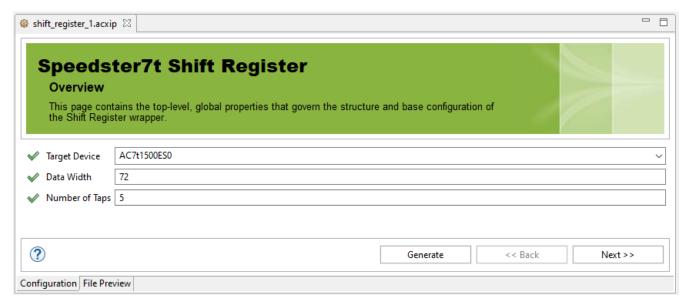

| 5           | 16                            |