# Speedster7t SerDes User Guide (UG099)

**Speedster FPGAs**

**Preliminary Data**

# Copyrights, Trademarks and Disclaimers

Copyright © 2022 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedster and VectorPath are registered trademarks, and Speedcore and Speedchip are trademarks of Achronix Semiconductor Corporation. All other trademarks are the property of their prospective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

#### **Preliminary Data**

This document contains preliminary information and is subject to change without notice. Information provided herein is based on internal engineering specifications and/or initial characterization data.

#### **Achronix Semiconductor Corporation**

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail: info@achronix.com

# Table of Contents

| Chapter - 1: Introduction                    | 7  |

|----------------------------------------------|----|

| Chapter - 2: Overview                        | 8  |

| Speedster7t FPGA SerDes PHY Highlights       | 8  |

| SerDes Placement on Speedster7t Devices      | 10 |

| PMA                                          | 11 |

| Physical Coding Subsystem (PCS)              | 12 |

| ACE Support for the Speedster7t FPGA SerDes  | 12 |

| Chapter - 3: PMA Architecture                | 13 |

| Speedster7t SerDes Block Diagram             | 13 |

| Common Block                                 | 13 |

| Clocking Architecture                        |    |

| Common LC PLL                                |    |

| Lane PLLs                                    |    |

| Speedster7t SerDes PHY Interface             |    |

| Transmit/Receive Block                       |    |

| Transmit Equalization                        |    |

| Receiver Block                               |    |

| Clocking                                     | 18 |

| Speedster7t SerDes PMA Configuration Options | 19 |

| Speedster7t SerDes Test and Debug            | 20 |

| Near End Serial Loopback                     |    |

| Near End Parallel Loopback                   |    |

| Serdes RX Equalization                       |    |

| ·                                            |    |

| Loopback Modes                               |    |

| Chapter - 4: Speedster7t PCS Block           |    |

| Introduction                                 |    |

| PCS Modes                                    |    |

| PCS Features                                 | 26 |

| PCS SerDes Block Diagram                        | 26 |

|-------------------------------------------------|----|

| Reference Clock Sharing                         | 28 |

| PCS Transmit Architecture                       |    |

| Transmit MUX Logic                              |    |

| 8b/10b Encoder                                  |    |

| 128b/130b Encoder Path                          |    |

| PCS Receive Architecture                        |    |

| 8b/10b Decoder Path                             |    |

| 128b/130b Decoder Path                          |    |

| 64b/66b and 64b/67b Bit Gearboxing              |    |

| Gearbox Mode                                    | 32 |

| Gearboxing Implementation                       |    |

| Gearbox Ports Mapping                           | 34 |

| PIPE Mode                                       | 34 |

| Rates                                           | 35 |

| PIPE Ports Mapping                              | 36 |

| Chapter - 5: Speedster7t Serdes Register Map    | 40 |

| Introduction                                    | 40 |

| Control and Status Registers                    | 40 |

| Global Address Space                            |    |

| CSR Addressing                                  |    |

| Target ID Addressing                            |    |

| IP ID Addressing                                |    |

| Register Address Within the SerDes              |    |

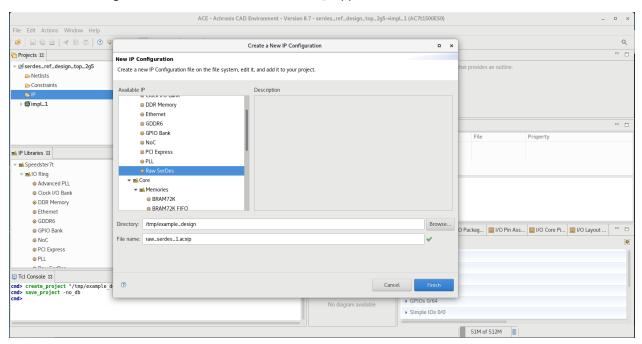

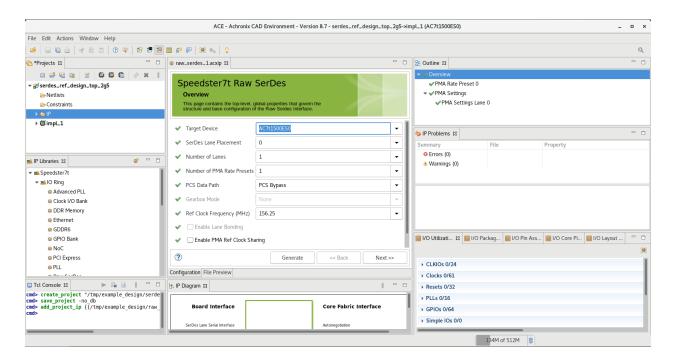

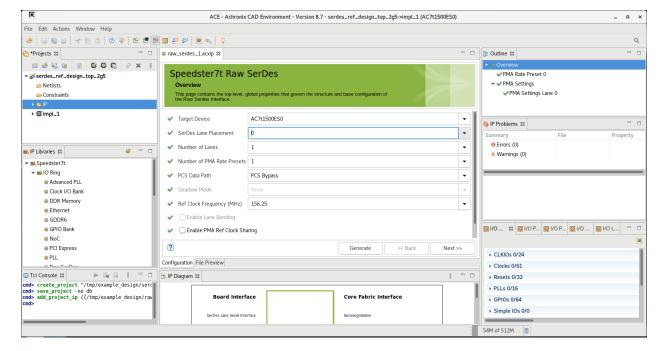

| Chapter - 6: ACE Support for Speedster7t SerDes |    |

| Introduction                                    |    |

|                                                 |    |

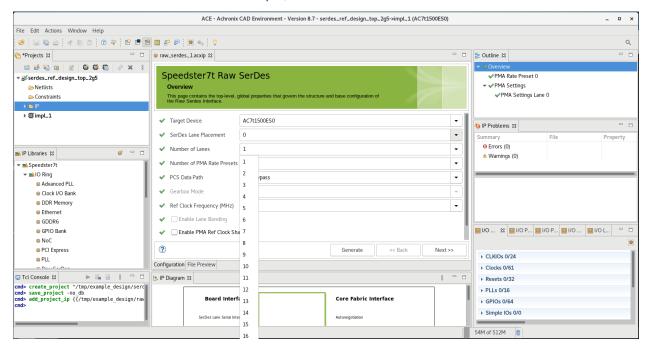

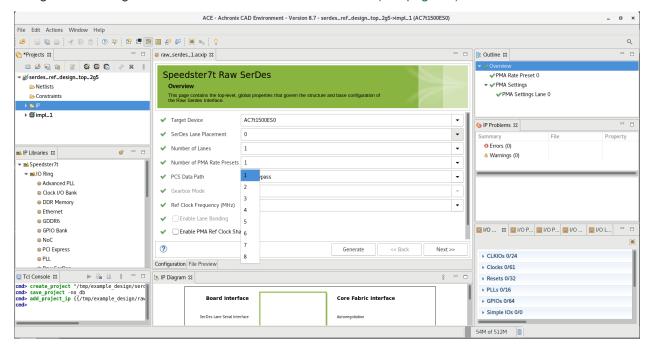

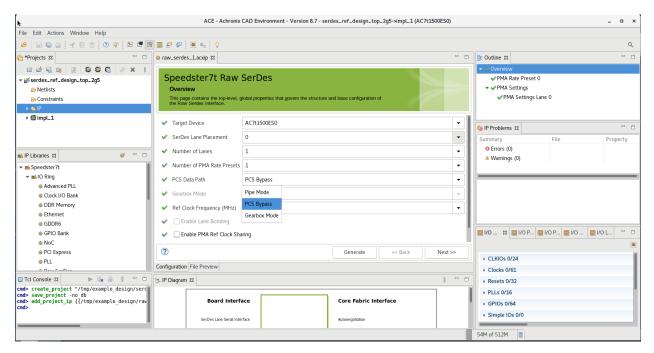

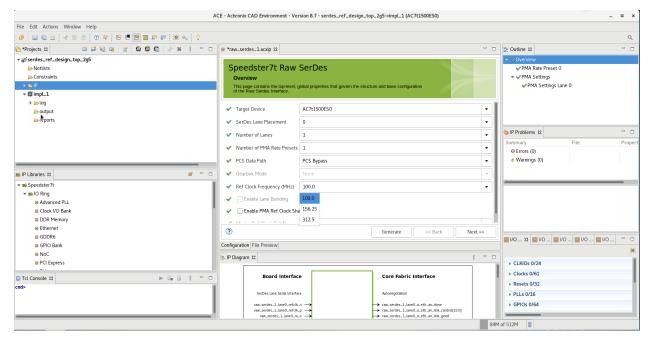

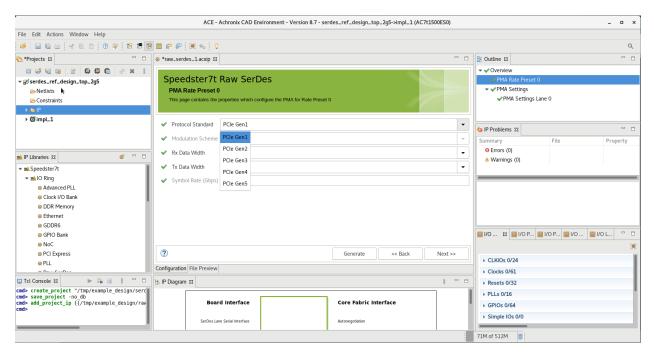

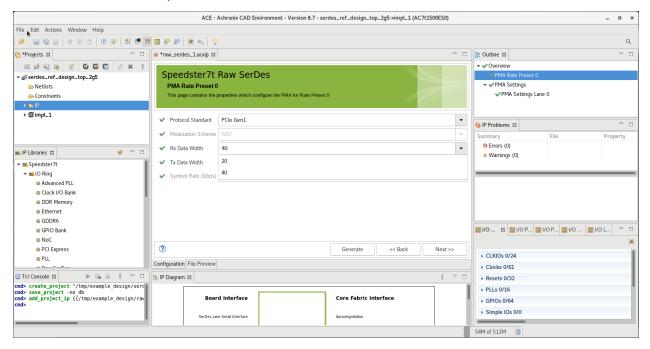

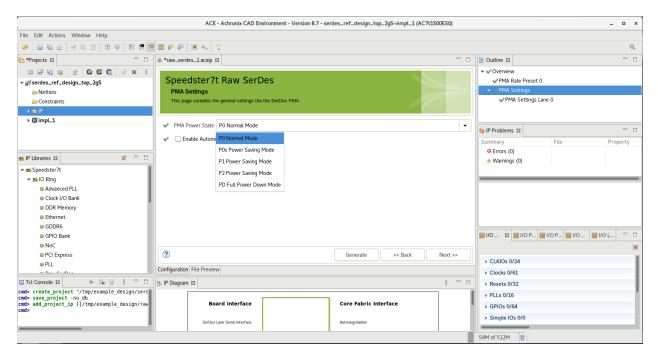

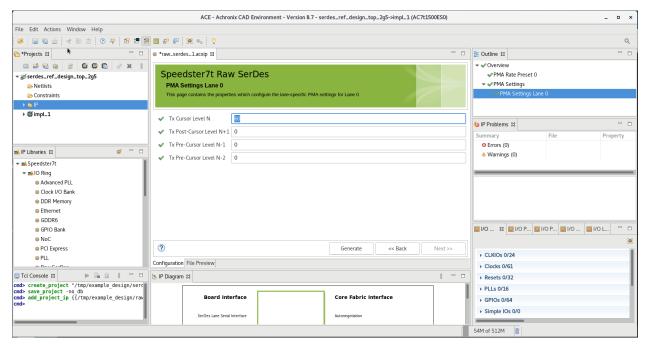

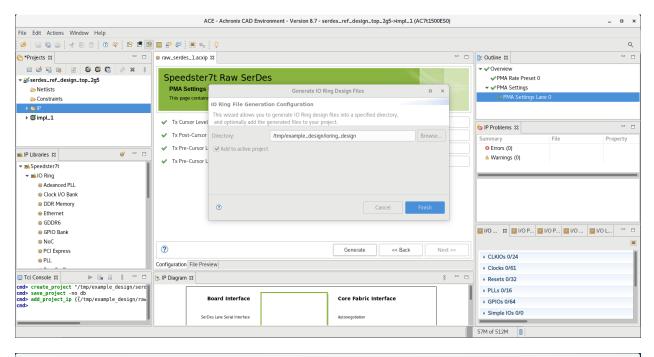

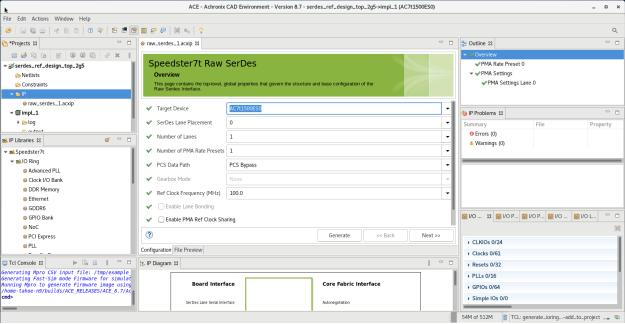

| SerDes IP Configuration                         |    |

| New SerDes IP Configuration                     |    |

| Chapter - 7: Simulation of Speedster7t SerDes   | 52 |

| Device Simulation Model                         |    |

| Selecting the Required DSM                      |    |

| IO Ring Connection                              | 53 |

|                                                 |    |

## Speedster7t SerDes User Guide (UG099)

| Special SerDes Configuration | 54 |

|------------------------------|----|

| Revision History             | 55 |

# Chapter - 1: Introduction

The Achronix 7nm Speedster®7t FPGA family is specifically designed to deliver extremely high performance for demanding applications including data-center workloads and networking infrastructure. The processing tasks associated with these high-performance applications, specifically those associated with artificial intelligence, machine learning (Al/ML) and high-speed networking, represent some of the most demanding processing workloads in the data center. The Achronix Speedster7t FPGA SerDes provides the foundation for high-speed, low power interconnects between Speedster7t FPGAs and external components.

This user guide describes the function and operation of the Achronix Speedster7t DSP SerDes PHY IP for multi-standard applications. The Speedster7t FPGA family incorporates 24 to 32 instances of high-performance, low-power, multi-standard SerDes PHY, which are highly configurable and support leading NRZ and PAM4 data center standards from 1 Gbps to 56 Gbps in raw mode. Protocols ranging from PCI-Express Gen1 to 100 Gbps Ethernet are supported.

# Chapter - 2: Overview

The Speedster7t AC7t1500 incorporates thirty-two SerDes transmit/receive pairs. These high-performance, low-power, multi-standard SerDes PHYs are highly configurable and support all leading NRZ and PAM4 standards from 1 Gbps to 112 Gbps (even including standards which are currently in development).

## Speedster7t FPGA SerDes PHY Highlights

- Digital DSP-based SerDes architecture, performance up to 56 Gbps while consuming ~6 mW/Gbps

- Innovative analog to digital converter (ADC) and digital signal processing (DSP) architecture supports long reach channel losses with near-end crosstalk (NEXT) noise

- · Power efficient for multi-lane operation

- Configurable DSP solution supports multiple power states and loop-timed applications

- Wide tuning (1-56 Gbps), low-jitter clock generation

- · Independent transmit and receive lane clocking

- DSP receiver

- Low-power, dynamic-rate, time-interleaved ADC

- Power scales with sampling rate and with necessary signal to noise ratio (SNR)

- Digital clock to data recovery (CDR) quickly acquires optimum sampling times for incoming signals.

- Blind adaptive equalizer

- Low-power transmitter

- Low-power, voltage-mode driver able to generate 56 Gbps PAM4

- Power scales with transmit launch swings to meet necessary channel conditions

- · Reconfigurable five-tap finite impulse response (FIR) filter

- Integrated Ethernet link training and auto-negotiation

#### **Table 1: Supported Standards**

| Standards                                                                                                                                                                                                                                  | Notes |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| OIF Chip-Chip/Module Backplane                                                                                                                                                                                                             |       |

| <ul> <li>CEI-56G-USR/XSR/VSR/MR/LR-PAM4 (supports NRZ as well)</li> <li>CEI-28G-VSR/SR/MR (19.6-28.1Gbps), CEI-25G-LR (19.9 – 25.8Gbps)</li> <li>CEI-11G SR/MR/LR (9.95 – 11.1 Gbps)</li> <li>CEI-6G SR/LR (4.976 – 6.375 Gbps)</li> </ul> |       |

| Ethernet Chip-Chip/Module Backplane                                                                                                                                                                                                        |       |

| Standards                                                                                                                                                                                    | Notes                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| <ul> <li>Ethernet (53.125 Gbps, 26.5625 Gbps, 25.78125 Gbps, 10.3125 Gbps, 3.125 Gbps, 1.25 Gbps)</li> </ul>                                                                                 |                          |

| 400 Gbps Ethernet — CDAUI-8                                                                                                                                                                  | 8×50 Gbps (802.3bs)      |

| • 200 Gbps Ethernet — 200GBASE-KR4 (802.3ck)                                                                                                                                                 | 4×50 Gbps (802.3cd)      |

| • 100 Gbps Ethernet — 200GBASE-KR2 (802.3ck)                                                                                                                                                 | 2×50 Gbps (802.3cd)      |

| 100 Gbps Ethernet — 100GBASE-KR4 & KP4                                                                                                                                                       | 4×25 Gbps (802.3bj)      |

| 40 Gbps Ethernet — XLAUI, 10G-BASE-KR4                                                                                                                                                       | 4×10.3125 Gbps (802.3ba) |

| <ul> <li>10 Gbps Ethernet — XAUI, 10G-BASE-KR (3.125 Gbps, 10.3125 Gbps, 10.3125 Gbps)</li> </ul>                                                                                            | 802.3ap                  |

| Gigabit Ethernet — 1000BASE-CX, SGMII (1.25 Gbps)                                                                                                                                            |                          |

| Synchronous Ethernet (ITU-T G.8262)                                                                                                                                                          |                          |

| Optical Chip-Module                                                                                                                                                                          |                          |

| <ul><li>Interlaken (3.125–12.5 Gbps, 25 Gbps)</li><li>Fiber Channel</li></ul>                                                                                                                |                          |

| Computing                                                                                                                                                                                    |                          |

| <ul> <li>PCI Express Gen1, Gen2, Gen3, Gen4, Gen5 (2.5 Gbps, 5.0 Gbps, 8 Gbps, 16 Gbps, 32 Gbps)</li> <li>USB 3.0/3.1</li> <li>Quickpath QPI / KTI / UPI</li> </ul>                          |                          |

| PON                                                                                                                                                                                          |                          |

| <ul> <li>GPON (1.25 Gbps, 2.5 Gbps, 10.0 Gbps)</li> <li>E-PON (1.25 Gbps, 2.5 Gbps, 10.0 Gbps)</li> </ul>                                                                                    |                          |

| Wireless                                                                                                                                                                                     |                          |

| <ul> <li>CPRI (24.576 Gbps, 24.330 Gbps, 19.660 Gbps, 12.165 Gbps, 10.137 Gbps, 9.830 Gbps, 6.144 Gbps, 3.072 Gbps, 2.457 Gbps, 1.228 Gbps)</li> <li>JESD204A/B/C (3.125–25 Gbps)</li> </ul> |                          |

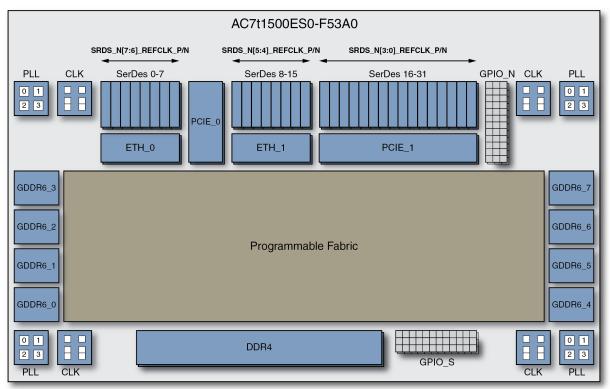

# SerDes Placement on Speedster7t Devices

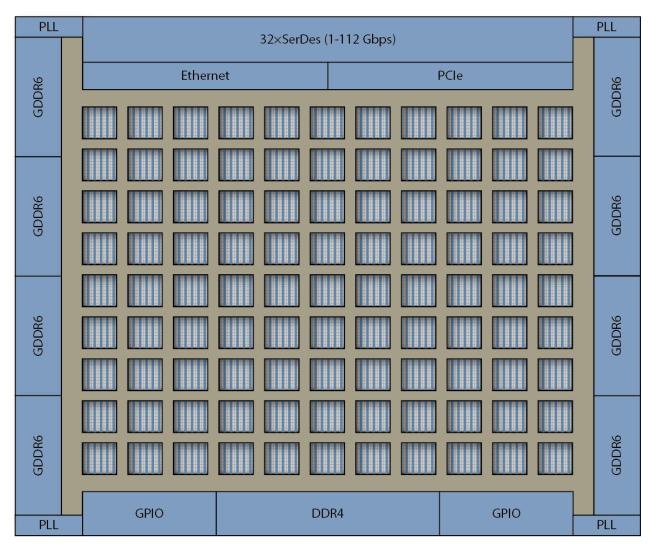

The Speedster7t FPGAs have both PCIe and Ethernet interfaces that use the SerDes PHY. All SerDes lanes can also be used independently (raw mode). The figure below shows the placement of the interface subsystems of the Speedster7t AC7t1500 device.

#### Note

For raw SerDes applications (those not using Ethernet MAC or PCIe IP), bandwidth is limited to 1–56 Gbps.

47418853-04.2022.04.23

Figure 1: Speedster7t AC7t1500 SerDes Placement

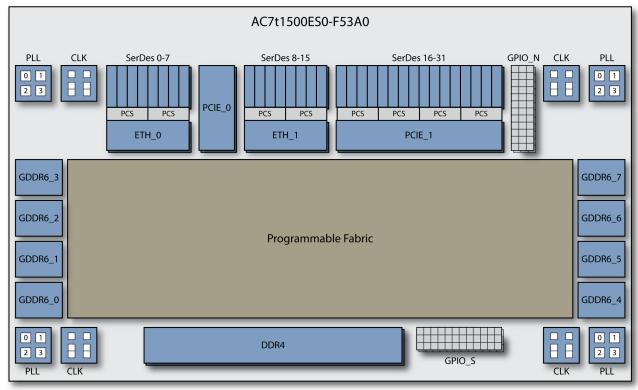

Eight quads of SerDes PHY are located at the north side of the chip as shown in the figure below.

47418853-01.2020.08.0

Figure 2: Speedster7t AC7t1500 Device Top-Level Block Diagram

Each SerDes instance is named "Serdes [x]" and they are organized as follows:

- Sixteen lanes, Serdes [31:16], are associated with a hard PCle controller

- Eight lanes, Serdes [15:8], are associated with a hard Ethernet controller

- Eight lanes, Serdes [7:0], are associated with both the Ethernet and PCIe controllers

When operating in conjunction with the associated hard controller, the operation of the SerDes is managed by the controller per the selected protocol. All 31 SerDes lanes can be used in raw mode. A single lane is the minimum number of lanes in a quad that can be selected for raw mode.

A quad can not be split. All lanes in a quad must be associated with an ethernet controller, PCIe controller, or raw mode. In raw mode the PCS block can be accessed directly by the user design in the FPGA fabric and the controllers are bypassed.

## **PMA**

The SerDes PHYs are arranged as quads made up of four transmit/receive lanes and a common block. This common block is responsible for the following:

- Receiving the reference clock

- Generating clocks for the transmit and receive blocks (with 16-bit fractional multiplication factors and optional spread spectrum)

- Calibration

Providing access to control/status registers

The transmit and receive portion of each lane contains an internal four-tap FIR filter. The transmitter provides a filter with output drivers that can deliver a 400–1200 mVp-p differential output voltage with adjustable slew rate.

The receive block receives the differential signal from the channel and applies equalization. It then determines level and symbol clock, captures the level and decodes per modulation into one or two bits per received symbol. The data is decoded, de-serialized, and driven out on data bus with a divided baud-clock.

The receiver supports AC and DC coupling with some restrictions on common-mode voltage. It incorporates robust automatically adjusted equalization including AGC, continuous-time linear equalizer (CTLE) with up to 20 dB gain tuned for key data rates, feed-forward equalization (FFE) and decision feedback equalizer (DFE) for robust recovery of data from impaired signals. Fast lock mode for EPON/GPON is also supported.

The SerDes includes debug features including multiple loopback modes and a non-destructive internal eye-scope in the receiver. The eye-scope can measure eye width, eye height and the bit error rate (BER).

# Physical Coding Subsystem (PCS)

The Achronix PCS serves as the conduit for the SerDes datapath to and from the fabric. The PCS provides several options to encode, decode, bond lanes, and reorder bits. The PCS can be bypassed if none of the features are needed for the user design.

Three types of hard PCS controllers are offered within Speedster7t devices:

- 1. One for PCle

- 2. One for Ethernet

- 3. One raw version for direct use by the fabric

The physical layout between the Speedster7t FPGA SerDes PHY and the PCS controllers are shown in the previous figure (see page 11).

## ACE Support for the Speedster7t FPGA SerDes

ACE is the Achronix development tool for placing, routing, configuring, and debugging Achronix FPGAs. ACE works in conjunction with third-party synthesis and simulation tools to provide a complete design environment for Achronix FPGAs. The Speedster7t SerDes PHY can be conveniently configured and controlled through the ACE GIII

For PCIe and Ethernet users, the ACE GUI has predefined options where the SerDes PHY can be configured easily to work seamlessly in PCIe/Ethernet mode. When the SerDes is used in raw mode, the SerDes PHY is configured via the ACE GUI. Configuration options are available by selecting the "Raw SerDes" option in the IP Library. The configuration can also be modified at runtime by writing to the control registers directly. The control and status registers are accessed through the JTAG port or by a NAP in the fabric. Refer to *Runtime Programming of Speedster FPGAs* (AN025) for details on how to access these registers through the JTAG port.

# Chapter - 3: PMA Architecture

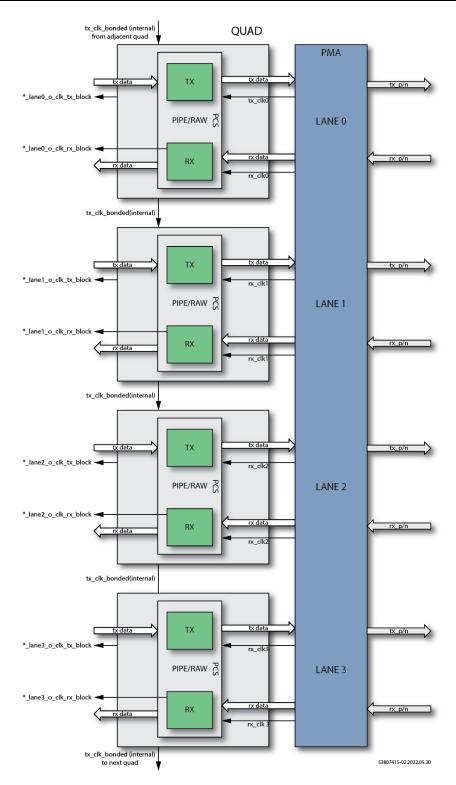

The Speedster7t SerDes PMA is composed of a common block and four transmit/receive blocks (lanes), and the combined assembly is referred to as a quad.

## Speedster7t SerDes Block Diagram

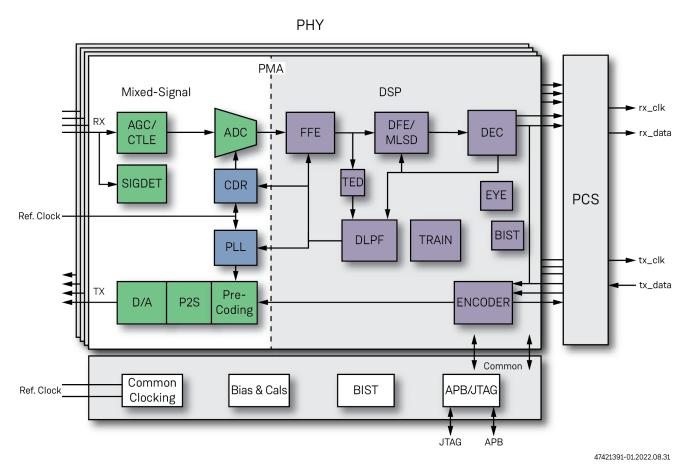

Following is a block diagram of a single lane in a SerDes quad. A detailed sub-block-level diagram of the Speedster7t SerDes PHY can be found in Appendix II of the NDA version of this document.

Figure 3: Speedster7t SerDes PHY Block Diagram

## Common Block

The common block performs calibration and contains control/status registers for the entire quad. The common block also receives the reference clock and generates a multiplied clock for the transmit and receive blocks (with 16-bit fractional multiplication factors and optional spread spectrum mode).

Calibration is performed automatically and can be invoked by register control. Details of the calibration control /status registers are provided in Control and Status Registers (see page 40).

The reference clock for a quad can be selectively sourced from external balls (SRDS\_xx\_REFCLK\_N/P) or from a neighboring quad. The received reference clock can be selectively forwarded to neighboring quads. This option can be selected in the ACE IP configuration tool by selecting **Enable PMA Ref Clock Sharing**.

## Clocking Architecture

The Speedster7t SerDes PHY clocking architecture provides a significant amount of configurability and flexibility. High quality clocks are generated and can be used directly by logic in the fabric. More details can be found in Appendix II *Speedster7t SerDes Architecture PMA*, available under NDA.

#### **External Reference Clocks**

The Speedster7t SerDes PHY reference clocks are used by the common block LC (Inductor capacitor) based PLL (LC PLL) to generate the high-speed clock, hsrefclk, that is distributed to the receive/transmit lane PLLs. The SerDes PHY includes the following external reference clock capabilities:

- Sourcing reference clock from the SRDS\_N[7:0]\_REFCLK external pins.

- Sourcing reference clocks from the adjacent quad for use in the local quad (limited to quads created within a single ACXIP file).

#### Note

More details can be found in Appendix II Speedster7t SerDes Architecture PMA, available under NDA.

#### Common LC PLL

The common LC PLL contains a low quantization noise fractional synthesizer which results in a high-degree flexibility with respect to supported data rates vs. reference clock rates. This fractional synthesis capability is also leveraged to enable spread spectrum clock generation. LC PLLs provide excellent jitter characteristics for a given power.

#### Lane PLLs

Each transmit and receive lane has its own local PLL to enable independent operation between transmit and receive blocks as well as between different lanes. The combination of a common LC PLL and the lane PLLs provide the benefit of flexibility across standards and configurations with the performance of an LC PLL. More details can be found in Appendix II *Speedster7t SerDes Architecture PMA*, available under NDA.

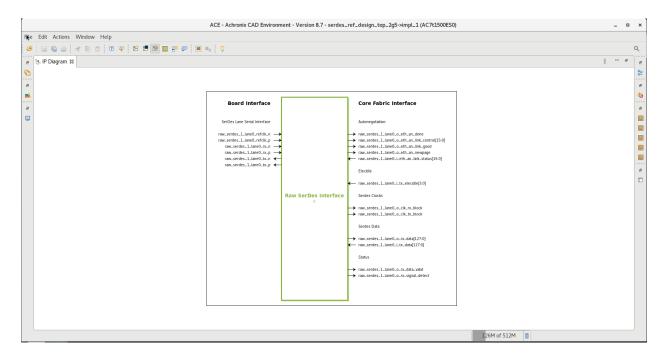

# Speedster7t SerDes PHY Interface

This section provides a brief description of the signal interface between the SerDes PHY and the FPGA in PCS bypass mode. These signals are on a per lane basis. "IP-Name" refers to the name of the ACXIP file and "Lane" refers to the lane number. For example: serdes\_quad\_2g5\_lane0\_o\_eth\_an\_link\_control. More detailed information can be found in Appendix II Speedster7t SerDes Architecture PMA, available under NDA.

**Table 2: Serdes interface Ports**

| Interface Signal Name                       | Direction | Width | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP-Name_Lane[#]_o_eth_an_done               | Output    | 1     | When asserted, indicates auto-negotiation complete (link fully up, including LT and PCS). (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IP-Name_Lane[#]_o_eth_an_link_control[15:0] | Output    | 16    | PCS enable, one-hot encoded. When auto-negotiation (AN) is complete, one of these signals is asserted to enable the attached PCS. (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IP-Name_Lane[#]_o_eth_an_link_good          | Output    | 1     | When asserted, indicates AN has negotiated a link speed and is attempting to start link training/PCS. (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IP-Name_Lane[#]_o_eth_an_newpage            | Input     | 1     | AN newpage received indicator. A positive edge on this signal indicates a new page has been received. The FPGA should read the associated registers, write extended page information, and assert the next_page_loaded bit, if needed. The FPGA might also poll the equivalent register. (1)                                                                                                                                                                                                                                                                                                    |

| IP-Name_Lane[#]_i_eth_an_link_status[15:0]  | Input     | 16    | PCS link status. Must be asserted by the enabled PCS to indicate the link is up. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IP-Name_Lane[#]_i_tx_elecidle[3:0]          | Input     | 4     | Pin control of the transmit electrical idle function. For PCIe applications with synchronous electrical idle requirement:  0 – I[#] transmitter in normal operating mode.  1 – I[#] transmitter placed into electrical idle.  Each bit corresponds to 16 bits of transmit data:  For widths up to 20 bits, only bit 0 is active.  For 32 and 40 bits, bits 1:0 are active.  For 64 bits, bits 3:0 are active.  For all other applications including all PM-4 rates ictl_tx_elecidle_ln[#] should be operated as if all were a single control (i.e., logically tie all four bits together). (1) |

| IP-Name_Lane[#]_o_clk_rx_block              | Output    | 1     | Receive clock synchronous to the receive data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IP-Name_Lane[#]_o_clk_tx_block              | Output    | 1     | Transmit clock synchronous to the transmit data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IP-Name_Lane[#]_o_rx_data[127:0]            | Output    | 128   | Data output bus to the fabric. Software requires all 128 bits are connected to the fabric despite the RX data width chosen in the IP configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IP-Name_Lane[#]_i_tx_data[127:0]            | Input     | 128   | Data input from the fabric. Software requires all 128 bits are connected to the fabric despite the TX data width chosen in the IP configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### Speedster7t SerDes User Guide (UG099)

| Interface Signal Name              | Direction | Width | Description                                                                                                               |

|------------------------------------|-----------|-------|---------------------------------------------------------------------------------------------------------------------------|

| IP-Name_Lane[#]_o_rx_data_valid    | Output    | 1     | Pin output showing lock status of the receive CDR. Timed to ck_r x_block.  0 - CDR unlocked.  1 - CDR locked, data valid. |

| IP-Name_Lane[#]_o_rx_signal_detect | Output    | 1     | Unfiltered output of the analog signal detection block.                                                                   |

#### **Table Notes**

1. Signal not used in PCS bypass mode.

## Transmit/Receive Block

The transmit and receive portion of each lane contains an internal synthesizer which allows independent rate support for each lane.

#### Transmit Block

The transmit block is responsible for capturing the transmit data from the fabric using a transmit clock and sending it serially off chip. This data width is variable and is dependent upon the chosen protocol standard. Within the PMA, the data is modulated (NRZ/PAM4) and serialized before being transmitted. There is an optional 4 tap pre-emphasis filter to help improve the channel signal quality.

## Transmit Equalization

The transmitter includes a five-tap digital FIR filter which boosts the relative amplitude of higher frequency data patterns by adjusting the amplitude of the bit/level being transmitted based on the values of preceding and succeeding bits.

In many cases, the PCIe/Ethernet subsystems attached to the SerDes properly adjust the transmit equalization during the establishment of the link. The transmit equalization can be adjusted manually to match channel requirements. The coefficient values can be overridden by writing new values to the TX FIR coefficients in the CSR registers space.

Further details can be found in Appendix II Speedster7t SerDes Architecture PMA, available under NDA.

Table 3: Transmit Lane Features

| Parameter                | Design Specification                                                                                                                            |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Driver<br>Voltage | <ul><li>Up to 1200 mVdiff-pkpk</li><li>Programmable</li></ul>                                                                                   |

| Transmit<br>Coupling     | Supports:  • External AC coupling  • Floating DC coupled receive termination  • DC coupling, for selected receive termination common modes. (1) |

| Parameter              | Design Specification                                                                                                                                                                               |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-chip<br>Termination | Nominal value: 90Ω                                                                                                                                                                                 |

| Transmit<br>Skew       | <ul> <li>Skew between transmit Lanes &lt; ± 2UI</li> <li>Synchronization of transmit data ensured within multiple lanes of a By-2/By-4 as well as between multiple By-1, By-2 and By-4.</li> </ul> |

| Beaconing              | Output enable control for beaconing.                                                                                                                                                               |

| Receiver<br>Detection  | Fully supports PCI Express receiver detection.                                                                                                                                                     |

1. More details can be found in Appendix I Speedster7t SerDes Overview, available under NDA.

## Receiver Block

The receive channel accepts the serial differential signal from the channel and sends the data and recovered clock to the fabric. The PMA applies a continuous time linear equalization filter (CTLE) in the analog domain before the signal is digitized using a time interleaved analog-to-digital converter (TIADC). A discrete feed forward equalization filter (FFE) is used to reduce inter-symbol interference before the slicer and a decision feed back equalization (DFE) filter are used minimize decision errors. See the Receive Lane Features (see page 17) table for more details.

**Table 4: Receive Lane Features**

| Parameter               | Design Specification                                                                                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Input<br>Range  | Up to 1200 mVdiff-pkpk                                                                                                                                                  |

| Receive<br>Equalization | <ul> <li>CTLE and DSP based equalization</li> <li>Blind Adaptive Receiver and Equalizer <sup>(1)</sup></li> </ul>                                                       |

| Receive Coupling        | Supports:  • External AC coupling  • DC coupled receive termination with internal AC coupling  • DC coupling without internal AC coupling for selected common modes (1) |

| Signal Detection        | <ul> <li>Receive signal envelope detection to support Beaconing and idle-exit detection</li> <li>Digital signal detection</li> </ul>                                    |

| Spread spectrum         | Fully supports recovery of signals with Spread Spectrum (0.5% down spread).                                                                                             |

| Parameter              | Design Specification                                                                                                                                                             |  |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Frequency<br>Accuracy  | Tolerates up to -5350 ppm to +350 ppm of data frequency inaccuracy from PHY reference clock.                                                                                     |  |  |  |

| On-Chip Eye<br>Monitor | n-destructive internal eye monitoring capability.                                                                                                                                |  |  |  |

| Lock Modes             | <ul> <li>Supports both auto-lock to incoming data when valid data is present and manual external control of lock to data</li> <li>Loss-of-Lock detector functionality</li> </ul> |  |  |  |

| Oversampling           | The receive CDR supports the oversampling mode of operation.                                                                                                                     |  |  |  |

| On-chip<br>Termination | Nominal values: 90Ω. <sup>(1)</sup>                                                                                                                                              |  |  |  |

| Reference Clock source | <ul> <li>Independently selectable reference clock input source per lane</li> <li>PMA quad includes reference clock buffers/repeaters and distribution infrastructure</li> </ul>  |  |  |  |

1. More details can be found in Appendix I Speedster7t SerDes Overview, available under NDA.

# Clocking

Clocking frequencies and signal geometry are specified in the following table along with a summary of features of the Common Lane.

**Table 5: Common Lane Features and Requirements**

| Parameter Description                                                                    | Min   | Тур | Max | Unit          |  |  |

|------------------------------------------------------------------------------------------|-------|-----|-----|---------------|--|--|

| General                                                                                  |       |     |     |               |  |  |

| Reference clock frequency range                                                          | 50    |     | 800 | MHz           |  |  |

| Frequency variation                                                                      | -5350 |     | 350 | ppm           |  |  |

| Duty cycle                                                                               | 40    | 50  | 60  | %             |  |  |

| Rise/fall times (20-80%)                                                                 |       |     | 0.2 | Refclk Period |  |  |

| Skew between positive and negative differential inputs                                   |       |     | 10  | ps            |  |  |

| Total integrated RMS phase noise for the band of frequency ranging from 12 kHz to 20 MHz |       |     | 0.7 | psRMS         |  |  |

| External Reference Clock I/O Inputs                                                      |       |     |     |               |  |  |

| Parameter Description              |                     | Min                                                                                                                                                                        | Тур | Max  | Unit |

|------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|

| Innut impedance                    | Terminated mode     | 40                                                                                                                                                                         | 50  | 60   | Ω    |

| Input impedance                    | High-impedance mode | 20k                                                                                                                                                                        |     |      | Ω    |

|                                    | PCle                | 0.15                                                                                                                                                                       |     |      | V    |

| Input Differential Voltage         | LVDS                | 0.25                                                                                                                                                                       |     | 0.4  | V    |

|                                    | LVPECL              | 0.525                                                                                                                                                                      |     | 0.95 | V    |

| Input Common Mode Voltage          |                     | 0                                                                                                                                                                          |     | 1.2  | V    |

| Common Lane Features               |                     |                                                                                                                                                                            |     |      |      |

| Fractional Synthesizer             |                     | <ul> <li>Fractional synthesizer support to eliminate integer<br/>reference clock requirements</li> <li>Programmable spread spectrum generation</li> </ul>                  |     |      |      |

| Synthesizer Loop Timing            |                     | The transmit PLL supports loop timed synchronous operation.                                                                                                                |     |      |      |

| Synthesizer reference clock source |                     | Independently selectable reference clock input source.                                                                                                                     |     |      |      |

| Other clock generation             |                     | <ul> <li>Internal heartbeat clock for power up and beaconing.</li> <li>Internal clock outputs <sup>(1)</sup></li> </ul>                                                    |     |      |      |

| Reference Clock Sources            |                     | <ul> <li>Reference clock I/O buffer that supports a variety of input reference clock signaling (e.g., CML, LVPECL, PCIe)</li> <li>On-chip CML distribution. (1)</li> </ul> |     |      |      |

|                                    |                     |                                                                                                                                                                            |     |      |      |

1. More details can be found in Appendix I Speedster7t SerDes Overview, available under NDA.

# Speedster7t SerDes PMA Configuration Options

**Table 6: PMA Configurability**

| Parameter           | Description                                                                                                                                                     |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number of Lanes     | 1 to 16, lanes must be contiguous in a single IP.                                                                                                               |  |

| PMA Rate Presets    | Up to 8 presets.                                                                                                                                                |  |

| Full Duplex Support | <ul> <li>Synchronized and non-synchronized full duplex operation</li> <li>Independent operation of transmit and receive Lanes (power-down and reset)</li> </ul> |  |

| Parameter                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power States                 | <ul> <li>Fully supports Energy Efficient Ethernet (EEE) low power states (deep sleep, fast wake).</li> <li>Fully supports PCle power savings modes:</li> <li>PD – Full power down on all blocks.</li> <li>P2 – Lowest power/longest recovery time state. Everything powered down except Beaconing and receiver detection.</li> <li>P1 – Low power/ Medium recovery time state. All P2 functionality with synthesizer powered up but transmit driver and receive paths powered down.</li> <li>P0s– Some power saving / fast recovery state. All P1 functionality with receive path powered up and transmit driver powered down.</li> <li>P0 – Normal full operation mode. Everything powered up.</li> </ul> |

| transmit FIR                 | Each tap is independently programmable. (1)  • C(-3) pre-cursor  • C(-2) pre-cursor  • C(-1) pre-cursor  • C(1) post-cursor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Data Path Parallel Interface | Selectable 16/32/64/128 and 20/40 data and byte clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

1. More details can be found in Appendix I Speedster7t SerDes Overview, available under NDA.

# Speedster7t SerDes Test and Debug

## Near End Serial Loopback

This procedure, operating on a quad, isolates the front end external signal and sets both the RX and TX into loopback mode.

Serial transmit to receive (max coverage of serial path) shown as path *one* in Figure 2 (see page 22). The TX data originates in the fabric and is routed back to the fabric. A TCL procedure is provided with the reference design to set the appropriate registers:

Table 7: Near End Serial Transmit To Receive Loopback Procedure

| Item        | Details                                                                             |

|-------------|-------------------------------------------------------------------------------------|

| TCL library | <pre><device>_serdes_utils.tcl Example: AC7t1500ES0_serdes_utils.tcl</device></pre> |

| Procedure   | nes_loopback <target> <quad> <enable></enable></quad></target>                      |

| Targets     | ETHERNET_0, ETHERNET_1, PCIE_1                                                      |

## Near End Parallel Loopback

This procedure, operating on a quad, sets both the RX and TX into near end parallel loopback mode and forces rx\_signal\_detect to be valid.

Parallel transmit to receive (confirms integrity of fabric-to-PMA interface) shown as path *two* in Figure 2 (see page 22). A TCL function is provided with the reference designs to set the appropriate registers:

Table 8: Near End Parallel Transmit To Receive Procedure

| Item        | Details                                                                             |

|-------------|-------------------------------------------------------------------------------------|

| TCL library | <pre><device>_serdes_utils.tcl Example: AC7t1500ES0_serdes_utils.tcl</device></pre> |

| Procedure   | nep_loopback <target> <quad> <enable></enable></quad></target>                      |

| Targets     | ETHERNET_0, ETHERNET_1, PCIE_1                                                      |

## Serdes RX Equalization

This procedure, operating on a quad or a single lane, checks for the absence of CDR lock on the lane. If CDR lock has not been asserted, the procedure activates receive equalization and checks the status bit until an acknowledge is set. The procedure times out if the acknowledge bit is never set.

RX equalization is recommended for rates above 10 Gbps. The procedure is not compatible with PCIE protocols under 10 Gbps when run in pcs\_bypass mode. A TCL procedure is provided with the reference designs to set the appropriate registers:

Table 9: Trigger SerDes RX Equalization Procedure

| Item        | Details                                                                             |

|-------------|-------------------------------------------------------------------------------------|

| TCL library | <pre><device>_serdes_utils.tcl Example: AC7t1500ES0_serdes_utils.tcl</device></pre> |

| Procedure   | acx_pcs_trigger_rx_eq <target> <quad> <max_channel></max_channel></quad></target>   |

| Targets     | ETHERNET_0, ETHERNET_1, PCIE_1                                                      |

| Max Channel | 1–4                                                                                 |

## Clear RX TX State Request

This procedure, operating on a quad, clears the RX and TX request bits for the target and quad specified.

The RX and TX state request must be cleared before any state changes such as equalization. A TCL function is provided with the reference designs to set the appropriate registers:

Table 10: Clear TX RX State Request Procedure

| Item        | Details                                                           |

|-------------|-------------------------------------------------------------------|

| TCL library | <pre><device>_serdes_utils.tcl</device></pre>                     |

| Procedure   | tx_rx_state_req <target> <quad> <enable></enable></quad></target> |

| Targets     | ETHERNET_0, ETHERNET_1, PCIE_1                                    |

## Loopback Modes

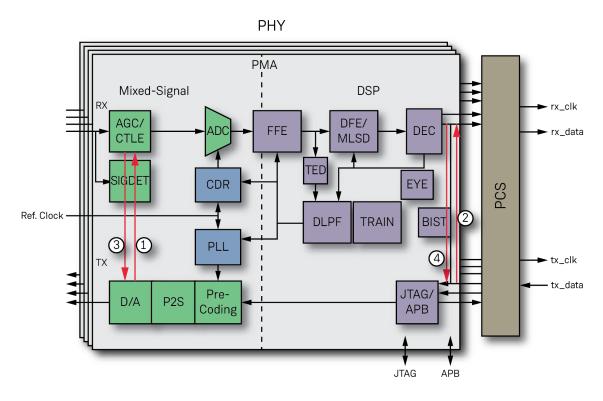

Four PHY Data loopback mode paths are available as detailed in the diagram below:

- 1. Internal serial TX to RX (maximum coverage of serial path) loopback. Data is generated in and looped back to the fabric. The CTLE data bypasses the FIR and IIR filters. Referred to as NES\_loopback. Shown as path 1

- 2. Internal parallel TX to RX. Data is generated in and looped back to the fabric. Referred to as NEP loopback. Shown as path 2.

- 3. External serial RX to TX. Untimed for continuity tests at low rates by external sources. Shown as path 3.

- 4. External parallel RX to TX. Transmits received data with respect to the device. Used to characterize the serdes for compliance and bit error rate. Shown as path 4.

47421391-02.2022.08.31

Figure 4: Speedster7t SerDes PHY Data Loopback Modes

# Chapter - 4: Speedster7t PCS Block

## Introduction

The Achronix PCS serves as the conduit for the SerDes datapath to and from the fabric. The PCS provides several options to encode, decode, bond lanes, and reorder bits. The PCS can be bypassed if none of the features are needed for the user design.

Three types of hard PCS controllers are offered within Speedster7t devices:

- 1. One for PCle

- 2. One for Ethernet

- 3. One raw version for direct use by the fabric

The raw SerDes PCS controller is covered in this section.

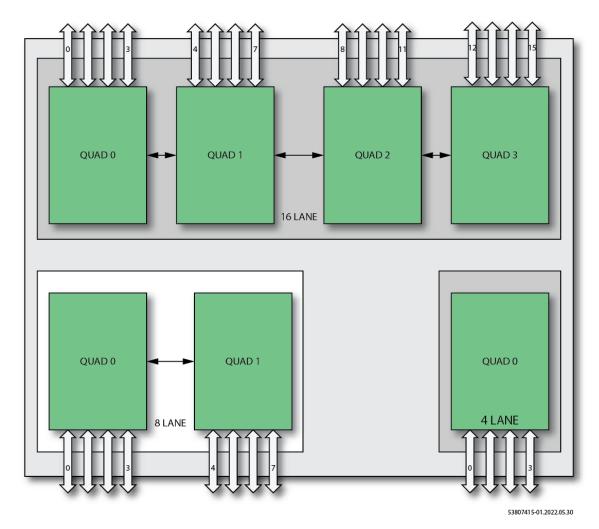

The Achronix PCS can support the rates and performance requirements for other protocols including CPRI, JESD204x and Interlaken. A soft controller is required in the fabric for these protocols. The Achronix PCS and PMA can be thought of as a unit. Some features in the PMA are controlled through the Achronix PCS. All lanes are configured as a quad, but can be used as a single lane or combined with other quads for a configurations that spans 16 lanes. Four quads are used to provided 16 high-speed lanes, two quads for eight lanes, and one quad for a four lane solution as shown in the following figure.

Figure 5: SerDes Configurations

## **PCS Modes**

The PCS has multiple modes:

- Ethernet Mode: The PCS is connected to a hard Ethernet MAC. This is covered in the *Speedster7t Ethernet User Guide* (UG097).

- PCle Mode: The PCS is connected to the hard PCle Gen5 subsystem. This is covered in the *Speedster7t PCle User Guide* (UG098) (support account required).

- Raw SerDes Mode: The PCS routes data directly to and from the fabric. In Raw Mode, there are three options for the datapath. These options can be found in the ACE GUI under the **PCS Data Path** selector.

- Pipe Mode: The data is routed through a PCIe PIPE to enable soft controllers in the fabric, up to GEN4

- PCS Bypass Mode: The data is sent directly to/from the PMA to the fabric. All word alignment must be accounted for in the fabric.

- Gearbox Mode: The data is routed through the gearbox logic. The gearbox logic supports 66b/64b synchronous mode, 66b/64b asynchronous mode, and 67b/64b synchronous mode.

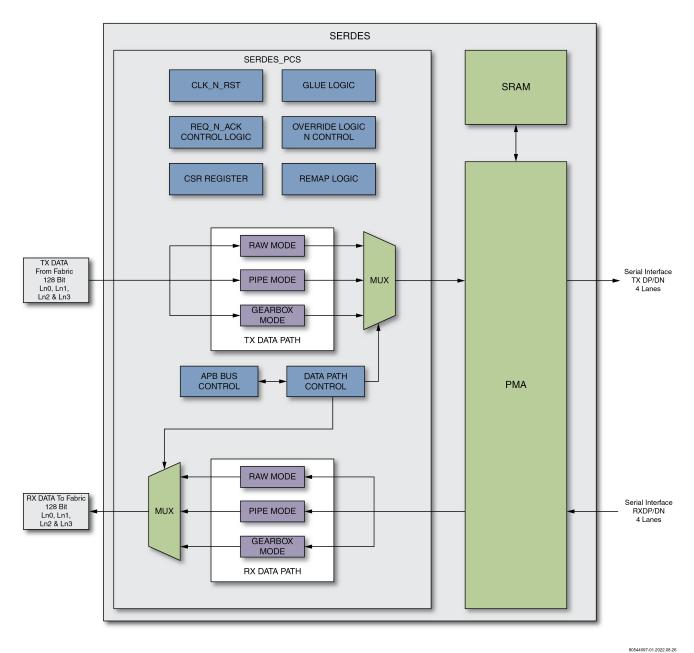

The following figure shows a high-level block diagram of the PCS and the RX/TX data multiplexing.

Figure 6: PCS Modes

**Preliminary Data**

## **PCS** Features

- 16/20/32/40/64/128 bit FPGA data path support

- PCIe protocol via the PIPE specification for implementation of a soft PCIE controller in the fabric:

- 40-bit internal data path support for 8b/10b encoder path for PCIE Gen1/Gen2

- Comma detection and byte/word alignment only for PCIe protocol 8b/10B alignment

- 32-bit internal data path support for 128/130b encoder/decoder for PCle Gen3/Gen4

- Receive elastic FIFO is only for PIPE mode for clock compensation

- Support for bypassing the PCS for hard IP such as Ethernet Controller in the fabric

- Support for 66b/64b CAUI gearbox in both synchronous and asynchronous mode.

- Support for 67b/64b gearbox in synchronous mode only

- Protocols supported by the PMA via raw mode include:

- Ethernet 1G/10G/25G/50G/100G/XAUI

- CPRI

- JESD204A/B/C

- SyncE

- Interlaken

- The PCS SerDes supports lane bonding up to 16 lanes using a quad as the basic lane bonding block

## PCS SerDes Block Diagram

This section outlines the high-level hardware architecture block diagram of a quad lane SerDes (figure below). The PCS SerDes IP consists of the following main functional blocks:

- PCS (transmitter and receiver)

- PMA (quad SerDes)

Figure 7: Quad Transmit/Receive Path

## Reference Clock Sharing

The figure below details sharing the reference clock between quads. The reference clocks can only be shared within a single ACXIP and must be within a single subsystem (ETHERNET\_0, ETHERNET\_1, or PCIE\_1). An AXCIP is a configuration file created in ACE defining an IP configuration such as SerDes.

47418853-02.2022.08.31

Figure 8: Reference Clock Sharing

The following table details which lanes belong to each subsystem. Reference clock sharing is limited to lanes within a subsystem.

**Table 11: Reference Clock Sharing Table**

| Lanes | Subsystem  | Reference Clock  |

|-------|------------|------------------|

| 3:0   | ETHERNET_0 | SRDS_N6_REFCLK_P |

| 7:4   | ETHERNET_0 | SRDS_N7_REFCLK_P |

| 11:8  | ETHERNET_1 | SRDS_N4_REFCLK_P |

| 15:12 | ETHERNET_1 | SRDS_N5_REFCLK_P |

| 19:16 | PCIE_1     | SRDS_N0_REFCLK_P |

| 23:20 | PCIE_1     | SRDS_N1_REFCLK_P |

| Lanes | Subsystem | Reference Clock  |

|-------|-----------|------------------|

| 27:24 | PCIE_1    | SRDS_N2_REFCLK_P |

| 31:28 | PCIE_1    | SRDS_N3_REFCLK_P |

## **PCS Transmit Architecture**

The transmitter consists of the following four data paths. Each data path supports a particular encoding scheme which caters to a set of protocols.

- Transmit mux logic

- 8b/10b encoding path (PCle Gen1 and Gen 2)

- 128/130b encoding path (PCIe Gen3 and Gen 4)

- Transmit gearboxing (66b/64b and 67b/64b)

- PCS transmit direct path (16/20/32/40/64/128 bit)

## Transmit MUX Logic

The transmit MUX logic block performs the mode-dependent bit multiplexing. The supported modes are:

- Gearboxing

- PIPE (32 bit)

- Raw (128 bit)

- PRBS Generator

#### 8b/10b Encoder

The 8b/10b encoder generates 10-bit code groups from 8-bit data and single-bit control input. The encoder uses the code group mapping specified in IEEE 802.3 clause 36. If the fabric interface uses a 32-bit data path, then four 8b/10b encoders are cascaded to produce a 40-bit code group output to the PMA for serialization. The 10-bit encoded output  $tx_{dataout[9:0]}$  maps to bits  $\{jhgf iedcba\}$  per the labeling used in IEEE 802.3-2005 clause 36. The encoder operates with four-byte data widths.

This block supports PCIe Gen1 and Gen2 in PIPE mode.

#### 128b/130b Encoder Path

The 128b/130b encoder is specifically targeted at PCIe gen3/gen4. The interface is compliant with PIPE 5.1.

## PCS Receive Architecture

The receiver consists of the following four data paths. Each data path supports a particular encoding scheme which caters to a set of protocols.

- · Receive demux logic

- 8b/10b decoding (PCIe Gen1 and Gen 2)

- 128/130b decoding (PCle Gen3-Gen5)

- 64b/66b and 64b/67b Gearboxing

- PCS receive direct path

- PRBS checker

## Receive DeMUX logic

The receive deMUX logic block performs the mode-dependent bit demultiplexing. The supported modes are:

- Gearboxing (66b/67b)

- PIPE (32-bit)

- Raw (128 bit)

#### 8b/10b Decoder Path

This path is used for implementing 8b/10b decoder-related receive path blocks. This path contains the following blocks:

- Comma detect and symbol alignment

- 8b/10b decoder

- Receive 8b/10b elastic buffer

#### **Comma Detect and Symbol Alignment**

The symbol alignment block can be configured to support a variety of standards by programming various characters. Currently supported standard are PCIe (Gen 1/Gen 2).

Symbol alignment is performed in automatic alignment mode only, using alignment and sequence characters for identifying the correct symbol boundary in the received data-stream. Attributes for alignment and sequence detect symbols are specified to be 10 bits wide. This block offers a programmable comma pattern with sequence options to fit any protocol or custom scenario.

#### 8b/10b Decoder

The 8b/10b decoder generates 8-bit code groups and 1-bit control from 10-bit encoded data. It uses the code group mapping specified in IEEE 802.3 clause 36. If the fabric interface uses a 32-bit data path, then four 8B/10B decoders are cascaded to produce 32-bit data to the fabric. The decoder handles various error conditions reported on a per byte lane basis.

The running disparity should change polarity when a 6-bit or 4-bit code word with an unequal number of 0s and 1s is received. If reception of a 6-bit or 4-bit code word with an unequal number of 0s and 1s does not change the running disparity, a disparity error is asserted for the corresponding byte.

Any 10-bit code word that is not present in tables 36-1, 36-2 of the IEEE 802.3-2005 specification are considered as an invalid code word. In addition, the 11 code words corresponding to the K characters are programmable to be flagged as invalid code words. If the 10-bit code word happens to be present in tables 36-1 or 36-2, but corresponds to the wrong column (per the currently running disparity calculation), a wrong column indication is asserted.

Disparity and code errors are not mutually exclusive. However, code error and wrong column indication are mutually exclusive. For PCle, if a code error and disparity error is detected on the same byte, the pipe rxstatus is encoded to indicate a code error.

#### Receive 8b/10b Elastic Buffer

The 8b/10b elastic FIFO is used to synchronize the received data from the PMA-recovered clock to a system clock or local clock (typically transmit clock) in the 8b/10b encoding environment. This block operates in a 40-bit mode and provides a very generic programmable skip character detection.

The elastic FIFO compensates for the frequency offset by adding or deleting pre-configured skip characters from the received data stream. The elastic FIFO provides an indication that skip characters were added or deleted to the downstream logic. For PCIe, the elastic FIFO also includes the appropriate status encoding to indicate add /delete operation.

#### 128b/130b Decoder Path

The 128b/130b decoder path is specifically targeted at PCIe Gen3-Gen4. The interface is compliant to PIPE 5.0 and consists of a block synchronizer and receives the Gen3-Gen4 elastic buffer.

#### **Block Synchronizer**

PMA parallelization occurs at arbitrary word boundaries. Consequently, the parallel data from the receive PMA CDR must be realigned to meaningful character boundaries. The PCI Express 4.0 base specification outlines that the data is formed using 130-bit blocks, with the exception of SKP blocks. A SKP ordered set can be 66, 98, 130, 162, or 194 bits long. The block synchronizer searches for the electrical idle exit sequence ordered set or skips (SKP) ordered set to identify the correct boundary for the incoming stream and to achieve block alignment. The block is realigned to the new block boundary following the receipt of a SKP ordered set, as it can be of variable length.

#### Receive Gen3-Gen5 Elastic Buffer

This elastic buffer compensates for small clock frequency differences between the recovered clock and the local clock domains by inserting or removing SKP symbols in the data stream to keep the FIFO from going empty or full respectively for PCIe Gen3/4/5 systems.

The PCI Express 4.0 base specification defines that the SKP ordered set (OS) can be 66, 98, 130, 162, or 194 bits long. The SKP OS has the following fixed bits: 2-bit Sync, 8-bit SKP END, and a 24-bit LFSR for a total of 34 bits. This block adds or deletes the 4 SKP characters (32 bits) to keep the FIFO from going empty or full, respectively. If the FIFO is nearly full, it deletes the 4 SKP characters (32 bits) by disabling write whenever a SKP is found. If the FIFO is nearly empty, the design waits for a SKP OS to start, then stops reading the data from the FIFO, and inserts a SKP in the outgoing data.

## 64b/66b and 64b/67b Bit Gearboxing

The receive gearbox is used to adapt the PMA data width to the width of the PCS-fabric interface. It supports different ratios (PMA interface width: fabric interface width) such as 64b/66b and 64b/67b. There are two modes supported:

- Synchronous mode Supported for both 66 and 67 bit mode. The gearbox stalls the data throughput by de-asserting data\_valid for one clock cycle to match the ratio. The fabric receives a data\_valid signal along with the data which must be monitored.

- Asynchronous mode Supported only for 66 bit mode. The gearbox provides the data on each clock cycle

of the receive clock. Data is valid on every clock cycle in asynchronous mode.

#### Gearbox Mode

The transmit gearbox is used to adapt the PCS data width to the width of the PCS-PMA interface. The gearbox supports different ratios (fabric interface width: PMA interface width) such as 66b/64b (synchronous and asynchronous) and 67b/64b (synchronous). This block can either operate seamlessly based on two clocks with different rates 66b/64b, or operate on a single clock with wait states added during the gearbox wrap around time for 67b/64b (synchronous mode).

## Gearboxing Implementation

#### **Clocking and Usage**

The following figure shows the clock and data path for a gearboxing implementation in the PCS for a quad.

Figure 9: Gearbox Implementation

# Gearbox Ports Mapping

Table 12: Gearbox Transmit Data Port Mapping

| Port             | Gearbox Port Name/Usage             | Width |

|------------------|-------------------------------------|-------|

| i_tx_data[66:0]  | 67/66 bit data input.               | 67    |

| i_tx_data[67]    | Enable 66-bit asynchronous gearbox. | 1     |

| i_tx_data[68]    | Enable 66-bit synchronous gearbox.  | 1     |

| i_tx_data[69]    | data valid.                         | 1     |

| i_tx_data[70]    | Enable 67-bit synchronous gearbox.  | 1     |

| i_tx_data[77:71] | 7-bit synchronous counter.          | 7     |

**Table 13: Gearbox Receive Data Port Mapping**

| Port            | Gearbox Port Name/Usage                        | Width |

|-----------------|------------------------------------------------|-------|

| o_rx_data[66:0] | 67/66 bit output data.                         | 67    |

| o_rx_data[67]   | Indicates skip missed for synchronous gearbox. | 1     |

| o_rx_data[68]   | Rx data valid.                                 | 1     |

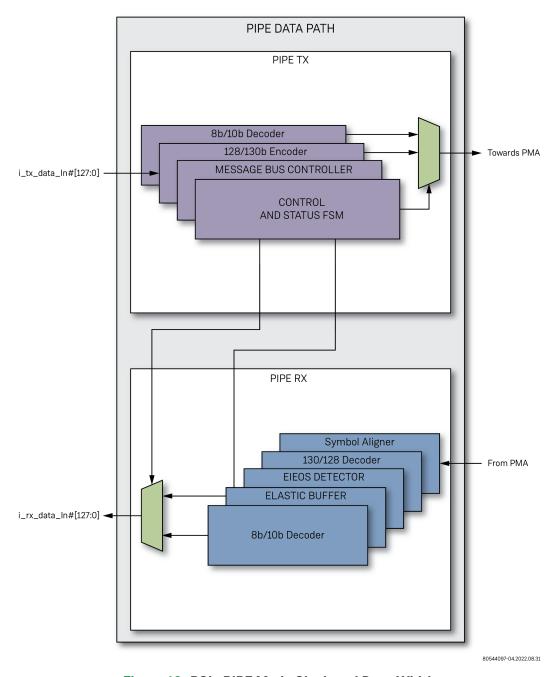

## PIPE Mode

The PIPE mode enables access to the PCS PIPE 5.1-compliant interface. The PCS layer supports PCIe Gen4 in PIPE mode using a soft controller in the fabric. The following diagram details the various supported combinations of clock and data width when the PCS supports PCIe.

Figure 10: PCIe PIPE Mode Clock and Data Width

## Rates

The PCS layer includes the glue logic to switch the PMA data width to 32-bit mode and program the final rate bits for PCIe gen3/gen4 operation. The following table lists the various supported combinations of clock and data width when the PCS supports PCIe.

Table 14: PCIE Generation with PCLK Rates and Supported Data Widths

| PCIe Mode      | PCLK     | PMA Data Width |

|----------------|----------|----------------|

| 2.5 Gbps Gen1  | 62.5 MHz | 40 bits        |

| 5.0 Gbps Gen2  | 125 MHz  | 40 bits        |

| 8.0 Gbps Gen3  | 250 MHz  | 22 hita        |

| 16.0 Gbps Gen4 | 500 MHz  | 32 bits        |

# PIPE Ports Mapping

Refer to PIPE spec 5.1 for further details.

**Table 15: PIPE Mode Transmit Data Port Mapping**

| Port             | PIPE Port Name | Width | Description                                                                                                                                                                                                                                                              |

|------------------|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i_tx_data[31:0]  | TxData         | 32    | Transmit PIPE Data.                                                                                                                                                                                                                                                      |

| i_tx_data[70:67] | TxElecidle     | 4     | Transmit electrical idle forces tx_p/n to idle state.                                                                                                                                                                                                                    |

| i_tx_data[72:71] | TxSubsample    | 2     | Not Supported.                                                                                                                                                                                                                                                           |

| i_tx_data[73]    | TxBeaconEnable | 1     | Enable transmit of a Beacon. 1 Beacon transmit is enabled, 0 Beacon transmit is disabled.                                                                                                                                                                                |

| i_tx_data[77:74] | TxDataK        | 4     | These signals indicate the type of characters on the TxData bus. A 1'b0 indicates a data character; while a 1'b1 indicates a control character.  i_tx_data[74] - TxData[7:0]  i_tx_data[75] - TxData[15:8]  i_tx_data[76] - TxData[23:16]  i_tx_data[77] - TxData[31:24] |

| i_tx_data[78]    | TxDataValid    | 1     | TxDataValid qualifies the data on the TxData bus and is active high.                                                                                                                                                                                                     |

| i_tx_data[80:79] | TxSyncHeader   | 2     | For Gen3 operation. Specifies the receive block type: 2'b01: Ordered Set Block 2'b10: Data Block These signals can be grounded if the design is not targeting Gen3.                                                                                                      |

Table 16: PIPE Mode Transmit Data Port Mapping (cont.)

| Port               | PIPE Port Name      | Width | Description                                                                                                                                                                                                                                                                                         |

|--------------------|---------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i_tx_data[81]      | TxStartBlock        | 1     | Allows the MAC to tell the PHY the starting byte for the 128b block, active high. The starting byte for a 128b block must always start with byte 0 of the data interface.                                                                                                                           |

| i_tx_data[82]      | TxCompliance        | 1     | Used when transmitting the PCI Express compliance pattern, active high. This signal is sampled on TxDataValid.                                                                                                                                                                                      |

| i_tx_data[83]      | SRISEnable          | 1     | Not Supported.                                                                                                                                                                                                                                                                                      |

| i_tx_data[91:84]   | M2PMessageBus       | 8     | The MAC multiplexes command, and required address, and any required data for sending read and write requests to access PHY PIPE registers and for sending read completion responses and write ack responses to PHY initiated requests. Refer PIPE spec 5.1 message bus section for full definition. |

| i_tx_data[92]      | RXEiDetectDisable   | 1     | Not Supported.                                                                                                                                                                                                                                                                                      |

| i_tx_data[93]      | TxCommonModeDisable | 1     | Not Supported.                                                                                                                                                                                                                                                                                      |

| i_tx_data[94]      | PclkChangeAck       | 1     | Not Supported.                                                                                                                                                                                                                                                                                      |

| i_tx_data[95]      | AsyncPowerChangeAck | 1     | Not Supported.                                                                                                                                                                                                                                                                                      |

| i_tx_data[96]      | TxDetectrx/Loopback | 1     | Used to tell the PHY to begin a receiver detection operation or to begin loopback, active high.                                                                                                                                                                                                     |

| i_tx_data[100:97]  | PowerDown           | 4     | Power the transceiver up or down. Power states:  4'b0000 - P0 normal operation.  4'b0001 - P0 low recovery time latency, power saving state.  4'b0010 - P1 longer recovery time latency, lower power state.  4'b0011 - P2 lowest power state.  4'b0100 - PD (full power down).                      |

| i_tx_data[103:101] | TxRate              | 3     | Control the link symbol rate:  3 'b000 - 2.5 GB/s symbol rate.  3 'b001 - 5.0 GB/s symbol rate.  3 'b010 - 8.0 GB/s symbol rate.  3 'b011 - 16.0 GB/s symbol rate.                                                                                                                                  |

| i_tx_data[106:105] | Width               | 2     | Fixed to 32 bit.                                                                                                                                                                                                                                                                                    |

# Speedster7t SerDes User Guide (UG099)

| Port               | PIPE Port Name | Width | Description                        |

|--------------------|----------------|-------|------------------------------------|

| i_tx_data[111:107] | PclkRate       | 5     | Not Supported.                     |

| i_tx_data[112]     | RxStandby      | 1     | Not Supported.                     |

| i_tx_data[113]     | MsgbusRstn     | 1     | Reset the message bus, active low. |

Table 17: PIPE Mode Receive Data Port Mapping

| Port             | PIPE Port Name  | Width | Description                                                                                                                                                                                                                                                                                               |

|------------------|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| o_rx_data[31:0]  | RxData          | 32    | Received PIPE data.                                                                                                                                                                                                                                                                                       |

| o_rx_data[67-32] | Unused.         | 36    | Unused.                                                                                                                                                                                                                                                                                                   |

| o_rx_data[68]    | RxValid         | 1     | Indicates symbol lock and valid data on RxData and RxDataK and further qualifies RxDataValid when used. Active high.                                                                                                                                                                                      |