# Speedster7t Power Estimator User Guide (UG093)

**Speedster FPGAs**

**Preliminary Data**

**Preliminary Data**

# Copyrights, Trademarks and Disclaimers

Copyright © 2020 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedcore, Speedster, and ACE are trademarks of Achronix Semiconductor Corporation in the U.S. and/or other countries All other trademarks are the property of their respective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

#### **Preliminary Data**

This document contains preliminary information and is subject to change without notice. Information provided herein is based on internal engineering specifications and/or initial characterization data.

#### Achronix Semiconductor Corporation

2903 Bunker Hill Lane Santa Clara, CA 95054 USA Website: www.achronix.com

E-mail : info@achronix.com

# **Table of Contents**

| Chapter - 1: Introduction                                           | 5  |

|---------------------------------------------------------------------|----|

| Chapter - 2: System Requirements and Setup                          | 6  |

| Chapter - 3: Speedster7t Power Estimator UG Power Central Worksheet |    |

| System Variables                                                    | 8  |

| Thermal Analysis                                                    |    |

| Power Usage                                                         |    |

| Dynamic Power                                                       | 10 |

| Current by Power Supply                                             |    |

| Power Usage Summary                                                 | 12 |

| Chapter - 4: Speedster7t Supporting Estimator Worksheets            | 14 |

| RLB Worksheet                                                       |    |

| BRAM Worksheet                                                      | 15 |

| LRAM Worksheet                                                      |    |

| MLP Worksheet                                                       | 18 |

| NoC Worksheet                                                       | 18 |

| I/O Worksheet                                                       | 19 |

| SerDes Worksheet<br>Raw SerDes<br>Hard IP Based SerDes              | 22 |

| PLL Worksheet                                                       | 23 |

| Clock Worksheet                                                     | 24 |

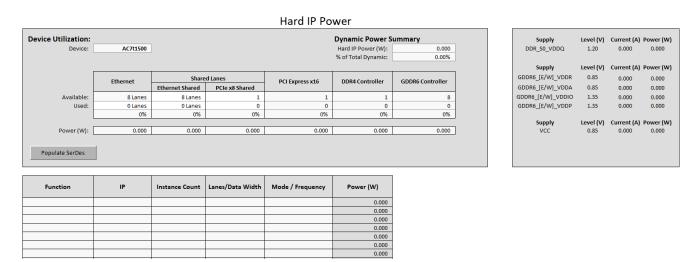

| Hard IP Worksheet<br>Shared Lanes<br>Populate SerDes                | 26 |

| Revision History                                                    | 27 |

|                                                                     |    |

# Chapter - 1: Introduction

The Achronix Speedster<sup>®</sup>7t Power Estimator tool provides a platform to calculate the power requirements for the Achronix 7nm standalone FPGAs. This user guide gives a detailed overview of the thermal and power needs depending on the device, environment and utilization of components in the design. The power estimator tool can be used at any stage of the design process to obtain an estimate of the total power dissipation from the device. However, it is generally used early on, prior to actual design activity, to obtain a first-cut estimate of the power needs so that board regulators and thermal solutions can be designed accordingly and power integrity analyses done appropriately. This estimate could then be compared with post-implementation results using the ACE-generated power report.

The Achronix Speedster Power Estimator is a spreadsheet that takes parameters as user inputs to estimate the total power dissipated. This includes device characteristics, thermal characteristics and utilization of IP resources such as BRAMs, LRAMs, MLPs, LUTs, etc. To obtain a good estimate of the design's power profile, the user is required to enter a realistic estimate of the design utilization.

Since this estimator is used at a very early stage of the design process, it is probable that the user cannot yet account for all the worst-case scenarios while providing inputs to the tool, for example, junction temperature for static power measurement and toggle rate inputs for different modules. Even slight temperature variations, especially in the higher order, could result in significant changes in the static power while providing toggle rates not accounting for realistic worst cases could result in underestimating dynamic power. In order to cover for such cases, it is recommended that the user adds an additional guard band of 30% to the total power estimation when specifying power regulators for the board.

# Chapter - 2: System Requirements and Setup

The Achronix Speedcore Power Estimator tool is compatible with Microsoft Excel 2007 and later versions. By default, the spreadsheet's security setting disables macros when opened. These macros must be enabled in order to use this spreadsheet. This setting can be changed when opening the spreadsheet.

For Excel versions 2007 and 2010:

- 1. Opening the spreadsheet first displays a security warning banner. Click **Options...** to proceed.

- From the Microsoft Office Security Options popup window displaying "Security Alert Macro," select Enable this content followed by clicking OK to close the window.

For Excel versions 2013 and 2016:

- 1. Opening the spreadsheet first displays a protected view warning banner. Click **Enable Editing** to proceed.

- 2. Then a security warning banner displaying "Macros have been disabled." Click **Enable Content** to proceed.

# Chapter - 3: Speedster7t Power Estimator UG Power Central Worksheet

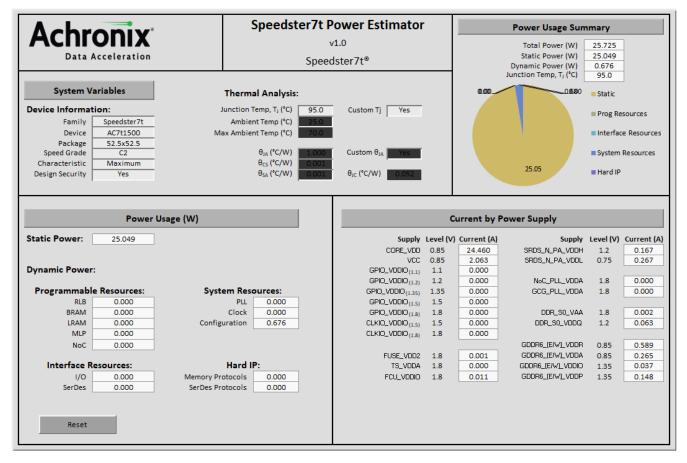

The central power estimator worksheet is the main worksheet of the estimator where the breakdown of various power dissipation components is displayed. It is divided into four sections: System Variables, Power Usage by Resource, Current by Power Supply and Power Usage Summary.

Figure 1: Power Central Worksheet

# System Variables

This section includes two parts: Device Information and Thermal Analysis.

| Yes   |

|-------|

|       |

|       |

|       |

| Yes   |

|       |

| 0.052 |

|       |

#### Figure 2: System Variables Section

### **Device Information**

The Device Information section allows the user to provide top-level device characteristics to be used in power calculations in the rest of the spreadsheet. It takes in the following input parameters to calculate power.

#### **Table 1: System Variables Input Parameters**

| Parameter      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Family         | Achronix Speedster7t device family.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Device         | Speedster7t device variant in the family.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Package        | Package dimensions of the chosen device                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Speed Grade    | This option allows the user to select the desired speed grade for the target device: C1/C2/C3. The operating voltage corresponding to these speed grades are as below: <ul> <li>C1 – 0.9V</li> <li>C2 – 0.85V</li> <li>C3 – 0.75V</li> </ul> <li>Note <ul> <li>C1 offers the fastest speed grade for the selected device under normal conditions</li> </ul></li>                                                                                                                        |

| Characteristic | <ul> <li>This option allows the user to select the device characteristics used for static power calculation:</li> <li>Typical – power dissipation characteristics of a device considered to be the median in the device power distribution.</li> <li>Maximum – power dissipation characteristics of the worst-case device in the power distribution.</li> <li>In order to account for worst-case process variation, it is recommended to set the characteristics to Maximum.</li> </ul> |

| Parameter          | Description                                                                                                                                                                       |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design<br>Security | This option allows the user to enable or disable design security feature, i.e, if the application requires fuse blowing (e,g., programming encryption fuses for design security). |

### **Thermal Analysis**

This section allows for device thermal characteristics to be calculated to:

- Ensure that device maximum junction temperature specifications are not exceeded.

- Appropriate thermal solutions (heat sinks and fans) can be devised.

- Provide an output junction temperature that allows for static and total power calculations to help drive board regulator solutions.

The following input parameters can be modified based upon the end requirements.

#### **Table 2: Thermal Analysis Input Parameters**

| Parameter                                              | Description                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lunction Tomporature T (°C)                            | The junction or operating temperature refers to the temperature of the silicon die within the package of the device when the device is powered. $T_J = T_A + (P \times \Theta_{JA})$ where $T_J$ is the Junction temperature in <sup>o</sup> C, $T_A$ is the ambient temperature in <sup>o</sup> C, P             |

| Junction Temperature, T <sub>J</sub> ( <sup>o</sup> C) | is the total power dissipated in Watts and $\Theta_{JA}$ is the junction-to-ambient thermal resistance in <sup>o</sup> C/W.                                                                                                                                                                                       |

| Custom T <sub>J</sub>                                  | Allows the user to enable/disable user-defined $T_J$ . When custom $T_J$ is disabled, the junction temperature is calculated based on the formula above and when enabled, the user has the choice to enter a predetermined value.                                                                                 |

| Ambient temperature, ( <sup>o</sup> C)                 | The ambient temperature refers to the temperature of the surrounding environment (typically air) when the device is powered. This field can only be accepted as an input if the custom $T_J$ option is disabled or set to 'No'.                                                                                   |

| Max Ambient temperature, ( <sup>o</sup> C)             | The maximum ambient temperature should be such that the junction temperature does not exceed the maximum allowed for the device. Refer to the datasheet for the temperature range supported by the target Speedster7t device.                                                                                     |

| Custom Θ <sub>JA</sub>                                 | When this option is enabled, it allows the user to enter a predetermined value for $\Theta_J_A$ keeping the other thermal resistance values unchanged. When disabled, the user is required to enter values for $\Theta_{JC}$ , $\Theta_{CS}$ and $\Theta_{SA}$ to have $\Theta_{JA}$ be calculated automatically. |

| Θ <sub>JA</sub> (°C/W)                                 | Junction-to-ambient thermal resistance. The user has the option to provide a custom value for this value or have it be calculated with the formula $\Theta_{JA} = \Theta_{JC} + \Theta_{CS} + \Theta_{SA}$ based on the option chosen for 'Custom $\Theta_{JA}$ '.                                                |

#### Speedster7t Power Estimator User Guide (UG093)

| Parameter              | Description                                                                                                  |

|------------------------|--------------------------------------------------------------------------------------------------------------|

| Θ <sub>JC</sub> (°C/W) | Junction-to-case thermal resistance. Only used when 'Custom $\Theta_{JA}$ ' is disabled or set to 'No'.      |

| Θ <sub>CS</sub> (°C/W) | Case-to-heat sink thermal resistance. Only used when 'Custom $\Theta_{JA}^{}$ ' is disabled or set to 'No'.  |

| Θ <sub>SA</sub> (°C/W) | Heat sink-to-ambient thermal resistance. Only used when 'Custom $\Theta_{JA}^{}$ is disabled or set to 'No'. |

### Power Usage

The Power Usage section presents the total power breakdown in terms of Static Power and Dynamic Power based on the resources.

### Static Power

Static power or standby power is the power dissipated when the device is in an unconfigured state after powerup. It depends on the device selected (die area), process characteristics, temperature and operating voltages.

### **Dynamic Power**

The dynamic or switching power dissipation is caused by switching activity inside the Speedster7t FPGA and is a function of switching frequency, operating voltage and load. This section gives a breakdown of the different power dissipation sources that contribute to the dynamic power in the device:

#### **Programmable Resources**

This section summarizes the power dissipated by the total RLBs, BRAMs, LRAMs, NOC and MLP components in the device. Each of these components has a separate worksheet for power calculation which will be explained in detail later in this document

#### **Interface Resources**

This section includes power dissipated by I/O and SerDes interfaces in the device. Each of these components has a separate worksheet for power calculation which will be explained in detail later in this document.

#### **System Resources**

This includes power dissipated by the total PLLs and clocks used in the design and also the configuration power. The configuration power is the total power consumed from initial power-up to user mode.

#### Hard IP

This section lists the power consumed by the hard IP used in the design. They are split into the following protocols accordingly.

#### Memory Protocols

This section includes the power consumed by the DDR and the GDDR6 controller subsystems.

#### SerDes Protocols

This section includes the power consumed by the other SerDes-based hard IP such as Ethernet and PCI Express. A more detailed review of the hard IP are addressed in the Hard IP worksheet later in this document

The Power Usage section also has a '**Reset**' option that enables the user to clear all user-defined inputs and from the spreadsheet and set the toggle rates to the default value.

|               | Power        | Usage (W)        |         |

|---------------|--------------|------------------|---------|

| Static Power: | 30.587       |                  |         |

| ·             |              | 4                |         |

| Dynamic Power | :            |                  |         |

| Programmable  | e Resources: | System Res       | ources: |

| RLB           | 0.000        | PLL              | 0.000   |

| BRAM          | 0.000        | Clock            | 0.000   |

| LRAM          | 0.000        | Configuration    | 0.676   |

| MLP           | 0.000        |                  |         |

| NoC           | 0.000        |                  |         |

|               |              |                  |         |

| Interface R   | esources:    | Hard II          | P:      |

| I/O           | 0.000        | Memory Protocols | 0.000   |

| SerDes        | 0.000        | SerDes Protocols | 0.000   |

|               |              |                  |         |

| Reset         |              |                  |         |

Figure 3: Power Usage by Resources

# Current by Power Supply

The Current by Power Supply section provides the user a breakdown of the total current that is the sum of both the static and dynamic current components used by each of the voltage rails present in the device. The voltage level corresponding to the voltage rails are also displayed.

| VCC         0.85         2.890         SRDS_N_PA_VDDL         0.75         0.374           GPIO_VDDIO (1.1)         1.1         0.000         NoC_PLL_VDDA         1.8         0.000           GPIO_VDDIO (1.2)         1.2         0.000         NoC_PLL_VDDA         1.8         0.000           GPIO_VDDIO (1.35)         1.35         0.000         GCG_PLL_VDDA         1.8         0.000           GPIO_VDDIO (1.5)         1.5         0.000         DDR_S0_VAA         1.8         0.002           GPIO_VDDIO (1.5)         1.5         0.000         DDR_S0_VDDQ         1.2         0.088           CLKIO_VDDIO (1.5)         1.5         0.000         DDR_S0_VDDQ         1.2         0.088           CLKIO_VDDIO (1.5)         1.8         0.000         DDR_S0_VDDQ         1.2         0.088           CLKIO_VDDIO (1.5)         1.8         0.000         DDR_S0_VDDQ         0.85         0.826           FUSE_VDD2         1.8         0.002         GDDR6_[E/W]_VDDA         0.85         0.372           TS_VDDA         1.8         0.000         GDDR6_[E/W]_VDDIO         1.35         0.052 | Supply            | Level (V) | Current (A) | Supply            | Level (V) | Current (A |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------|-------------|-------------------|-----------|------------|

| GPIO_VDDIO (1.1)       1.1       0.000       NoC_PLL_VDDA       1.8       0.000         GPIO_VDDIO (1.2)       1.2       0.000       NoC_PLL_VDDA       1.8       0.000         GPIO_VDDIO (1.35)       1.35       0.000       GCG_PLL_VDDA       1.8       0.000         GPIO_VDDIO (1.5)       1.5       0.000       DDR_S0_VAA       1.8       0.002         GPIO_VDDIO (1.8)       1.8       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.5)       1.5       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.8)       1.8       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.8)       1.8       0.000       DDR_S0_VDDQ       1.2       0.088         GDDR6_[E/W]_VDDR       0.85       0.826       0.372       0.052       0.052         TS_VDDA       1.8       0.000       GDDR6_[E/W]_VDDIO       1.35       0.052                                                                                                                                                                                                                     | CORE_VDD          | 0.85      | 34.262      | SRDS_N_PA_VDDH    | 1.2       | 0.234      |

| GPIO_VDDIO (1.2)       1.2       0.000       NoC_PLL_VDDA       1.8       0.000         GPIO_VDDIO (1.35)       1.35       0.000       GCG_PLL_VDDA       1.8       0.000         GPIO_VDDIO (1.5)       1.5       0.000       GCG_PLL_VDDA       1.8       0.000         GPIO_VDDIO (1.5)       1.5       0.000       DDR_S0_VAA       1.8       0.002         GLKIO_VDDIO (1.5)       1.5       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.5)       1.8       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.6)       1.8       0.000       DDR_S0_VDDQ       0.85       0.826         FUSE_VDD2       1.8       0.002       GDDR6_[E/W]_VDDA       0.85       0.372         TS_VDDA       1.8       0.000       GDDR6_[E/W]_VDDIO       1.35       0.052                                                                                                                                                                                                                                                                                                         | VCC               | 0.85      | 2.890       | SRDS_N_PA_VDDL    | 0.75      | 0.374      |

| GPIO_VDDIO (1.35)       1.35       0.000       GCG_PLL_VDDA       1.8       0.000         GPIO_VDDIO (1.5)       1.5       0.000       DDR_S0_VAA       1.8       0.002         GPIO_VDDIO (1.5)       1.5       0.000       DDR_S0_VAA       1.8       0.002         CLKIO_VDDIO (1.5)       1.5       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.5)       1.8       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.8)       1.8       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.8)       1.8       0.000       DDR_S0_VDDQ       0.85       0.826         FUSE_VDD2       1.8       0.002       GDDR6_[E/W]_VDDA       0.85       0.372         TS_VDDA       1.8       0.000       GDDR6_[E/W]_VDDIO       1.35       0.052                                                                                                                                                                                                                                                                                                           | GPIO_VDDIO (1.1)  | 1.1       | 0.000       |                   |           |            |

| GPIO_VDDIO (1.5)       1.5       0.000       DDR_S0_VAA       1.8       0.002         GPIO_VDDIO (1.8)       1.8       0.000       DDR_S0_VAA       1.8       0.002         CLKIO_VDDIO (1.5)       1.5       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.8)       1.8       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.8)       1.8       0.000       GDDR6_[E/W]_VDDR       0.85       0.826         FUSE_VDD2       1.8       0.002       GDDR6_[E/W]_VDDA       0.85       0.372         TS_VDDA       1.8       0.000       GDDR6_[E/W]_VDDIO       1.35       0.052                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | GPIO_VDDIO (1.2)  | 1.2       | 0.000       | NoC_PLL_VDDA      | 1.8       | 0.000      |

| GPIO_VDDIO (1.8)       1.8       0.000       DDR_S0_VAA       1.8       0.002         CLKIO_VDDIO (1.5)       1.5       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.8)       1.8       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.8)       1.8       0.000       GDDR6_[E/W]_VDDR       0.85       0.826         FUSE_VDD2       1.8       0.002       GDDR6_[E/W]_VDDA       0.85       0.372         TS_VDDA       1.8       0.000       GDDR6_[E/W]_VDDIO       1.35       0.052                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GPIO_VDDIO (1.35) | 1.35      | 0.000       | GCG_PLL_VDDA      | 1.8       | 0.000      |

| CLKIO_VDDIO (1.5)       1.5       0.000       DDR_S0_VDDQ       1.2       0.088         CLKIO_VDDIO (1.8)       1.8       0.000       GDDR6_[E/W]_VDDR       0.85       0.826         FUSE_VDD2       1.8       0.002       GDDR6_[E/W]_VDDA       0.85       0.372         TS_VDDA       1.8       0.000       GDDR6_[E/W]_VDDIO       1.35       0.052                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GPIO_VDDIO (1.5)  | 1.5       | 0.000       |                   |           | -          |

| CLKIO_VDDIO (1.8)       1.8       0.000       GDDR6_[E/W]_VDDR       0.85       0.826         FUSE_VDD2       1.8       0.002       GDDR6_[E/W]_VDDA       0.85       0.372         TS_VDDA       1.8       0.000       GDDR6_[E/W]_VDDIO       1.35       0.052                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GPIO_VDDIO (1.8)  | 1.8       | 0.000       | DDR_S0_VAA        | 1.8       | 0.002      |

| GDDR6_[E/W]_VDDR         0.85         0.826           FUSE_VDD2         1.8         0.002         GDDR6_[E/W]_VDDA         0.85         0.372           TS_VDDA         1.8         0.000         GDDR6_[E/W]_VDDIO         1.35         0.052                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLKIO_VDDIO (1.5) | 1.5       | 0.000       | DDR_S0_VDDQ       | 1.2       | 0.088      |

| FUSE_VDD2         1.8         0.002         GDDR6_[E/W]_VDDA         0.85         0.372           TS_VDDA         1.8         0.000         GDDR6_[E/W]_VDDIO         1.35         0.052                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CLKIO_VDDIO (1.8) | 1.8       | 0.000       |                   |           |            |

| TS_VDDA 1.8 0.000 GDDR6_[E/W]_VDDIO 1.35 0.052                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |           |             | GDDR6_[E/W]_VDDR  | 0.85      | 0.826      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FUSE_VDD2         | 1.8       | 0.002       | GDDR6_[E/W]_VDDA  | 0.85      | 0.372      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TS_VDDA           | 1.8       | 0.000       | GDDR6_[E/W]_VDDIO | 1.35      | 0.052      |

| FCU_VDDIO 1.8 0.015 GDDR6_[E/W]_VDDP 1.35 0.208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FCU_VDDIO         | 1.8       | 0.015       | GDDR6_[E/W]_VDDP  | 1.35      | 0.208      |

| FC0_VDDIO 1.8 0.015 GDDR6_[E/W]_VDDP 1.35 0.208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FCU_VDDIO         | 1.8       | 0.015       | GDDR6_[E/W]_VDDP  | 1.35      | 0.208      |

Figure 4: Current by Power Supply

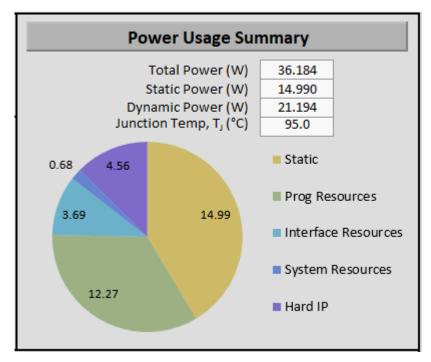

# Power Usage Summary

This section provides a summary of all the power dissipation components such as the Total Power (W), Static Power (W) and Dynamic Power (W) and their distribution across various device resources on a pie chart. This provides a pictorial representation of the percentage contribution of each of these resources towards the total power dissipated by the device.

Figure 5: Power Usage Summary

# Chapter - 4: Speedster7t Supporting Estimator Worksheets

# **RLB Worksheet**

The RLB power worksheet provides a summary of the total RLB utilization that comprises the LUTs, DFFs and ALUs in the design versus the available resource count in the device. The worksheet also lists the total dynamic power consumed by these RLB logic components in the design. Based on the values entered by the user in the following fields, the worksheet computes the total dynamic power as a sum of the total instance and interconnect power of all the RLB logic used and the corresponding dynamic current for the chosen CORE\_VDD rail.

| RLB Power               |           |      |        |                     |            |         |  |

|-------------------------|-----------|------|--------|---------------------|------------|---------|--|

| Device Utilization:     |           |      |        | Dynamic Powe        | er Summary | Supply  |  |

| Device:                 | AC7t1500  |      |        | RLB Power (W):      | 0.000      | CORE_VD |  |

| Availability and Usage: |           |      |        | % of Total Dynamic: | 0.00%      |         |  |

|                         | Available | Used | Used % |                     |            |         |  |

| 6-LUTs:                 | 691,200   | 0    | 0%     |                     |            |         |  |

| DFFs:                   | 1,382,400 | 0    | 0%     |                     |            |         |  |

| 8-bit ALUs:             | 172,800   | 0    | 0%     |                     |            |         |  |

|                         |           |      |        |                     |            |         |  |

|                         |           |      |        |                     |            |         |  |

| Function | LUT Count | DFF Count | ALU Count | Clock<br>(MHz) | Toggle Rate | Fanout | Instance<br>Power (W) | Interconnect<br>Power (W) |

|----------|-----------|-----------|-----------|----------------|-------------|--------|-----------------------|---------------------------|

|          |           |           |           |                | 12.5%       | Medium | 0.000                 | 0.000                     |

|          |           |           |           |                | 12.5%       | Medium | 0.000                 | 0.000                     |

|          |           |           |           |                | 12.5%       | Medium | 0.000                 | 0.000                     |

|          |           |           |           |                | 12.5%       | Medium | 0.000                 | 0.000                     |

|          |           |           |           |                | 12.5%       | Medium | 0.000                 | 0.000                     |

|          |           |           |           |                | 12.5%       | Medium | 0.000                 | 0.000                     |

|          |           |           |           |                | 12.5%       | Medium | 0.000                 | 0.000                     |

|          |           |           |           |                | 12.5%       | Medium | 0.000                 | 0.000                     |

|          |           |           |           |                | 12.5%       | Medium | 0.000                 | 0.000                     |

#### Figure 6: RLB Power Worksheet

#### Table 3: RLB Power Worksheet Fields

| Name         | Description                                                                                 |

|--------------|---------------------------------------------------------------------------------------------|

| Input Fields |                                                                                             |

| Function     | Description about the functionality/module associated with the LUT. This entry is optional. |

| LUT Count    | The number of LUTs used in the functions/modules of the design.                             |

| DFF Count    | The total register count used in the functions/modules of the design.                       |

| ALU Count    | The total number of ALUs used in the functions/modules of the design                        |

| Clock (MHz)  | The clock frequency associated with the LUTs/registers in that portion of the circuitry.    |

#### Speedster7t Power Estimator User Guide (UG093)

| Name                      |             | Description                                                                                                                                                                      |                                                                                                                                       |  |  |  |  |  |

|---------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Toggle rate               |             |                                                                                                                                                                                  | gic or data toggles on each clock cycle. More information on how found in the application note <i>Measuring Accurate Toggle Rates</i> |  |  |  |  |  |

|                           |             | The average number of fanout nets driven by the LUTs, ALUs and registers. The values are very ow, low, medium, high and very high and the corresponding fanout limits are        |                                                                                                                                       |  |  |  |  |  |

|                           | Option      | Fanout                                                                                                                                                                           |                                                                                                                                       |  |  |  |  |  |

| Fanout                    | very low    | 1 to 2                                                                                                                                                                           |                                                                                                                                       |  |  |  |  |  |

|                           | low         | 3 to4                                                                                                                                                                            |                                                                                                                                       |  |  |  |  |  |

|                           | medium      | 5 to 8                                                                                                                                                                           |                                                                                                                                       |  |  |  |  |  |

|                           | high        | 9 to 12                                                                                                                                                                          |                                                                                                                                       |  |  |  |  |  |

|                           | very high   | greater than 12                                                                                                                                                                  |                                                                                                                                       |  |  |  |  |  |

| Calculated Fields         |             |                                                                                                                                                                                  |                                                                                                                                       |  |  |  |  |  |

| Instance Power<br>(W)     |             | Calculation of the total power used by the LUTs, ALUs and registers for a particular function /module. These values are then summed to provide the total in the summary section. |                                                                                                                                       |  |  |  |  |  |

| Interconnect<br>Power (W) | Total dynam | ic power contribute                                                                                                                                                              | d by the interconnect to/from LUTs, ALUs and registers                                                                                |  |  |  |  |  |

# **BRAM Worksheet**

The BRAM worksheet summarizes the total BRAMs used as a percentage of the total available BRAMs. It also shows the sum of instance and interconnect power as the total dynamic power dissipation from BRAM usage based on the user-specified inputs and highlights it as a percentage of the total dynamic power. This worksheet also shows the corresponding total dynamic current for the chosen CORE\_VDD rail.

#### **BRAM Power**

| <b>Device Utilization:</b><br>Device:<br>Available BRAMs:<br>Used BRAMs: | AC7t1500<br>2,560<br>0 | 0%               |          | BRAM Po                  | <b>nic Powe</b><br>wer (W):<br>Dynamic: | r Summary<br>0.000<br>0.00% | ]                        |                | Supply<br>CORE_VDD    | Level (V)<br>0.75         | Current (A)<br>0.000 | Power (W)<br>0.000 |

|--------------------------------------------------------------------------|------------------------|------------------|----------|--------------------------|-----------------------------------------|-----------------------------|--------------------------|----------------|-----------------------|---------------------------|----------------------|--------------------|

| Function                                                                 | BRAM<br>Count          | Mode             | Data Org | Port A<br>Clock<br>(MHz) | Toggle<br>Rate                          | Data Org                    | Port B<br>Clock<br>(MHz) | Toggle<br>Rate | Instance<br>Power (W) | Interconnect<br>Power (W) |                      |                    |

|                                                                          |                        | Simple Dual Port | x72      |                          | 25.0%                                   | x72                         |                          | 25.0%          | 0.000                 | 0.000                     | 1                    |                    |

|                                                                          |                        | Simple Dual Port | x72      |                          | 25.0%                                   | x72                         |                          | 25.0%          | 0.000                 | 0.000                     | 1                    |                    |

|                                                                          |                        | Simple Dual Port | x72      |                          | 25.0%                                   | x72                         |                          | 25.0%          | 0.000                 | 0.000                     | 1                    |                    |

|                                                                          |                        | Simple Dual Port | x72      |                          | 25.0%                                   | x72                         |                          | 25.0%          | 0.000                 | 0.000                     | 1                    |                    |

|                                                                          |                        | Simple Dual Port | x72      |                          | 25.0%                                   | x72                         |                          | 25.0%          | 0.000                 | 0.000                     |                      |                    |

|                                                                          |                        | Simple Dual Port | x72      |                          | 25.0%                                   | x72                         |                          | 25.0%          | 0.000                 | 0.000                     |                      |                    |

|                                                                          |                        | Simple Dual Port | x72      |                          | 25.0%                                   | x72                         |                          | 25.0%          | 0.000                 | 0.000                     |                      |                    |

|                                                                          |                        | Simple Dual Port | x72      |                          | 25.0%                                   | x72                         |                          | 25.0%          | 0.000                 | 0.000                     |                      |                    |

|                                                                          |                        | Simple Dual Port | x72      |                          | 25.0%                                   | x72                         |                          | 25.0%          | 0.000                 | 0.000                     |                      |                    |

|                                                                          |                        | Simple Dual Port | x72      |                          | 25.0%                                   | x72                         |                          | 25.0%          | 0.000                 | 0.000                     |                      |                    |

|                                                                          |                        | Simple Dual Port | x72      |                          | 25.0%                                   | x72                         |                          | 25.0%          | 0.000                 | 0.000                     |                      |                    |

|                                                                          |                        |                  |          |                          |                                         |                             |                          |                |                       |                           |                      |                    |

#### Figure 7: BRAM Power Worksheet

x72

25.0%

0.000

0.000

25.0%

x72

Simple Dual Port

#### **Table 4: BRAM Power Worksheet Fields**

| Name                      | Description                                                                                                                                                                                                  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Fields              |                                                                                                                                                                                                              |

| Function                  | Description about the functionality/module associated with the BRAM. This entry is optional.                                                                                                                 |

| BRAM<br>Count             | The number of BRAMs used in the function/module of the design.                                                                                                                                               |

| Mode                      | BRAM mode of operation is one of: ROM, simple dual port or FIFO. A simple dual-port RAM has one read port and one write port, ROMs are read-only RAMs, and FIFOs are the BRAMs used for FIFO implementation. |

| Data Org                  | The data width of BRAMs for ports A and B. The values range from ×4 to ×144.                                                                                                                                 |

| Clock (MHz)               | The clock frequencies for the BRAMs at ports A and B in those modules.                                                                                                                                       |

| Toggle Rate               | The percentage at which the BRAM toggles on each clock cycle on ports A and B.                                                                                                                               |

| Calculated Fi             | elds                                                                                                                                                                                                         |

| Instance<br>Power (W)     | Calculation of the total power used by the BRAMs for a particular function/module.                                                                                                                           |

| Interconnect<br>Power (W) | Total dynamic power contributed by the interconnect to/from BRAMs.                                                                                                                                           |

# LRAM Worksheet

The LRAM worksheet summarizes the total LRAMs used as a percentage of the total available LRAMs. It also shows the sum of instance and interconnect power as the total dynamic power dissipation from LRAM usage based on the user-specified inputs and highlights it as a percentage of the total dynamic power. This worksheet also shows the corresponding total dynamic current for the chosen CORE\_VDD rail.

#### LRAM Power

| Device Utilization: |          |    | Dynamic Powe        | er Summary | Supply   | Level (V) | Current (A) | Power (W) |

|---------------------|----------|----|---------------------|------------|----------|-----------|-------------|-----------|

| Device:             | AC7t1500 |    | LRAM Power (W):     | 0.000      | CORE_VDD | 0.75      | 0.000       | 0.000     |

| Available LRAMs:    | 2,560    |    | % of Total Dynamic: | 0.000      |          |           |             |           |

| Used LRAMs:         | 0        | 0% | ]                   |            |          |           |             |           |

| Function | LRAM Count | Clock<br>(MHz) | Toggle Rate | Instance Power<br>(W) | Interconnect<br>Power <mark>(</mark> W) |

|----------|------------|----------------|-------------|-----------------------|-----------------------------------------|

|          |            |                | 25.0%       | 0.000                 | 0.000                                   |

|          |            |                | 25.0%       | 0.000                 | 0.000                                   |

|          |            |                | 25.0%       | 0.000                 | 0.000                                   |

|          |            |                | 25.0%       | 0.000                 | 0.000                                   |

|          |            |                | 25.0%       | 0.000                 | 0.000                                   |

|          |            |                | 25.0%       | 0.000                 | 0.000                                   |

|          |            |                | 25.0%       | 0.000                 | 0.000                                   |

|          |            |                | 25.0%       | 0.000                 | 0.000                                   |

|          |            |                | 25.0%       | 0.000                 | 0.000                                   |

|          |            |                | 25.0%       | 0.000                 | 0.000                                   |

|          |            |                | 25.0%       | 0.000                 | 0.000                                   |

#### Figure 8: LRAM Power Worksheet

#### Table 5: LRAM Power Worksheet Fields

| Input Parameter           | Description                                                                                  |

|---------------------------|----------------------------------------------------------------------------------------------|

| Input Fields              |                                                                                              |

| Function                  | Description about the functionality/module associated with the LRAM. This entry is optional. |

| LRAM Count                | The number of LRAMs used in the function/module of the design.                               |

| Clock (MHz)               | The clock frequency for the LRAM used in this circuitry.                                     |

| Toggle Rate               | The percentage at which the LRAM data toggles on each clock cycle for that module.           |

| Calculated Fields         |                                                                                              |

| Instance Power (W)        | Calculation of the total power used by the LRAMs for a particular function/module.           |

| Interconnect Power<br>(W) | Total dynamic power contributed by the interconnects to/from LRAMs                           |

### MLP Worksheet

The MLP worksheet summarizes the total MLPs used as a percentage of the total available MLPs present in the device. It also shows the sum of instance and interconnect power as the total dynamic power dissipation from MLP usage based on the user-specified inputs and highlights it as a percentage of the total dynamic power. This worksheet also shows the corresponding total dynamic current for the chosen CORE\_VDD rail.

|                     | MLP Power |    |                     |            |  |          |           |             |           |

|---------------------|-----------|----|---------------------|------------|--|----------|-----------|-------------|-----------|

| Device Utilization: |           |    | Dynamic Powe        | er Summary |  | Supply   | Level (V) | Current (A) | Power (W) |

| Device:             | AC7t1500  |    | MLP Power (W):      | 0.000      |  | CORE_VDD | 0.75      | 0.000       | 0.000     |

| Available MLPs:     | 2,560     |    | % of Total Dynamic: | 0.00%      |  |          |           |             |           |

| Used MLPs:          | 0         | 0% |                     |            |  |          |           |             |           |

|                     |           |    |                     |            |  |          |           |             |           |

| Function | MLP Count | Clock<br>(MHz) | Toggle Rate | Instance Power<br>(W) | Interconnect<br>Power (W) |

|----------|-----------|----------------|-------------|-----------------------|---------------------------|

|          |           |                | 25.0%       | 0.000                 | 0.000                     |

|          |           |                | 25.0%       | 0.000                 | 0.000                     |

|          |           |                | 25.0%       | 0.000                 | 0.000                     |

|          |           |                | 25.0%       | 0.000                 | 0.000                     |

|          |           |                | 25.0%       | 0.000                 | 0.000                     |

|          |           |                | 25.0%       | 0.000                 | 0.000                     |

|          |           |                | 25.0%       | 0.000                 | 0.000                     |

|          |           |                | 25.0%       | 0.000                 | 0.000                     |

#### Figure 9: MLP Power Worksheet

#### Table 6: MLP Power Worksheet Fields

| Input Parameter           | Description                                                                                 |

|---------------------------|---------------------------------------------------------------------------------------------|

| Input Fields              |                                                                                             |

| Function                  | Description about the functionality/module associated with the MLP. This entry is optional. |

| MLP Count                 | The number of MLPs used in the function/module of the design.                               |

| Clock (MHz)               | The clock frequency for the MLP used in this circuitry.                                     |

| Toggle Rate               | The percentage at which the MLP data toggles on each clock cycle for that module.           |

| Calculated Fields         |                                                                                             |

| Instance Power (W)        | Calculation of the total power used by the MLPs for a particular function/module.           |

| Interconnect Power<br>(W) | Total dynamic power contributed by the interconnects to/from MLPs                           |

### NoC Worksheet

The network-on-chip (NoC) power worksheet summarizes the total dynamic power consumed by NoC resources specified by the user.

#### Speedster7t Power Estimator User Guide (UG093)

|                     |           | NoC            | Power                                                                    |                   |       |  |        |                   |                      |                    |

|---------------------|-----------|----------------|--------------------------------------------------------------------------|-------------------|-------|--|--------|-------------------|----------------------|--------------------|

| Device Utilization: | AC7t1500  |                |                                                                          |                   |       |  | Supply | Level (V)<br>0.85 | Current (A)<br>0.000 | Power (W)<br>0.000 |

| Available NAPs:     | 80        |                | NoC Power (W):         0.000           % of Total Dynamic:         0.00% |                   |       |  |        | 0.65              | 0.000                | 0.000              |

| Used NAPs:          | 0         | 0%             | 701                                                                      | or rotal bynamic. | 0.00% |  |        |                   |                      |                    |

| USEU NAPS:          | 0         | 076            |                                                                          |                   |       |  |        |                   |                      |                    |

|                     |           |                |                                                                          |                   |       |  |        |                   |                      |                    |

| Function            | NAP Count | Clock<br>(MHz) | Toggle Rate                                                              | Power (W)         |       |  |        |                   |                      |                    |

|                     |           |                | 10.0%                                                                    | 0.000             |       |  |        |                   |                      |                    |

|                     |           |                | 10.0%                                                                    | 0.000             |       |  |        |                   |                      |                    |

|                     |           |                | 10.0%                                                                    | 0.000             |       |  |        |                   |                      |                    |

|                     |           |                | 10.0%                                                                    | 0.000             |       |  |        |                   |                      |                    |

|                     |           |                | 10.0%                                                                    | 0.000             |       |  |        |                   |                      |                    |

|                     |           |                | 10.0%                                                                    | 0.000             |       |  |        |                   |                      |                    |

|                     |           |                | 10.0%                                                                    | 0.000             |       |  |        |                   |                      |                    |

|                     |           |                | 10.0%                                                                    | 0.000             |       |  |        |                   |                      |                    |

|                     |           |                | 10.0%                                                                    | 0.000             |       |  |        |                   |                      |                    |

|                     |           |                | 10.0%                                                                    | 0.000             |       |  |        |                   |                      |                    |

#### Figure 10: NoC Power Worksheet

#### Table 7: NoC Power Worksheet Fields

| Input Parameter   | Description                                                                                 |

|-------------------|---------------------------------------------------------------------------------------------|

| Input Fields      |                                                                                             |

| Function          | Description about the functionality/module associated with the NoC. This entry is optional. |

| NAP Count         | The number of NoC access points (NAPs) used in the function/module of the design.           |

| Clock (MHz)       | The clock frequency for the NoC used in this circuitry.                                     |

| Toggle Rate       | The percentage at which the NoC data toggles on each clock cycle for that module.           |

| Calculated Fields |                                                                                             |

| Power (W)         | The total dynamic power used by the NoCs for a particular function/module.                  |

### I/O Worksheet

The I/O power worksheet provides the user a summary of the total dynamic power consumed by the total I/O utilization and a breakdown of each of the I/O power rails based on the I/O standard selection. The worksheet also presents the I/O utilization percentage for each I/O type used.

| Device Utilization: |           |              | Dynamic                                               | Power S                                               | Summary | ,              |              | Supply            | Level (V)      | Current (A)                                                                                                          | Power (W)                                                |              | Supply            | Level (V) | Current (A) | Power (V |

|---------------------|-----------|--------------|-------------------------------------------------------|-------------------------------------------------------|---------|----------------|--------------|-------------------|----------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------|-------------------|-----------|-------------|----------|

| Device:             | AC7t1500  | ]            | I/O Po                                                | wer (W): 🛛                                            | 0.000   |                |              | GPIO_VDDIO (1.1)  | 1.1            | 0.000                                                                                                                | 0.000                                                    |              | CLKIO_VDDIO (1.5) | 1.5       | 0.000       | 0.000    |

| Package:            | 52.5x52.5 |              | % of Total [                                          | Dynamic:                                              | 0.00%   | 1              |              | GPIO_VDDIO (1.2)  | 1.2            | 0.000                                                                                                                | 0.000                                                    |              | CLKIO_VDDIO (1.8) | 1.8       | 0.000       | 0.000    |

|                     |           |              |                                                       | L.                                                    |         | ·              |              | GPIO_VDDIO (1.35) | 1.35           | 0.000                                                                                                                | 0.000                                                    |              |                   |           |             |          |

|                     | GPIOs     | Clock IOs    | DDR IOs                                               |                                                       |         |                |              | GPIO_VDDIO (1.5)  | 1.5            | 0.000                                                                                                                | 0.000                                                    |              | Supply            | Level (V) | Current (A) | Power (V |

| Available:          | 68        | 24           | 158                                                   |                                                       |         |                |              | GPIO_VDDIO (1.8)  | 1.8            | 0.000                                                                                                                | 0.000                                                    |              | DDR_S0_VDDQ (1.2) | 1.2       | 0.000       | 0.000    |

| Used:               | 0         | 0            | 0                                                     |                                                       |         |                |              |                   |                |                                                                                                                      |                                                          |              |                   |           |             |          |

|                     | 0%        | 0%           | 0%                                                    |                                                       |         |                |              |                   |                |                                                                                                                      |                                                          |              |                   |           |             |          |

|                     |           |              |                                                       |                                                       |         |                |              |                   |                |                                                                                                                      |                                                          |              |                   |           |             |          |

|                     |           |              |                                                       |                                                       |         |                |              |                   |                |                                                                                                                      |                                                          |              | _                 |           |             |          |

|                     |           |              |                                                       | <b>.</b>                                              |         | <b>.</b>       |              |                   |                |                                                                                                                      |                                                          |              |                   |           |             |          |

|                     |           | 1.1          | Input                                                 | Output                                                | Input   | Output         | Bidi         | Data              | Clock          | Toggle                                                                                                               |                                                          | Load         |                   |           |             |          |

| Function            | І/О Туре  | I/O Standard | Input<br>Term                                         | Output<br>Term                                        | Pins    | Output<br>Pins | Bidi<br>Pins | Data<br>Rate      | Clock<br>(MHz) | Toggle<br>Rate                                                                                                       | OE Rate                                                  | Load<br>(pf) |                   |           |             |          |

| Function            | I/О Туре  | I/O Standard |                                                       | -                                                     |         |                |              |                   |                |                                                                                                                      | OE Rate<br>100.0%                                        |              | -                 |           |             |          |

| Function            | I/О Туре  | I/O Standard | Term                                                  | Term                                                  |         |                |              |                   |                | Rate                                                                                                                 |                                                          |              | -                 |           |             |          |