**Speedster FPGAs**

**Preliminary Data**

**Preliminary Data**

# Copyrights, Trademarks and Disclaimers

Copyright © 2023 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedster and VectorPath are registered trademarks, and Speedcore and Speedchip are trademarks of Achronix Semiconductor Corporation. All other trademarks are the property of their prospective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

#### **Preliminary Data**

This document contains preliminary information and is subject to change without notice. Information provided herein is based on internal engineering specifications and/or initial characterization data.

#### **Achronix Semiconductor Corporation**

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail : info@achronix.com

# **Table of Contents**

| Chapter - 1: Introduction                                                         | 6  |

|-----------------------------------------------------------------------------------|----|

| Chapter - 2: Device and Maximum Number of GPIO Ports                              | 7  |

| Chapter - 3: Supported Electrical Standards                                       | 8  |

| Chapter - 4: GPIO Bank Features                                                   | 9  |

| GPIO Pin Types                                                                    |    |

| Bank Features                                                                     |    |

|                                                                                   |    |

| DDR Mode                                                                          |    |

| Chapter - 5: I/O Ring and GPIO                                                    |    |

| I/O Ring Files                                                                    |    |

| User Design Port List File                                                        |    |

| Chapter - 6: Speedster7t AC7t1500/1550 Ball Assignments by Bank                   |    |

| GPIO Pin Naming Convention                                                        | 15 |

| Ball Assignments                                                                  | 16 |

| I/O Package Diagram                                                               | 19 |

| Chapter - 7: Speedster7t AC7t800 Ball Assignments by Bank                         | 20 |

| GPIO Pin Naming Convention                                                        | 20 |

| Simple I/O Bank Naming Convention                                                 |    |

| I/O Package Diagram                                                               | 26 |

| Chapter - 8: Speedster7t GPIO IP Bank Types                                       | 27 |

| Speedster7t AC7t1500/1550 GPIO IP Bank Types                                      |    |

| Speedster7t AC7t800 GPI0 IP Bank Types<br>GPI0 Bank Placements<br>Simple I/0 Bank | 29 |

| Chapter - 9: Configuring a GPIO Bank                                              | 32 |

| Introduction                                                                        |

|-------------------------------------------------------------------------------------|

| Step 1: Determine if PLL and NoC IP Are Required                                    |

| Step 2: Create a GPIO Bank                                                          |

| Step 3: Creating a GPIO Bank IP Configuration                                       |

| Chapter - 10: Configuring a Simple I/O Bank 47                                      |

| Introduction                                                                        |

| Create a Simple I/O Bank                                                            |

| Creating a Simple I/O Bank IP Configuration                                         |

| Chapter - 11: Design Implementation and Simulation 54                               |

| Introduction                                                                        |

| Default GPIO Behavior                                                               |

| GPIO Port Lists                                                                     |

| Data and Auxiliary GPIO (Inputs) 55                                                 |

| Data and Auxiliary GPIO (Outputs)                                                   |

| Data and Auxiliary GPIO (Inout/ Bi-Directional)                                     |

| Data GPIO with SerDes Mode (INOUT)                                                  |

| DDR Mode (Inputs)                                                                   |

| DDR and SerDes Modes (Outputs)                                                      |

| Simulation                                                                          |

| Chapter - 12: Dynamically Configuring Delays with Speedster7t AC7t1500/1550 GPIO 60 |

| Introduction                                                                        |

| Memory Addressing                                                                   |

| Configuring the GPIO Bank                                                           |

| Pipeline Registers    63      Receive Path    63                                    |

| Transmit Path                                                                       |

|                                                                                     |

| Revision History                                                                    |

# Chapter - 1: Introduction

The Speedster®7t General Purpose I/O (GPIO) are digital pins that can be configured to either read data from external devices and/or output data to control external devices. GPIO pins on Speedster7t FPGAs are designed to provide a flexible, customizable, and efficient means to connect user designs to external components. To accomplish this, Achronix provides a variety of built-in features, options, supported I/O standards, and packages. This document describes the various features, how to configure them, any design considerations to be taken into account, and the tools required to implement them.

GPIO utilization requires knowledge of ACE, IP configuration, and the I/O Ring since the GPIO is part of the I/O Ring along with other interface subsystems such as PCIe and GDDR6. It is necessary to edit the IP configurations and generate I/O Ring files in order for ACE to understand the design requirements before implementing them.

There are two types of GPIO IP banks available in Speedster7t FPGAs:

- 1. The GPIO Bank

- 2. The Simple I/O Bank

The banks can configured using the ACE IP configuration perspective. The type of GPIO IP banks available depends on the Speedster7t FPGA model. Speedster7t AC7t1500/AC7t1550 FPGAs only have the GPIO Bank, while Speedster7t AC7t800 FPGAs have both GPIO and Simple I/O banks. After configuring the GPIO IP bank and generating the I/O Ring files, signals may be added to their top-level port list.

GPIO banks have built-in features such as un-registered I/O, registered I/O, DDR mode, and SerDes mode, offering more options than traditional GPIO. This can simplify the design process and speed up production. Simple I/O banks are closer to traditional GPIO and do not include the registered I/O, DDR mode, or SerDes mode features. Simple I/O banks can only be found on Speedster7t AC7t800 FPGAs.

Speedster7t FPGAs offer various traditional options that can be applied to individual GPIOs, such as pull resistors, slew rate, target impedence, etc.

Speedster7t FPGAs support a range of electrical standards that are widely used in various industries and applications. This makes Speedster7t FPGAs versatile and suitable for a wide range of applications. These electrical standards may include but are not limited to, industry standards for voltage levels, signals, and communication protocols such as GMIIs, SPI, I<sup>2</sup>C, I<sup>3</sup>C, etc.

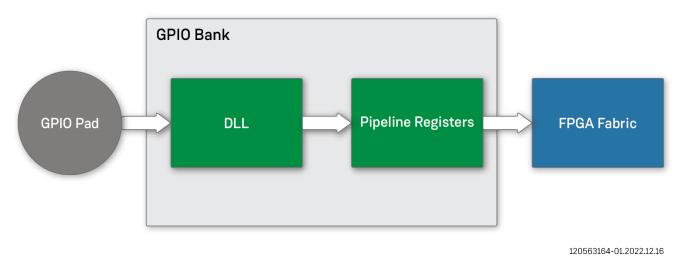

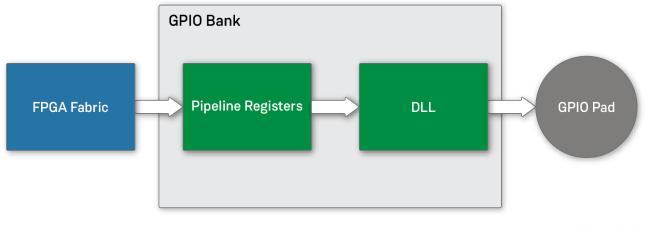

Speedster7t FPGAs have the ability to dynamically configure GPIO delays during runtime using delay-locked loops (DLL) allowing for more flexible control over timing of the GPIO signals. The built-in memory map provides a user-friendly interface for manipulating these delays dynamically.

By supporting these features, standards, and options, Speedster7t FPGA allows for easy integration and compatibility with existing systems and devices with GPIO.

A GPIO reference design is available from How do I Download Demonstration and Reference Designs for Speedster7t and Speedcore Devices? The GPIO reference design is a helpful resource for those looking to implement GPIO interfaces in their designs. It provides a tested and verified starting point for implementing GPIO features.

# Chapter - 2: Device and Maximum Number of GPIO Ports

There are three types of GPIO available in Speedster7t FPGAs:

- 1. Clock GPIO used as either input or output and can also serve as the reference clock for the GPIO bank with optioanl differential pairs.

- 2. Data GPIO capable of being used as input, output, tri-state, or bi-directional ports with optional differential pairs.

- 3. Auxiliary GPIO has the same features and usage as data GPIO including optional differential pairs.

Future releases of ACE may allow for the Speedster7t AC7t800 FPGA to enable auxiliary GPIO to serve as the reset source for the GPIO bank.

When evaluating the suitability of the Speedster7t FPGA for your design needs, refer to the following table for the available number of user GPIO ports.

| Device   | Configuration | Clock Capable | Data | Auxiliary |

|----------|---------------|---------------|------|-----------|

| AC7t800  | Differential  | 2             | 34   | 2         |

| AC71800  | Single Ended  | 2             | 68   | 4         |

| AC7t1500 | Differential  | 6             | 22   | 4         |

| AC/11500 | Single Ended  | 6             | 44   | 8         |

| AC7t1550 | Differential  | 6             | 22   | 4         |

| AG7(1550 | Single Ended  | 6             | 44   | 8         |

Table 1: Maximum Number of Available GPIO Ports by Device

#### Note

In the number of clock-capable GPIO ports in the preceding table is the same whether used as differential or single-ended. This is because the N side of a clock pair cannot be used as a single-ended port.

# Chapter - 3: Supported Electrical Standards

Speedster7t FPGAs include GPIO ports to facilitate communication with external components. These ports support various I/O standards and have the ability to operate at multiple voltages. The following table details the supported I/O standards.

| Supported<br>I/O Standard | Supported<br>Voltage (V) | Single-Ended/<br>Differential |

|---------------------------|--------------------------|-------------------------------|

| HSTL Class I              | 1.8                      |                               |

| HSUL                      | 1.2                      |                               |

|                           | 1.1                      |                               |

|                           | 1.2                      |                               |

| LVCMOS                    | 1.35                     |                               |

|                           | 1.5                      | single-ended,                 |

|                           | 1.8                      | differential                  |

|                           | 1.2                      |                               |

| SSTL Class I              | 1.35                     |                               |

| SSTE Class I              | 1.5                      |                               |

|                           | 1.8                      |                               |

| SSTL Class II             | 1.8                      |                               |

#### Table 2: Supported General-Purpose I/O Standards

#### Note

LVCMOS is labeled as supporting differential signaling in the table. This is due to the Speedster7t FPGA GPIO pad design which implements a pseudo-differential signal when differential mode is enabled on LVCMOS signals.

# Chapter - 4: GPIO Bank Features

The Speedster7t FPGA includes a variety of built-in features that can be applied to a set of GPIO ports within a GPIO Bank. The following is an overview of the Speedster7t AC7t800 FPGA built-in features such as unregistered I/O, registered I/O, SerDes mode, and DDR mode. Refer to Configuring a GPIO Bank (see page 32) for a complete guide on implementing these features. Since the GPIO bank can be found in both the Speedster7t AC7t800 and AC7t1500/AC7t1550 FPGAs, the features described are relevant to all Speedster7t FPGAs. Please note that these features are not relevant to the simple I/O bank found only in the Speedster7t AC7t800 FPGAs.

Before describing the GPIO bank features, it is important to first understand the GPIO pin types present within a GPIO bank.

# **GPIO** Pin Types

There are three types of GPIO pins available in Speedster7t FPGAs:

- 1. Clock GPIO can be used as either input or output and can also serve as the reference clock for the GPIO bank with optional differential pairs.

- Data GPIO capable of being used as inputs, outputs, tri-state, or bi-directional with optional differential pairs.

- 3. Auxiliary GPIO same features and usage as data GPIO and can also be used as differential pairs.

Future releases of ACE may allow for the Speedster7t AC7t800 FPGA to enable auxiliary GPIO to serve as the reset source for the GPIO bank.

### **Bank Features**

#### A Caution!

When enabling any of the features in this section, that feature is applied to all the GPIO ports in that bank. It is not possible to apply these features to individual signals.

### Un-Registered I/O

Un-registered I/O is the conventional form of GPIO where data or clock signals pass to/from the fabric RTL design asynchronously. This means that even if a clock GPIO is enabled and used as the reference clock for the GPIO bank, the signal is still passed asynchronously. There is no need to select a reference clock when only using unregistered data GPIO.

### Registered I/O

Registered I/O provides the ability for GPIO signals to be registered within the GPIO bank. The data GPIO can then be conveniently read or written within the fabric RTL user design. This feature requires that the GPIO bank is given a reference clock, and the data signals are aligned with the bank reference clock.

### DDR Mode

DDR Mode is only supported on Speedster7t AC7t800 FPGAs. In DDR Mode, the GPIO bank is capable of sampling and/or driving data on both the rising and falling edges of the clock signal, effectively doubling the amount of data that can be transferred per clock cycle on GPIO ports. DDR Mode is supported in combination with other features, including registered I/O and SerDes mode. This allows for even higher data transfer rates and more efficient use of FPGA resources.

### SerDes Mode

SerDes mode allows the creating a SerDes bus with one or more of the ports in the GPIO bank. SerDes mode can be used to create an Rx and/or Tx path.

# Chapter - 5: I/O Ring and GPIO

# I/O Ring Files

Hardened IP is part of the I/O ring which surrounds the Speedster7t FGPA core. The I/O ring includes GPIO, PLLs, memory interfaces, etc. that are configurable if implemented. Therefore to utilize GPIO pins, the I/O ring must be configured with the IP configuration and I/O designer tools within ACE. After generating the I/O ring IP, timing constraints, placement constraints, etc. are created automatically. It is not necessary to instantiate GPIO macros in the design.

When the GPIO bank is configured, it is then necessary to generate the required I/O ring files in ACE. For additional details on generating I/O ring files by configuring IP, see the section, Creating an IP Configuration, in the *Ace User Guide* (UG070).

The following table lists the relevant I/O ring generated files for GPIO, which may also contain information about the entire user design and not just the GPIO portion.

#### Table 3: I/O Ring GPIO File List

| File                                          | Description                                                                                                                                                                                                                                                      |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <project_name>_ioring.pdc</project_name>      | Sets constraints for pin placements linking the top-<br>level port list of the design with the I/O ring signals.                                                                                                                                                 |

| <project_name>_ioring.sdc</project_name>      | Sets the RTL design clock constraints.                                                                                                                                                                                                                           |

| <project_name>_pins.csv</project_name>        | CSV format file containing a list of GPIO pins to be<br>placed by the I/O ring, with information including the<br>names of the ball and bump, ball number, pad name,<br>polarity, clock capability, reset capability, data<br>capability, clock and reset usage. |

| <project_name>_pins.html</project_name>       | HTML format file containing information similar to the <project_name>_pins.csv file.</project_name>                                                                                                                                                              |

| <project_name>_pins.txt</project_name>        | Text format file containing a list of GPIO pins to be placed by the I/O ring, including information similar to the <project_name>_pins.csv file.</project_name>                                                                                                  |

| <project_name>_sim_defines.f</project_name>   | Includes defines needed to set GPIO clocks and resets in the I/O ring. Must be included in the simulation file list.                                                                                                                                             |

| <project_name>_sim_defines.svh</project_name> | Calls configuration functions for any subsystems using full-chip RTL. Must be included in the test bench.                                                                                                                                                        |

| File                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <project_name>_user_design_port_bindings.svh</project_name> | Binds signal names in the RTL for signals traveling<br>between the core and the I/O ring to core pins (i.e., a<br>user-renamed I/O ring port gpio_bank_1_clk_0 is a<br>named version of a hardware port from the core, e.g.,<br>i_user_11_09_mt_00[2], and must be bound so<br>that it can be properly connected by the tool). See the<br>Device Simulation Model section in the <i>Design Flow</i><br><i>User Guide</i> (UG106) for more details. |

| <project_name>_user_design_port_list.svh</project_name>     | A list of ports used to connect signals traveling to and<br>from the fabric RTL and I/O ring from the perspective<br>of the fabric RTL (e.g., SerDes parallel clock output,<br>gpio_bank_1_clk_0_parallel, going to the fabric<br>RTL would be listed as an input). Must be included in<br>the top-level port list.                                                                                                                                |

| <project_name>_user_design_signal_list.svh</project_name>   | Same as<br><project_name>_user_design_port_list.svh<br/>but uses "logic" declaration. Can be included in the<br/>test bench.</project_name>                                                                                                                                                                                                                                                                                                        |

#### Note

In the file names shown in the table include <project\_name> which is a placeholder for the ACE project name.

#### Important!

When using Speedster7t FPGAs, it is not possible to leave an enabled GPIO pin disconnected. This is because the I/O ring requires all ports to be constrained, meaning that the input or output pins must at least be connected at the top-level port list. Attempting to leave an enabled GPIO pin disconnected causes ACE to generate the following error message in the Tcl console:

\_\_\_\_\_

Net <Instance Name> on top level Port <Instance Name> does not have a valid pad connection. Unable to process this pin. Please contact Achronix customer support.

Where <Instance Name> is the name chosen in the GPIO Bank for a given signal.

### User Design Port List File

The file, <project\_name>\_user\_design\_port\_list.svh, is useful because it confirms the signal names that ACE expects in the top-level port list of the fabric RTL design. Use this file as a reference when creating the top-level port list. The following is an example of this file which uses all of the data and auxiliary GPIO set as inputs and the clock GPIO set as outputs for a Speedster7t AC7t1500/AC7t1550 FPGA.

```

// ACE GENERATED VERILOG INCLUDE FILE

// Generated on: 2022.12.05 at 15:35:49 PST

// By: ACE 8.8.2

// From project: gpio_user_guide_top

// User Design Port List Include File

// Ports for gpio_bank_1

input wire

gpio_bank_1_aux_0,

input wire

gpio_bank_1_aux_1,

gpio_bank_1_data_0,

input wire

input wire

gpio_bank_1_data_1,

gpio_bank_1_data_2,

input wire

gpio_bank_1_data_3,

input wire

gpio_bank_1_data_4,

input wire

gpio_bank_1_data_5,

input wire

input wire

gpio_bank_1_data_6,

input wire

gpio_bank_1_data_7,

output wire

gpio_bank_1_clk_0,

// Ports for gpio_bank_2

input wire gpio_bank_2_aux_0,

input wire

gpio_bank_2_aux_1,

input wire

gpio_bank_2_data_0,

input wire

gpio_bank_2_data_1,

input wire

gpio_bank_2_data_2,

gpio_bank_2_data_3,

input wire

gpio_bank_2_data_4,

input wire

gpio_bank_2_data_5,

input wire

input wire

gpio_bank_2_data_6,

input wire

gpio_bank_2_data_7,

gpio_bank_2_clk_0,

output wire

// Ports for gpio_bank_3

input wire gpio_bank_3_data_0,

input wire

gpio_bank_3_data_1,

input wire

gpio_bank_3_data_2,

gpio_bank_3_data_3,

input wire

input wire

gpio_bank_3_data_4,

input wire

gpio_bank_3_data_5,

output wire

gpio_bank_3_clk_0,

// Ports for gpio_bank_4

input wire

gpio_bank_4_aux_0,

input wire

gpio bank 4 aux 1.

input wire

gpio_bank_4_data_0,

input wire

gpio_bank_4_data_1,

input wire

gpio_bank_4_data_2,

input wire

gpio_bank_4_data_3,

input wire

gpio_bank_4_data_4,

```

```

input wire

gpio_bank_4_data_5,

input wire

gpio_bank_4_data_6,

input wire

gpio_bank_4_data_7,

output wire

gpio_bank_4_clk_0,

// Ports for gpio_bank_5

input wire

gpio_bank_5_aux_0,

input wire

gpio_bank_5_aux_1,

input wire

gpio_bank_5_data_0,

gpio_bank_5_data_1,

input wire

input wire

gpio_bank_5_data_2,

gpio_bank_5_data_3,

input wire

input wire

gpio_bank_5_data_4,

gpio_bank_5_data_5,

input wire

input wire

gpio_bank_5_data_6,

input wire

gpio_bank_5_data_7,

output wire

gpio_bank_5_clk_0,

// Ports for gpio_bank_6

input wire

gpio_bank_6_data_0,

input wire

gpio_bank_6_data_1,

input wire

gpio_bank_6_data_2,

input wire

gpio_bank_6_data_3,

input wire

gpio_bank_6_data_4,

input wire

gpio_bank_6_data_5,

output wire

gpio_bank_6_clk_0,

// End User Design Port List Include File

```

# Chapter - 6: Speedster7t AC7t1500/1550 Ball Assignments by Bank

### GPIO Pin Naming Convention

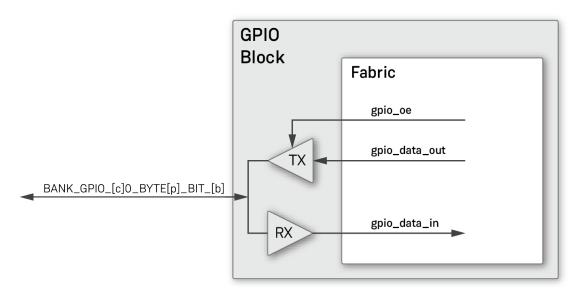

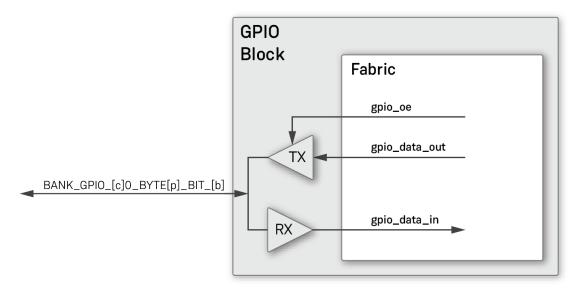

Speedter7t AC7t1500/1550 FPGA GPIO pins are placed across six different banks. The following table describes the naming convention in ACE for the placement and ball names for GPIO Bank I/O; "c" is the chip side (north or south), "p" is the bank placement (i.e., 0, 1, or 2), and "b" is the individual GPIO number (i.e., 0, 1, 2, etc.) within a bank. Placement names refer to the functional group for which a particular pad is used (e.g., clock, data, auxiliary).

#### Table 4: GPIO Bank Ball Naming Convention for Speedster7t AC7t1500/1550 FPGAs

| Placement<br>Name      | Ball/Bump<br>Name              | Туре      | Description                                                                   |

|------------------------|--------------------------------|-----------|-------------------------------------------------------------------------------|

| GPIO_[c]_B[p]_CLK_0    | BANK_GPIO_[c]0_BYTE[p]_BIT_[b] | Clock     | GPIO clock capable ball. This is the P side when used as a differential pair. |

| GPIO_[c]_B[p]_CLK_1    | BANK_GPIO_[c]0_BYTE[p]_BIT_[b] | Clock     | GPIO clock capable ball. This is the N side when used as a differential pair. |

| GPIO_[c]_B[p]_DATA_[b] | BANK_GPIO_[c]0_BYTE[p]_BIT_[b] | Data      | Arbitrary user data.                                                          |

| GPIO_[c]_B[p]_AUX_[b]  | BANK_GPIO_[c]0_BYTE[p]_BIT_[b] | Auxiliary | Arbitrary user data.                                                          |

# **Ball Assignments**

The following table lists the Speedster7t AC7t1500/1550 FPGA ball assignments for all available GPIO bank I/O.

#### Table 5: GPIO Bank Ball Assignments

| Ball/Bump<br>Name    | Bank               | GPIO<br>Type | Ball |

|----------------------|--------------------|--------------|------|

| GPIO_N0_BYTE0_BIT_10 | BANK_GPIO_N0_BYTE0 | Auxiliary    | AE16 |

| GPIO_N0_BYTE0_BIT_11 | BANK_GPIO_N0_BYTE0 | Auxiliary    | AE17 |

| GPIO_N0_BYTE0_BIT_5  | BANK_GPIO_N0_BYTE0 | Clock        | AA16 |

| GPIO_N0_BYTE0_BIT_4  | BANK_GPIO_N0_BYTE0 | Clock        | AA17 |

| GPIO_N0_BYTE0_BIT_0  | BANK_GPIO_N0_BYTE0 | Data         | W17  |

| GPIO_N0_BYTE0_BIT_1  | BANK_GPIO_N0_BYTE0 | Data         | W16  |

| GPIO_N0_BYTE0_BIT_2  | BANK_GPIO_N0_BYTE0 | Data         | Y17  |

| GPIO_N0_BYTE0_BIT_3  | BANK_GPIO_N0_BYTE0 | Data         | Y16  |

| GPIO_N0_BYTE0_BIT_6  | BANK_GPIO_N0_BYTE0 | Data         | AB17 |

| GPIO_N0_BYTE0_BIT_7  | BANK_GPIO_N0_BYTE0 | Data         | AC16 |

| GPIO_N0_BYTE0_BIT_8  | BANK_GPIO_N0_BYTE0 | Data         | AD16 |

| GPIO_N0_BYTE0_BIT_9  | BANK_GPIO_N0_BYTE0 | Data         | AD17 |

| GPIO_N0_BYTE1_BIT_10 | BANK_GPIO_N0_BYTE1 | Auxiliary    | AN16 |

| GPIO_N0_BYTE1_BIT_11 | BANK_GPIO_N0_BYTE1 | Auxiliary    | AR16 |

| GPIO_N0_BYTE1_BIT_5  | BANK_GPIO_N0_BYTE1 | Clock        | AJ17 |

| GPIO_N0_BYTE1_BIT_4  | BANK_GPIO_N0_BYTE1 | Clock        | AH16 |

| GPIO_N0_BYTE1_BIT_0  | BANK_GPIO_N0_BYTE1 | Data         | AF16 |

| GPIO_N0_BYTE1_BIT_1  | BANK_GPIO_N0_BYTE1 | Data         | AG17 |

| GPIO_N0_BYTE1_BIT_2  | BANK_GPIO_N0_BYTE1 | Data         | AG16 |

| GPIO_N0_BYTE1_BIT_3  | BANK_GPIO_N0_BYTE1 | Data         | AH17 |

| GPIO_N0_BYTE1_BIT_6  | BANK_GPIO_N0_BYTE1 | Data         | AJ16 |

| Ball/Bump<br>Name    | Bank               | GPIO<br>Type | Ball |

|----------------------|--------------------|--------------|------|

| GPIO_N0_BYTE1_BIT_7  | BANK_GPIO_N0_BYTE1 | Data         | AK17 |

| GPIO_N0_BYTE1_BIT_8  | BANK_GPIO_N0_BYTE1 | Data         | AL16 |

| GPIO_N0_BYTE1_BIT_9  | BANK_GPIO_N0_BYTE1 | Data         | AM16 |

| GPIO_N0_BYTE2_BIT_5  | BANK_GPIO_N0_BYTE2 | Clock        | AU19 |

| GPIO_N0_BYTE2_BIT_4  | BANK_GPIO_N0_BYTE2 | Clock        | AV19 |

| GPIO_N0_BYTE2_BIT_0  | BANK_GPIO_N0_BYTE2 | Data         | AP17 |

| GPIO_N0_BYTE2_BIT_1  | BANK_GPIO_N0_BYTE2 | Data         | AR17 |

| GPIO_N0_BYTE2_BIT_2  | BANK_GPIO_N0_BYTE2 | Data         | AT17 |

| GPIO_N0_BYTE2_BIT_3  | BANK_GPIO_N0_BYTE2 | Data         | AV18 |

| GPIO_N0_BYTE2_BIT_6  | BANK_GPIO_N0_BYTE2 | Data         | AR19 |

| GPIO_N0_BYTE2_BIT_7  | BANK_GPIO_N0_BYTE2 | Data         | AT20 |

| GPIO_S0_BYTE0_BIT_10 | BANK_GPIO_S0_BYTE0 | Auxiliary    | BL14 |

| GPIO_S0_BYTE0_BIT_11 | BANK_GPIO_S0_BYTE0 | Auxiliary    | BL15 |

| GPIO_S0_BYTE0_BIT_5  | BANK_GPIO_S0_BYTE0 | Clock        | BL8  |

| GPIO_S0_BYTE0_BIT_4  | BANK_GPIO_S0_BYTE0 | Clock        | BK9  |

| GPIO_S0_BYTE0_BIT_0  | BANK_GPIO_S0_BYTE0 | Data         | BL2  |

| GPIO_S0_BYTE0_BIT_1  | BANK_GPIO_S0_BYTE0 | Data         | BL3  |

| GPIO_S0_BYTE0_BIT_2  | BANK_GPIO_S0_BYTE0 | Data         | BL4  |

| GPIO_S0_BYTE0_BIT_3  | BANK_GPIO_S0_BYTE0 | Data         | BL5  |

| GPIO_S0_BYTE0_BIT_6  | BANK_GPIO_S0_BYTE0 | Data         | BL9  |

| GPIO_S0_BYTE0_BIT_7  | BANK_GPIO_S0_BYTE0 | Data         | BL11 |

| GPIO_S0_BYTE0_BIT_8  | BANK_GPIO_S0_BYTE0 | Data         | BL12 |

| GPIO_S0_BYTE0_BIT_9  | BANK_GPIO_S0_BYTE0 | Data         | BL13 |

| GPIO_S0_BYTE1_BIT_10 | BANK_GPIO_S0_BYTE1 | Auxiliary    | BL49 |

| Ball/Bump<br>Name    | Bank               | GPIO<br>Type | Ball |

|----------------------|--------------------|--------------|------|

| GPIO_S0_BYTE1_BIT_11 | BANK_GPIO_S0_BYTE1 | Auxiliary    | BL50 |

| GPIO_S0_BYTE1_BIT_5  | BANK_GPIO_S0_BYTE1 | Clock        | BL43 |

| GPIO_S0_BYTE1_BIT_4  | BANK_GPIO_S0_BYTE1 | Clock        | BK42 |

| GPIO_S0_BYTE1_BIT_0  | BANK_GPIO_S0_BYTE1 | Data         | BL39 |

| GPIO_S0_BYTE1_BIT_1  | BANK_GPIO_S0_BYTE1 | Data         | BL40 |

| GPIO_S0_BYTE1_BIT_2  | BANK_GPIO_S0_BYTE1 | Data         | BL41 |

| GPIO_S0_BYTE1_BIT_3  | BANK_GPIO_S0_BYTE1 | Data         | BL42 |

| GPIO_S0_BYTE1_BIT_6  | BANK_GPIO_S0_BYTE1 | Data         | BK44 |

| GPIO_S0_BYTE1_BIT_7  | BANK_GPIO_S0_BYTE1 | Data         | BL45 |

| GPIO_S0_BYTE1_BIT_8  | BANK_GPIO_S0_BYTE1 | Data         | BL46 |

| GPIO_S0_BYTE1_BIT_9  | BANK_GPIO_S0_BYTE1 | Data         | BL47 |

| GPIO_S0_BYTE2_BIT_5  | BANK_GPIO_S0_BYTE2 | Clock        | AY23 |

| GPIO_S0_BYTE2_BIT_4  | BANK_GPIO_S0_BYTE2 | Clock        | AT22 |

| GPIO_S0_BYTE2_BIT_0  | BANK_GPIO_S0_BYTE2 | Data         | AU20 |

| GPIO_S0_BYTE2_BIT_1  | BANK_GPIO_S0_BYTE2 | Data         | AW22 |

| GPIO_S0_BYTE2_BIT_2  | BANK_GPIO_S0_BYTE2 | Data         | AV22 |

| GPIO_S0_BYTE2_BIT_3  | BANK_GPIO_S0_BYTE2 | Data         | AU22 |

| GPIO_S0_BYTE2_BIT_6  | BANK_GPIO_S0_BYTE2 | Data         | AW23 |

| GPIO_S0_BYTE2_BIT_7  | BANK_GPIO_S0_BYTE2 | Data         | AR23 |

# I/O Package Diagram

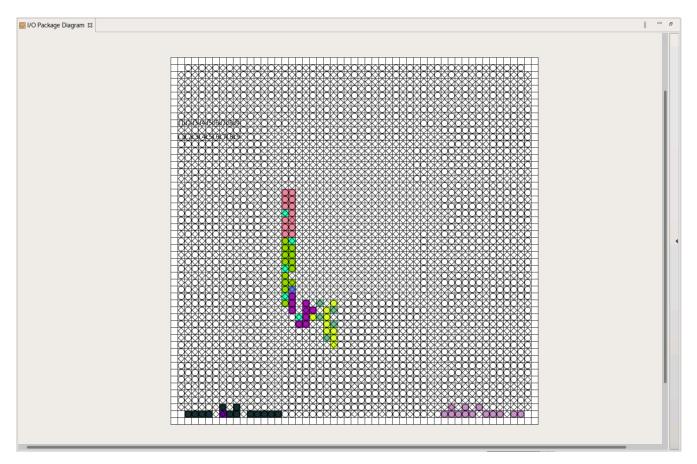

ACE includes an I/O Package Diagram view of placed balls. Hovering over a ball shows additional information for that site. The folowing image shows the ball locations for all GPIO and GPIO VDDIO for a Speedster7t AC7t1500 /1550 FPGA. The package diagram is visible by default, as shown. If not, find this view by selecting **Window**  $\rightarrow$  **Show View...**  $\rightarrow$  **Other...**  $\rightarrow$  **I/O Package Diagram**. Additional information about the I/O Package Diagram can be found in the *ACE User Guide* (UG070).

Figure 1: Ball Locations in ACE Package Diagram

# Chapter - 7: Speedster7t AC7t800 Ball Assignments by Bank

### **GPIO Pin Naming Convention**

The Speedster7t AC7t800 FPGA GPIO is placed across four different banks. Two of the four banks are GPIO and the other two are simple I/O banks.

The following table describes the ACE naming convention for the placement and ball names for GPIO bank I/O.

Table 6: GPIO Bank Ball Naming Convention for Speedster7t AC7t800 FPGAs

| Placement<br>Name    | Ball/Bump<br>Name      | Туре      | Description                                                                   |

|----------------------|------------------------|-----------|-------------------------------------------------------------------------------|

| GPIO_0_B[p]_CLK_0    | GPIO_0_BYTE[p]_BIT_[b] | Clock     | GPIO clock-capable ball. This is the P side when used as a differential pair. |

| GPIO_0_B[p]_CLK_1    | GPIO_0_BYTE[p]_BIT_[b] | Clock     | GPIO clock capable ball. This is the N side when used as a differential pair. |

| GPIO_0_B[p]_DATA_[b] | GPIO_0_BYTE[p]_BIT_[b] | Data      | Arbitrary user data.                                                          |

| GPIO_0_B[p]_AUX_[b]  | GPIO_0_BYTE[p]_BIT_[b] | Auxiliary | Arbitrary user data.                                                          |

"p" is the bank placement (e.g., 0 or 1), and "b" is the individual GPIO number (i.e., 0, 1, 2, etc.) within a bank. Placement names refer to a functional group for which a particular pad is used (e.g., clock, data, auxiliary).

### Simple I/O Bank Naming Convention

The following table describes the ACE naming convention for the placement and ball names for simple I/O banks.

#### Table 7: Simple I/O Bank Ball Naming Convention for Speedster7t AC7t800 FPGAs

| Placement Name       | Ball/Bump Name | Туре | Description          |

|----------------------|----------------|------|----------------------|

| GPIO_[p]_B0_DATA_[b] | GPIO_[p]_[b]   | Data | Arbitrary user data. |

"p" is the bank placement (e.g., 0 or 1), and "b" is the individual GPIO number (i.e., 0, 1, 2, etc.) within the simple I /O banks.

### **Ball Assignments**

The following table lists the Speedster7t AC7t800 FPGA ball assignments for all available GPIO bank I/O.

#### Table 8: GPIO Bank Ball Assignments

| Ball/Bump<br>Name   | Bank        | GPIO<br>Type | Ball |

|---------------------|-------------|--------------|------|

| GPIO_0_BYTE0_BIT_10 | BANK_GPIO_0 | Auxiliary    | AF5  |

| GPIO_0_BYTE0_BIT_11 | BANK_GPIO_0 | Auxiliary    | AF7  |

| GPIO_0_BYTE0_BIT_5  | BANK_GPIO_0 | Clock        | AG8  |

| GPIO_0_BYTE0_BIT_4  | BANK_GPIO_0 | Clock        | AG6  |

| GPIO_0_BYTE0_BIT_0  | BANK_GPIO_0 | Data         | AH7  |

| GPIO_0_BYTE0_BIT_1  | BANK_GPIO_0 | Data         | AH6  |

| GPIO_0_BYTE0_BIT_2  | BANK_GPIO_0 | Data         | AH8  |

| GPIO_0_BYTE0_BIT_3  | BANK_GPIO_0 | Data         | AH10 |

| GPIO_0_BYTE0_BIT_6  | BANK_GPIO_0 | Data         | AG10 |

| GPIO_0_BYTE0_BIT_7  | BANK_GPIO_0 | Data         | AF2  |

| GPIO_0_BYTE0_BIT_8  | BANK_GPIO_0 | Data         | AF3  |

| GPIO_0_BYTE0_BIT_9  | BANK_GPIO_0 | Data         | AF4  |

| GPIO_0_BYTE1_BIT_10 | BANK_GPIO_0 | Auxiliary    | AE9  |

| GPIO_0_BYTE1_BIT_11 | BANK_GPIO_0 | Auxiliary    | AE10 |

| GPIO_0_BYTE1_BIT_5  | BANK_GPIO_0 | Clock        | AD2  |

| GPIO_0_BYTE1_BIT_4  | BANK_GPIO_0 | Clock        | AD1  |

| GPIO_0_BYTE1_BIT_0  | BANK_GPIO_0 | Data         | AF8  |

| GPIO_0_BYTE1_BIT_1  | BANK_GPIO_0 | Data         | AF9  |

| GPIO_0_BYTE1_BIT_2  | BANK_GPIO_0 | Data         | AE2  |

| GPIO_0_BYTE1_BIT_3  | BANK_GPIO_0 | Data         | AE3  |

| GPIO_0_BYTE1_BIT_6  | BANK_GPIO_0 | Data         | AE4  |

| GPIO_0_BYTE1_BIT_7  | BANK_GPIO_0 | Data         | AE5  |

| Ball/Bump<br>Name  | Bank        | GPIO<br>Type | Ball |

|--------------------|-------------|--------------|------|

| GPIO_0_BYTE1_BIT_8 | BANK_GPIO_0 | Data         | AE6  |

| GPIO_0_BYTE1_BIT_9 | BANK_GPIO_0 | Data         | AE7  |

The following table lists the Speedster7t AC7t800 FPGA ball assignments for all available simple I/O pins.

#### Table 9: Simple I/O Bank Ball Assignments

| Ball/Bump<br>Name | Bank        | GPIO<br>Type | Ball |

|-------------------|-------------|--------------|------|

| GPIO_1_0          | BANK_GPIO_1 | Data         | AD3  |

| GPIO_1_1          | BANK_GPIO_1 | Data         | AD4  |

| GPIO_1_2          | BANK_GPIO_1 | Data         | AD5  |

| GPIO_1_3          | BANK_GPIO_1 | Data         | AD7  |

| GPIO_1_4          | BANK_GPIO_1 | Data         | AD8  |

| GPIO_1_5          | BANK_GPIO_1 | Data         | AD9  |

| GPIO_1_6          | BANK_GPIO_1 | Data         | AD10 |

| GPIO_1_7          | BANK_GPIO_1 | Data         | AC3  |

| GPIO_1_8          | BANK_GPIO_1 | Data         | AC4  |

| GPIO_1_9          | BANK_GPIO_1 | Data         | AC6  |

| GPIO_1_10         | BANK_GPIO_1 | Data         | AC7  |

| GPIO_1_11         | BANK_GPIO_1 | Data         | AC8  |

| GPIO_1_12         | BANK_GPIO_1 | Data         | AC9  |

| GPIO_1_13         | BANK_GPIO_1 | Data         | AB2  |

| GPIO_1_14         | BANK_GPIO_1 | Data         | AB4  |

| GPIO_1_15         | BANK_GPIO_1 | Data         | AB5  |

| GPIO_1_16         | BANK_GPIO_1 | Data         | AB6  |

| GPIO_1_17         | BANK_GPIO_1 | Data         | AB8  |

| GPIO_1_18         | BANK_GPIO_1 | Data         | AA1  |

| GPIO_1_19         | BANK_GPIO_1 | Data         | Y1   |

| GPIO_1_20         | BANK_GPIO_1 | Data         | AA2  |

| GPIO_1_21         | BANK_GPIO_1 | Data         | AA4  |

| GPI0_1_22         | BANK_GPIO_1 | Data         | AA5  |

| Ball/Bump<br>Name | Bank        | GPIO<br>Type | Ball |

|-------------------|-------------|--------------|------|

| GPIO_1_23         | BANK_GPIO_1 | Data         | AA6  |

| GPIO_1_24         | BANK_GPIO_1 | Data         | AA7  |

| GPIO_1_25         | BANK_GPIO_1 | Data         | AA10 |

| GPIO_2_0          | BANK_GPIO_2 | Data         | R2   |

| GPIO_2_1          | BANK_GPIO_2 | Data         | R1   |

| GPIO_2_2          | BANK_GPIO_2 | Data         | T1   |

| GPIO_2_3          | BANK_GPIO_2 | Data         | U8   |

| GPIO_2_4          | BANK_GPIO_2 | Data         | U7   |

| GPIO_2_5          | BANK_GPIO_2 | Data         | U6   |

| GPIO_2_6          | BANK_GPIO_2 | Data         | U4   |

| GPIO_2_7          | BANK_GPIO_2 | Data         | U3   |

| GPIO_2_8          | BANK_GPIO_2 | Data         | U1   |

| GPIO_2_9          | BANK_GPIO_2 | Data         | V8   |

| GPIO_2_10         | BANK_GPIO_2 | Data         | V7   |

| GPIO_2_11         | BANK_GPIO_2 | Data         | V6   |

| GPIO_2_12         | BANK_GPIO_2 | Data         | V4   |

| GPIO_2_13         | BANK_GPIO_2 | Data         | V1   |

| GPIO_2_14         | BANK_GPIO_2 | Data         | W10  |

| GPIO_2_15         | BANK_GPIO_2 | Data         | W8   |

| GPIO_2_16         | BANK_GPIO_2 | Data         | W7   |

| GPIO_2_17         | BANK_GPIO_2 | Data         | W5   |

| GPIO_2_18         | BANK_GPIO_2 | Data         | W4   |

| GPIO_2_19         | BANK_GPIO_2 | Data         | W3   |

| GPIO_2_20         | BANK_GPIO_2 | Data         | Y9   |

| GPIO_2_21         | BANK_GPIO_2 | Data         | Y8   |

| Ball/Bump<br>Name | Bank        | GPIO<br>Type | Ball |

|-------------------|-------------|--------------|------|

| GPIO_2_22         | BANK_GPIO_2 | Data         | Y6   |

| GPIO_2_23         | BANK_GPIO_2 | Data         | Y5   |

| GPIO_2_24         | BANK_GPIO_2 | Data         | Y3   |

| GPIO_2_25         | BANK_GPIO_2 | Data         | Y2   |

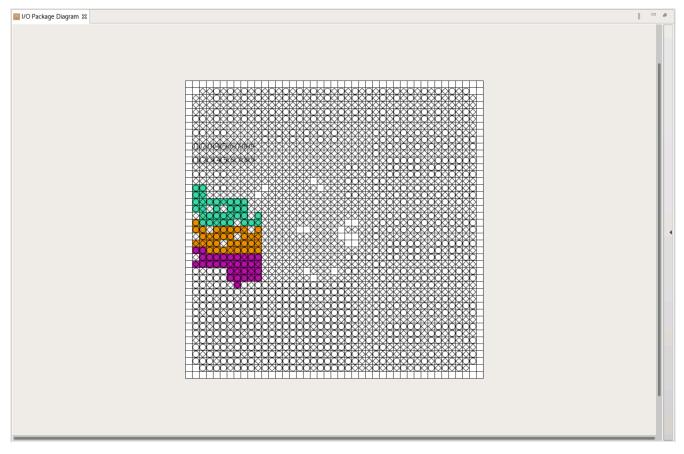

### I/O Package Diagram

ACE includes an I/O package diagram view of placed balls. Hovering over a ball shows additional information for that site. The following image shows the ball locations for all GPIO and GPIO VDDIO pins for a Speedster7t AC7t800 FPGA. The Package Diagram is visible by default, as shown. If not, find this view by selecting **Window**  $\rightarrow$  **Show View...**  $\rightarrow$  **Other...**  $\rightarrow$  **I/O Package Diagram**. Additional information about the I/O package diagram can be found in the *ACE User Guide* (UG070)".

Figure 2: Ball Locations in ACE Package Diagram

# Chapter - 8: Speedster7t GPIO IP Bank Types

There are two types of GPIO IP bank within Speedster7t FPGAs:

- GPIO bank

- Simple I/O bank

The Speedster7t AC7t800 FPGA includes both GPIO banks and simple I/O banks while the Speedster7t AC7t1500/1550 FPGAs only include GPIO banks.

### Speedster7t AC7t1500/1550 GPI0 IP Bank Types

The Speedster7t AC7t1500/1550 GPIO exists in two blocks on the chip. There is no difference in functionality between the two blocks. Each block consists of three banks for a total of six GPIO IP bank types. The Layout diagram is visible by default in ACE, as shown in the following figure. If it is not visible, it can be found by selecting **Window**  $\rightarrow$  **Show View...**  $\rightarrow$  **Other...**  $\rightarrow$  **I/O Layout Diagram**.

| 🔯 I/O Layout Diagram 🕱                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 🙀 8 🗖 🗖                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |

| AC7t1500ES0-F53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |

| PLL_NW       CLK_NW       SerDes 0-7       SerDes 8-15       SerDes 16-31       GPIO_N         Image: Comparison of the series of the seri |                                     |

| GDDR6_3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GDDR6_7                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |

| GDDR6_2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GDDR6_6                             |

| GDDR6_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GDDR6_5                             |

| GDDR6_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GDDR6_4                             |

| DDR4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | □ □ 0 1<br>□ □ 2 3<br>CLK_SE PLL_SE |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |

Figure 3: Speedster7t AC7t1500/1550 GPIO Blocks

### **GPIO Bank Placements**

The GPIO bank IP configuration editor, shown in the following figure, is where the options for a given bank are selected. The **Placement** menu is expanded showing the six available GPIO Banks.

|        |                                                                                              | of the following features in<br>all of the GPIO pins in that |   |                                                                                                                                                |                                                               |   |

|--------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---|

|        | D_bank_1.acxip ⊠<br>Deedster7t GPIO Ba<br>verview<br>I properties for the GPIO Bank can be e |                                                              |   |                                                                                                                                                |                                                               |   |

|        | Configuration                                                                                | AC7t1500ES0                                                  |   | ✓ Placement                                                                                                                                    | GPIO_N_B0                                                     | • |

| ~      | Target Device                                                                                | ACTIDUCED                                                    | • |                                                                                                                                                |                                                               |   |

|        |                                                                                              |                                                              |   |                                                                                                                                                |                                                               |   |

| ~      | DDR Mode                                                                                     | No                                                           | * | ✓ SerDes Ratio                                                                                                                                 | GPIO_N_B0                                                     |   |

| ✓<br>✓ | DDR Mode                                                                                     | No                                                           | * | <ul> <li>✓ SerDes Ratio</li> <li>✓ □ Tx Register Mode</li> </ul>                                                                               | GPIO_N_B0<br>GPIO_N_B1                                        |   |

| *      |                                                                                              | No<br>Positive edge                                          | - |                                                                                                                                                | GPIO_N_B0<br>GPIO_N_B1<br>GPIO_N_B2                           |   |

| * * *  | Rx Register Mode                                                                             |                                                              |   | ✓ ☐ Tx Register Mode                                                                                                                           | GPIO_N_B0<br>GPIO_N_B1<br>GPIO_N_B2<br>GPIO_S_B0              |   |

|        | Rx Register Mode                                                                             | Positive edge                                                |   | <ul> <li>✓ □ Tx Register Mode</li> <li>✓ Tx Edge Select</li> </ul>                                                                             | GPIO_N_B0<br>GPIO_N_B1<br>GPIO_N_B2                           |   |

|        | Rx Register Mode  Rx Edge Select Bank Clock Signal Name Bank (Serial) Clock Frequency        | Positive edge                                                |   | <ul> <li>Tx Register Mode</li> <li>Tx Edge Select</li> <li>Valid GPIO DLL refclk Frequency</li> <li>Bank (Parallel) Clock Frequency</li> </ul> | GPIO_N_B0<br>GPIO_N_B1<br>GPIO_N_B2<br>GPIO_S_B0<br>GPIO_S_B1 | v |

#### Figure 4: Speedster7t AC7t1500/1550 Available GPIO Bank Placements

#### Maximum Number of GPIO Pins for GPIO Banks

Banks B0 and B1 differ slightly from B2 in the number of GPIO pins available. The following applies to both GPIO blocks on the FPGA.

Banks B0 and B1 include:

- 2 clock-capable balls (1 differential pair/1 single-ended)

- 8 data balls

- 2 auxiliary balls

Bank B2 includes:

- 2 clock-capable balls (1 differential pair/1 single-ended)

- 6 data balls

### Speedster7t AC7t800 GPI0 IP Bank Types

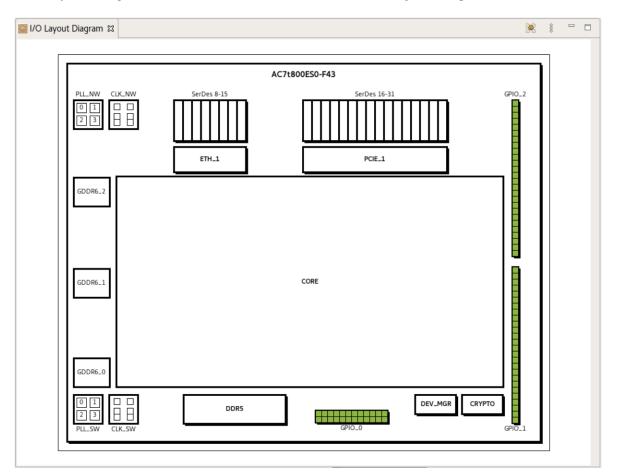

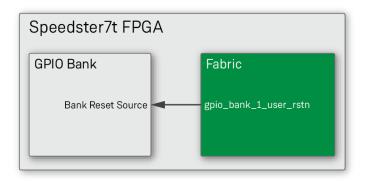

The Speedster7t AC7t800 GPIO exists in two blocks on the chip. These two blocks each contain one of two GPIO IP bank types. Two of these banks are of the GPIO bank type, and the remaining two are of the simple I/O bank type. The layout diagram is visible by default in ACE, as shown in the following figure. If it is not visible, it can be found by selecting **Window**  $\rightarrow$  **Show View...**  $\rightarrow$  **Other...**  $\rightarrow$  **I/O Layout Diagram**.

#### Figure 5: Speedster7t AC7t800 GPIO Blocks

### **GPIO Bank Placements**

The GPIO bank IP configuration editor, shown it the following figure, is where the options for a given bank are selected. The **Placement** menu is expanded showing the two available GPIO banks.

#### Caution!

When enabling any of the following features in the upper portion of the IP configuration editor, that feature is applied to all of the GPIO pins in that bank. It is not possible to apply these features to individual signals.

| gpio | o_bank_1.acxip ⊠                                                       |                         |   |   |                                                                   |               | - 0 |

|------|------------------------------------------------------------------------|-------------------------|---|---|-------------------------------------------------------------------|---------------|-----|

| 0    | Deedster7t GPIO Ba<br>verview<br>properties for the GPIO Bank can be e |                         |   |   |                                                                   |               |     |

| Bank | Configuration                                                          |                         |   |   |                                                                   |               |     |

| ~    | Target Device                                                          | AC7t800ES0              | • | V | Placement                                                         | GPIO_0_B0     | •   |

| ~    | DDR Mode                                                               | No                      | • | V | SerDes Ratio                                                      | GPIO_0_B0     |     |

| ~    | Rx Register Mode                                                       |                         |   | ~ | 🗌 Tx Register Mode                                                | GPIO_0_B1     |     |

| ~    | Rx Edge Select                                                         | Positive edge           | Ŧ | ~ | Tx Edge Select                                                    | Positive edge | -   |

| ~    | Bank Clock Signal Name                                                 | gpio_bank_1_clk_0       | ~ |   | Valid GPIO DLL refclk Frequency:                                  |               |     |

|      | Bank (Serial) Clock Frequency<br>GPIO DLL Reference Clock Period       |                         |   |   | Bank (Parallel) Clock Frequency<br>GPIO DLL Phase Shift Increment |               |     |

| ~    | Bank Reset Source                                                      | Internal Reset from FCU | - | V | Bank Global Reset Signal Name                                     | bank_reset    | -   |

| ~    | VREF Source                                                            | Internal VDD            | • | ~ | Bank Voltage Level                                                | 1.1           | •   |

Figure 6: Speedster7t AC7t800 Available GPI0 Bank Placements

#### Maximum Number of GPIO Pins for GPIO Banks

Banks B0 and B1 both include:

- 2 clock-capable balls (1 differential pair/1 single-ended)

- 8 data balls

- 2 auxiliary balls

### Simple I/O Bank

The simple I/O bank IP configuration editor, shown in the following figure, is where the options for a given bank are selected. The **Placement** menu is expanded showing the two available simple I/O banks.

#### Caution!

When enabling any of the following features in the upper portion of the IP configuration editor, that feature is applied to all of the GPIO pins in that bank. It is not possible to apply these features to individual signals.

@ simple\_io\_bank\_1.acxip ⊠

| Speedster                          | 7t Simple IO Bank                   |        |                       |                      |           |

|------------------------------------|-------------------------------------|--------|-----------------------|----------------------|-----------|

| Overview<br>All properties for the | Simple IO Bank can be edited below. |        |                       |                      |           |

| Bank Configuration                 |                                     |        |                       |                      |           |

| 🖋 Target Device                    | AC7t800ES0                          | •      | <ul> <li>✓</li> </ul> | Placement            | GPIO_1_B0 |

| ✓ VREF Source                      | Internal VDD                        | •      | <b>~</b>              | Bank Voltage Level   | GPIO_1_B0 |

| Enabl I/O Insta                    | nce Name Placement Ball/Bump Ba     | ll Dif | ffer                  | . Port Di I/O Standa | GPIO_2_B0 |

Figure 7: Speedster7t AC7t800 Available Simple I/O Bank Placements

#### Maximum Number of GPIO Pins for Simple I/O Banks

Banks GPIO\_1\_B0 and GPIO\_2\_B0 each include 26 data balls.

# Chapter - 9: Configuring a GPIO Bank

### Introduction

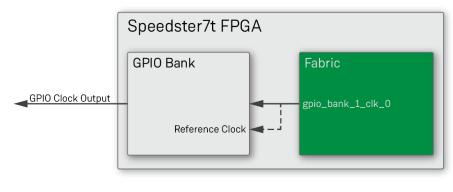

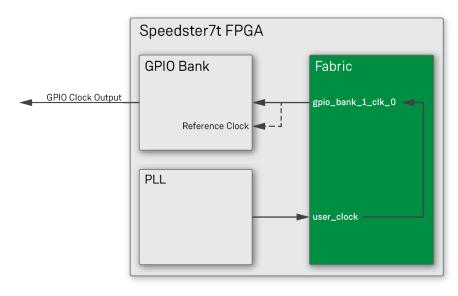

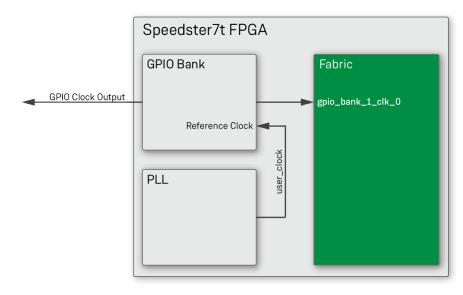

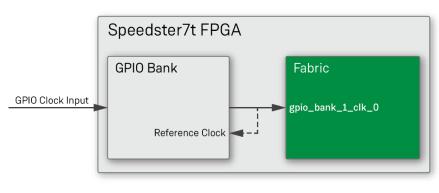

This section describes the steps required to utilize the GPIO types (clock, data, auxiliary) within a GPIO bank. The I/O ring files must first be generated with ACE by configuring one or more GPIO banks and generating the I /O ring files: