**Speedster FPGAs**

**Preliminary Data**

**Preliminary Data**

# Copyrights, Trademarks and Disclaimers

Copyright © 2020 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedcore, Speedster, and ACE are trademarks of Achronix Semiconductor Corporation in the U.S. and/or other countries All other trademarks are the property of their respective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

#### **Preliminary Data**

This document contains preliminary information and is subject to change without notice. Information provided herein is based on internal engineering specifications and/or initial characterization data.

#### **Achronix Semiconductor Corporation**

2903 Bunker Hill Lane Santa Clara, CA 95054 USA Website: www.achronix.com

E-mail : info@achronix.com

# **Table of Contents**

| Chap | oter - 1: Introduction              | . 7  |

|------|-------------------------------------|------|

| Sur  | nmary                               | . 7  |

|      | tures<br>400G/200G PCS Layer        |      |

|      | 100G PCS Layer                      | 7    |

|      | 10/25/40/50G PCS Layers             | . 7  |

|      | Reed-Solomon FEC (RS-FEC)           | . 7  |

|      | MAC                                 |      |

|      | System Multirate and Multichannel   | . 8  |

| Arc  | hitecture                           | . 8  |

|      | PMA (SerDes)                        | . 9  |

|      | PCS                                 |      |

|      | MAC                                 | 10   |

| Spe  | ecifications                        | 10   |

|      | Channels                            |      |

|      | Bitmux                              |      |

|      | SerDes                              | . 11 |

| Chap | oter - 2: System Architecture       | 12   |

|      | ernet Interface System Architecture |      |

|      | Data Flow                           | 13   |

|      | Data Connections                    | 14   |

|      | Status and Flow Control Signals     |      |

|      | Control and Status Registers        | . 14 |

|      | IP Generation and Configuration     | . 14 |

| EIU  |                                     | 15   |

|      | NAP Columns                         | 15   |

|      | Memory Buffering                    | 15   |

|      | Clocks                              | 16   |

|      | Packet and Quad Segmented Modes     | 16   |

|      | Configuration                       | . 17 |

| NA   | P Data Connections                  | 17   |

|      | Timestamp                           | 18   |

| Transmit Flags                              |    |

|---------------------------------------------|----|

| Receive Flags                               |    |

| Receive Sequence ID                         |    |

| Transmit Clock Frequencies                  | 21 |

| Receive Clock Frequencies                   | 22 |

| Combined TX and RX Frequencies              | 23 |

| Transmit Rate Limiting                      |    |

| Receive Flow Control                        | 23 |

| Flow Control and Status Signals             | 24 |

| Prefix                                      |    |

| MAC Identifier                              | 24 |

| Chapter - 3: NoC Connectivity               | 28 |

| Packet Mode                                 | 28 |

| Quad-Segmented Mode                         | 30 |

| Chapter - 4: Ethernet Clocks                | 33 |

| Clock Domains                               | 33 |

| Clock Frequencies                           | 34 |

| Reference and FIFO Clocks                   |    |

| SerDes Clocks                               |    |

| Selecting Clock Frequencies                 | 35 |

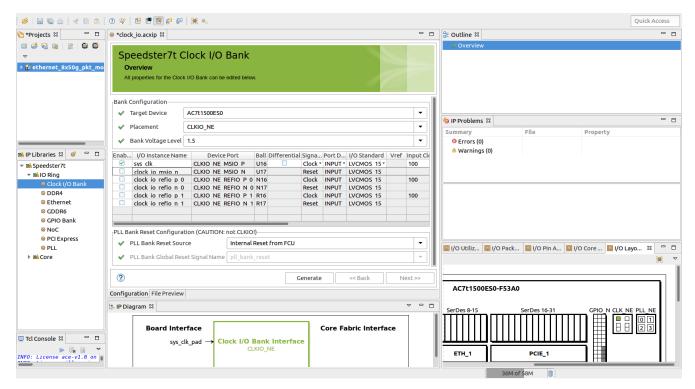

| Chapter - 5: Ethernet IP Support in ACE     | 36 |

| Overview                                    | 36 |

| Step 1 – Creating a Project                 | 36 |

| Step 2 – Configure and Generate ACE IP      | 37 |

| System Clock Input                          |    |

| NoC                                         |    |

| Ethernet PLLs                               |    |

| Ethernet Interface                          |    |

| Check for Errors and Generate the Bitstream |    |

| Generated Constraint files                  | 42 |

| Chapter - 6: Extended Features              |    |

| Low Latency                                 | 43 |

| Loopback                                    |    |

| Direct (Local) PMA Loopback Mode            |    |

| Reverse SerDes Loopback Mode                | 43 |

| Loopback Limi           | nitations | } |

|-------------------------|-----------|---|

| <b>Revision History</b> |           | 5 |

# Chapter - 1: Introduction

### Summary

Speedster®7t devices include high-speed Ethernet interfaces, which can support a wide variety of Ethernet packet protocols and speeds of up to 400 Gbps per channel. These Ethernet interfaces are paired with latest generation SerDes which individually support 100 Gbps data rates. With eight of these SerDes per Ethernet interface, each interface can support 2× 400 Gbps Ethernet IP channels.

The number of Ethernet interfaces varies according to the device. In the descriptions below, the AC7t1500 device is used as an example. This device has two Ethernet interfaces, allowing for 4× 400 Gbps interfaces, for a combined total bandwidth of 1.6 Tbps.

### Features

#### 400G/200G PCS Layer

- 400G over 8× 50G SerDes or 4× 100G SerDes

- 200G over 4× 50G SerDes or 2× 100G SerDes

#### Note

400G/200G do not support 25G SerDes. The following configurations are not available; 16× 25G or 8× 25G.

### 100G PCS Layer

- 100G Base-R PCS according to IEEE 802.3 Clause 82 specification.

- 2× SerDes lane with 53 Gbps or 1x SerDes lane with 106 Gbps.

- 4× SerDes lane with 25G (KR4) or 26.5G (KP4).

- Supports Reed-Solomon FEC (RS-FEC) implementing RS(528,514) and RS(544,514) for 100G-KR and 100G-KP applications respectively.

#### 10/25/40/50G PCS Layers

- Configurable Base-R PCS compliant with IEEE 802.3 Clauses 49, 82, 107, 133 for 10G, 25G, 50G operation respectively.

- Independent 64bit XLGMII MAC interfaces per channel.

- Supports Reed-Solomon FEC (RS-FEC) implementing RS(528,514) and RS(544,514) for 25G and 50G applications.

- Optional support for EEE fast-wake (i.e., transfer of LPI sequences, no deep sleep).

- Optional Base-R (Firecode) FEC according to Clause 74 of IEEE 802.3.

### Reed-Solomon FEC (RS-FEC)

- Support for RS(528, 514) (KR) codewords and RS(544, 514) (KP) depending on mode of operation.

- Support for RS(272, 258) low-latency variant.

- Support for 25G (Clause 108) and 50G (Clause 134) and 25/50G Ethernet Consortium specifications.

- Support for error indication to PCS when uncorrectable errors are detected.

#### MAC

- 1588 precision timing, one-step operation, for for all data rates, 10 to 400G.

- IEEE 802.3br is supported in 10...100G by providing two transmit and receive interfaces to the application.

### System Multirate and Multichannel

The Ethernet interface can be configured with up to eight lanes of SerDes and PCS. Each lane is independently usable for 10G or 25G or 50G or 100G Ethernet rates.

- Up to four 50G Ethernet channels using two 25 Gbps lanes each.

- Up to two 100G Ethernet channels using four 25 Gbps lanes each.

- Up to four 100G Ethernet channels using two 50 Gbps lanes each.

- Up to two 200G Ethernet channels using two 50 Gbps lanes each.

- Up to four 200G Ethernet channels using two 100 Gbps lanes each.

- Up to two 400G Ethernet channels using four 100 Gbps lanes each.

- One 400G Ethernet channel using eight 50 Gbps lanes.

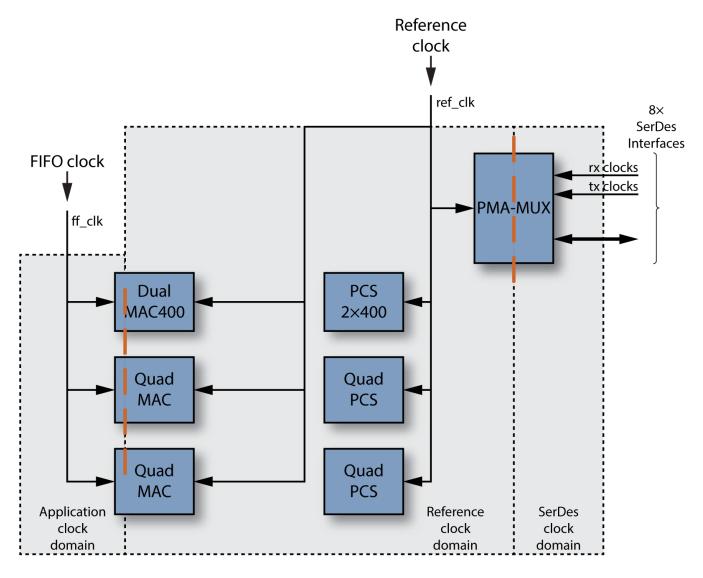

### Architecture

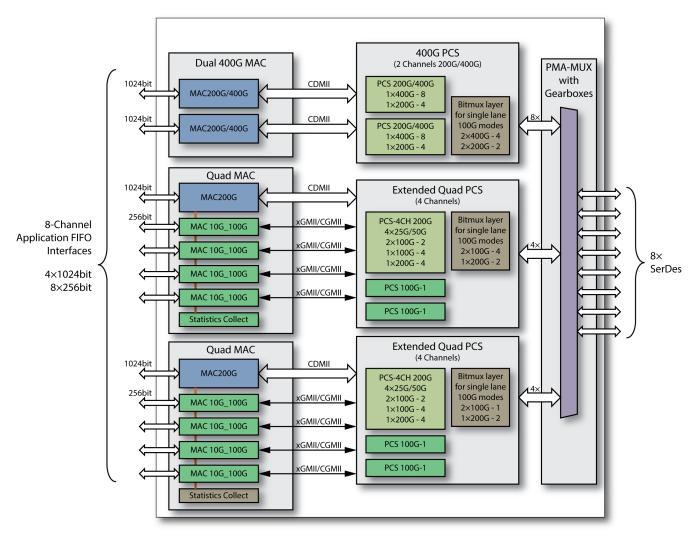

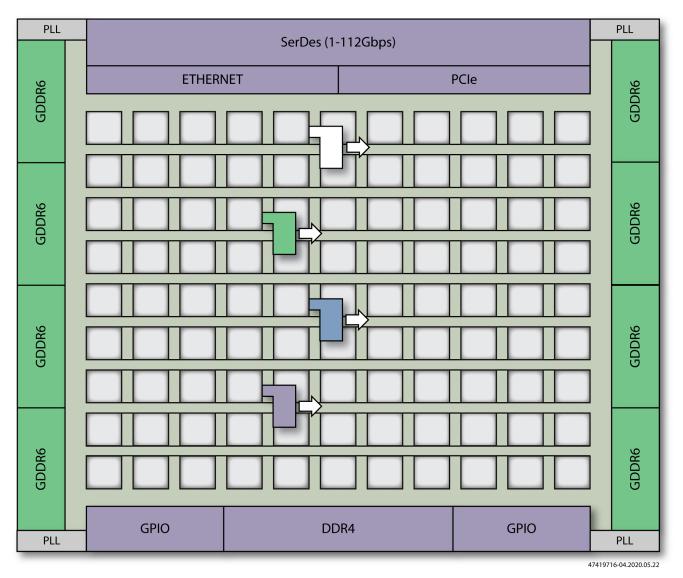

The architecture of each Ethernet interface is shown below.

47419925-01.2020.03.04

#### Figure 1: Ethernet Interface Block Diagram

### PMA (SerDes)

The physical media attachment (PMA) block consists of eight next-generation SerDes. Each SerDes can operate at up to 106.25 Gbps and down to 10.3125 Gbps. In normal operation the PMA block uses a dedicated mux to connect the SerDes directly to the PCS layer. If the user requires the SerDes for applications other than Ethernet (or to use their own Ethernet PCS and MAC), then the PMA mux can be set to connect the SerDes interface directly to the fabric.

#### Note

The PMA mux must be switched for all SerDes signals within an interface; therefore, if the user wishes to use any SerDes from an Ethernet interface directly, then all SerDes from that group are switched to the fabric, and the related Ethernet MAC and PCS are not longer available for use

### PCS

The physical coding sublayer (PCS), connects between the SerDes and the MAC. The PCS consists of a dualchannel 400G PCS which can be configured to support either 2× 200G or 2× 400G operation, and twin Quad-PCS, each of which implements a combined four channel PCS, supporting up to a single channel of 200G operation, or four channels with up to 100G per channel. The PCS layer provides the coding functions for the various channel rates supported, including Reed-Solomon error correction of RS(528, 514) (KR) and RS(544, 514) (KP) code words. In addition, support for 25G (Clause 108) and 50G (Clause 134) error correction and coding are also supported.

### MAC

The media access controller (MAC) is constructed from three blocks: one a dedicated dual channel 400G MAC for 400G/200G operation, which connects to the dual channel 400G PCS, and then two instances of a Quad-MAC, each connecting to a Quad-PCS. Each of the Quad-MAC can support a single channel of 200G, or four channels operating at 100G down to 10G per channel. The dedicated 400G MAC is optimized for higher data rates and the wider bus widths necessary for the faster interfaces; the Quad-MAC is equally optimized for multiple channels of lower data rates.

# Specifications

### Channels

Each Ethernet interface can support the following combinations of data rates

#### Table 1: Channel configurations

| Mode –<br>Lanes | SerDes<br>Lanes (per<br>Channel) | SerDes Rate<br>per Lane  | Possible<br>No. of<br>Channels | Description (with Coding Options)                  |

|-----------------|----------------------------------|--------------------------|--------------------------------|----------------------------------------------------|

| 400G – 8        | 8                                | 53.125G                  | 1                              | 400G over 8 lanes (2:1 bitmux)                     |

| 400G – 4        | 4                                | 106.25G                  | 2                              | 400G over 4 lanes (4:1 bitmux)                     |

| 200G – 4        | 4                                | 53.125G                  | 2                              | 200G over 4 lanes (2:1 bitmux)                     |

| 200G – 2        | 2                                | 106.25G                  | 4                              | 200G over 2 lanes (4:1 bitmux)                     |

| 100G – 4        | 4                                | 25.78125G or<br>26.5625G | 2                              | 100G over 4 lanes (no FEC, RSFEC-KR4 or RSFEC-KP4) |

| 100G – 2        | 2                                | 53.125G                  | 4                              | 100G over 2 lanes (RSFEC-KP 2:1 bitmux)            |

| 100G – 1        | 1                                | 106.25G                  | 8                              | 100G over 1 lane (RSFEC-KP 4:1 bitmux)             |

| 50G – 2         | 2                                | 25.78125G or<br>26.5625G | 4                              | 50G single lane (RSFEC-KR or RSFEC-KP)             |

| 50G – 1         | 1                                | 53.125G                  | 8                              | 50G single lane (RSFEC-KP 4:1 bitmux)              |

| Mode –<br>Lanes | SerDes<br>Lanes (per<br>Channel) | SerDes Rate<br>per Lane | Possible<br>No. of<br>Channels | Description (with Coding Options)                                                                  |

|-----------------|----------------------------------|-------------------------|--------------------------------|----------------------------------------------------------------------------------------------------|

| 40G – 4         | 4                                | 10.3125G                | 2                              | 40G over 4 lanes (optional Base-R (Firecode) FEC according to Clause 74 of IEEE 802.3)             |

| 40G – 2         | 2                                | 20.625G                 | 4                              | 40G over 4 lanes (optional Base-R (Firecode) FEC according to Clause 74 of IEEE 802.3), 2:1 bitmux |

| 25G – 1         | 1                                | 25.78125G               | 8                              | 25G single lane (66b or RSFEC-KR)                                                                  |

| 10G – 1         | 1                                | 10.3125G                | 8                              | 10G single lane (66b)                                                                              |

#### Bitmux

Bitmux refers to a layer of multiplexing that occurs between the PCS and the SerDes. This multiplexing provides the ability to widen the data interface to the PCS, (and MAC), while reducing the overall system frequency.

For example, 400G-8. requires 8 50G SerDes lanes. From the SerDes table (see page 11) below it can be seen that when configured as 50G, the SerDes is set to a 64-bit interface, operating at 83 0MHz. By using a 2:1 bitmux, the data bus is widened to 16 lanes of PCS, with each PCS operating at 415 MHz.

### SerDes

The SerDes supports the following modes and interface width combinations

**Table 2: SerDes Interface Configuration and Frequencies**

| SerDes Speed        | PMA Interface Width | Active SerDes Width <sup>(3)</sup> | PMA Interface<br>Frequency                    |

|---------------------|---------------------|------------------------------------|-----------------------------------------------|

| 10.3125 Gbps (NRZ)  | 128                 | 32/64                              | 32 : 322.265635 MHz<br>64 : 161.1328125 MHz   |

| 25.78125 Gbps (NRZ) | 128                 | 32/64                              | 32 : 805.6640625 MHz<br>64 : 402.83203125 MHz |

| 26.5625 Gbps (NRZ)  | 128                 | 32/64                              | 32 : 830.078125 MHz<br>64 : 415.0390625 MHz   |

| 26.5625 Gbps (PAM4) | 128                 | 32/64                              | 32 : 830.078125 MHz<br>64 : 415.0390625 MHz   |

| 53.125 Gbps (PAM4)  | 128                 | 64                                 | 830.078125 MHz                                |

| 106.25 Gbps (PAM4)  | 128                 | 128                                | 830.078125 MHz                                |

# Chapter - 2: System Architecture

## Ethernet Interface System Architecture

Due to the fully integrated architecture of the Speedster7t device, the connections to and use of the Ethernet interface subsystem, are different from what a user may be used to. In previous FPGA architectures, a user would expect to generate an RTL wrapper which contained the Ethernet interface (perhaps including also models of the SerDes). This wrapper would then be instantiated within a design, and the user would directly connect to the clock, reset, status and data ports. The user would then be expected to ensure the correct clock and reset strategies were followed, and confirm the integrity of the data connections.

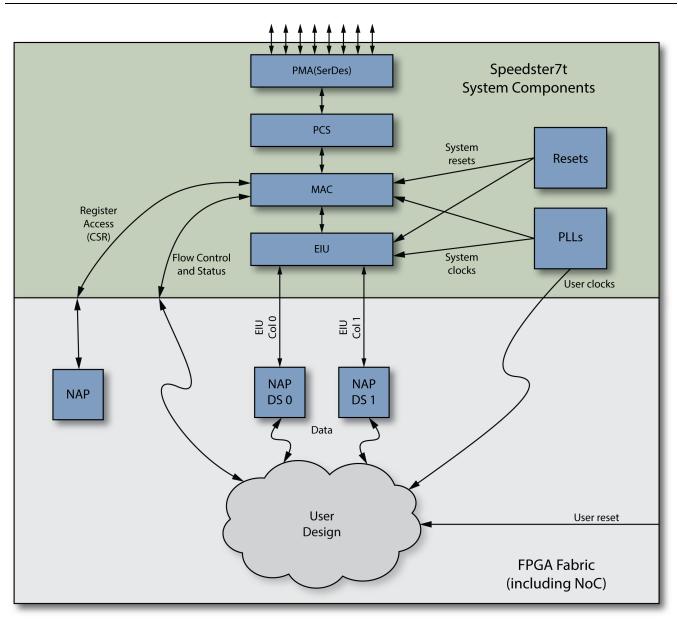

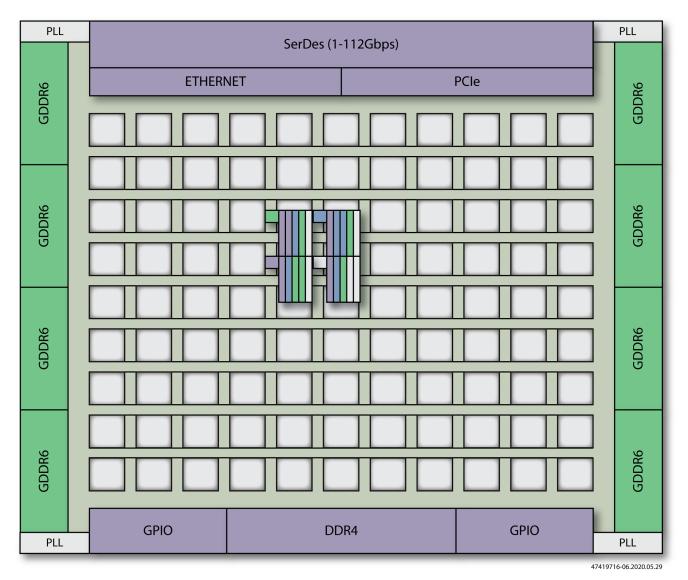

With a Speedster7t device, the usage methods and connections are very different. The full Ethernet interface, containing MAC, PCS and PMA (SerDes) is fully integrated within the Speedster7t device system components. The MAC connects via an Ethernet interface unit (EIU (see page 15)) directly to the network-on-chip (NoC). These components and the connections between them are not accessible to the user, and the user design cannot connect directly to the Ethernet interface components. This architecture is as shown below (see page 13)

70522135-01.2020.08.09

Figure 2: Ethernet Interface System Architecture

### Data Flow

The basic data flow of a user Ethernet design is as follows:

- Transmit data, in the form of whole packets, is input to a NAP

- The packet flows up the NoC column to the EIU (see page 15). Within the EIU (see page 15) the packet can be passed through, or stored and forwarded depending on the required mode. For the advanced modes(Packet and Quad Segmented Modes (see page )) the EIU (see page 15) will assemble and format the packets accordingly.

- The whole packet is transmitted in parallel form to the MAC, which processes the packet, adding preambles and FCS.

- The packet is passed through the PCS to the SerDes, and hence to the serial pins of the device.

Packet reception is a reverse of the above.

With reference to the above architecture (see page 13), the user has to make connections to the Ethernet interface with the following methods;

### Data Connections

The user connects to the Ethernet data streams using network access points (NAPs) placed within the NoC. The use of the NoC greatly simplifies the access to the Ethernet interface, with simplified data streams presented to the user.

#### Note

If or data streams, the user design only connects to the NAPs; it does not connect directly to the MAC or EIU.

For full details of the NAP data connections, refer to NAP Data Connections. (see page 17)

### Status and Flow Control Signals

Although the data streams, and accompanying metadata are delivered directly from the NAP, flow control and MAC status are connected directly to the FPGA fabric using the Ethernet direct-connect (DC) interface. When the Ethernet interface is configured within ACE, the appropriate flow control and status signals are created and set to be connected via the DC Interface to the FPGA fabric. The user can then connect directly to these signals within their design. The description of these signals is detailed in the Direct-Connect Interface table (see page 24).

#### Note

The names and types of signals vary according to the configuration of the various MACs; each MAC type has a different set of control and status signals.

### **Control and Status Registers**

Access to the internal Ethernet controller registers, is also performed via the NoC. The access is performed using a NAP, set for AXI-4 mode, which is used to access the control and status register (CSR) address space. This NAP can access any of the control registers in any of the interface subsystems on the Speedster7t device. Similar to the data streams, the user design does not connect directly to the MAC or PCS, instead access to the CSRs is only supported via the NoC.

#### Note

Correct configuration of the Ethernet interface is performed at power-up using the ACE-generated configuration. Typically a user design would only require CSR access to monitor status or to enable or disable extended features.

### IP Generation and Configuration

Generation and configuration of the Ethernet interface is performed using ACE I/O Designer as detailed in Ethernet IP Software Support in ACE (see page 36). The configuration created within ACE sets the appropriate channel modes while ensuring the correct clocks and frequencies are provided to the Ethernet interface. ACE subsequently generates the following files:

- A bitstream file for the Ethernet interface. This file is merged with other bitstream files during final bitstream assembly. This bitstream programs the Ethernet interface upon FPGA power-up, ensuring the Ethernet interface is ready for operation once the device enters user mode.

- A simulation configuration file. This file is input to the simulation environment to set Ethernet interface configuration.

With the above generation and configuration flow, combined with the fully integrated nature of the Speedster7t device, the user no longer has the responsibility for ensuring the right clocking and reset strategies are followed. The Speedster7t device, combined with ACE, manage these low-level tasks leaving the user to concentrate on the core parts of their design.

### EIU

The Ethernet interface unit (EIU) is unique to the Speedster7t family of devices. There is an EIU for each Ethernet interface, and each instance manages the connection of the MAC data interfaces to the NoC. The EIU adapts the traffic flow and performs clock domain crossings between the NoC and the MAC. It is further responsible for dividing the traffic when one of the 400G or 200G, packet or quad modes is selected. For all modes, the EIU is responsible for packetizing the traffic so it can be sent down the appropriate NoC column to the correct NAP endpoint.

### NAP Columns

Each EIU supports two NoC columns which the Ethernet NAP endpoints can be located on. The EIU will only send and receive packets to NAPs placed within those two columns. The particular columns that an EIU is connected to for each Ethernet interface is detailed in the table below. (see page 15)

#### Table 3: Ethernet NoC columns

| Device   | Ethernet S    | Total NoC Columns |   |

|----------|---------------|-------------------|---|

|          | 0             | 1                 |   |

| ac7t1500 | Columns 0 & 1 | Columns 4 & 5     | 4 |

### Memory Buffering

The EIU has memory buffering, primarily in order to do the higher line rate packet division and rearrangement. In addition the buffering is used for clock crossing and packetization. The EIU buffering operates in two modes, according to the selected line rate

- For 200 and 400G Packet and Quad Segmented Modes, (see page) the EIU operates in a store-andforward mode. Each whole packet is buffered until it is fully received from the NoC, and then it is forwarded to the MAC. A similar scheme operates for received packets.

- In all other modes, no buffering is performed; therefore, the EIU should be considered as a transparent block with minimal buffering. This mode places frequency and throughput restrictions on the NAPs; these restrictions are discussed below.

Each NAP only has a shallow buffer in order to support clock domain crossing. For a system design the NAPs should also be considered transparent elements with minimal or no buffering capability.

### Clocks

The EIU bridges between the NoC core operating frequency, 2 GHz, and the MAC  $ff_clk$  frequency domains. Each of these clock domains can be configured by the user. The NoC operating frequency is fixed, and the user must provide a 2 GHz clock as detailed in Ethernet IP Software Support in ACE (see page 36). The minimum MAC  $ff_clk$  frequencies are defined in the Reference and FIFO Clock frequencies. (see page 34)

### Packet and Quad Segmented Modes

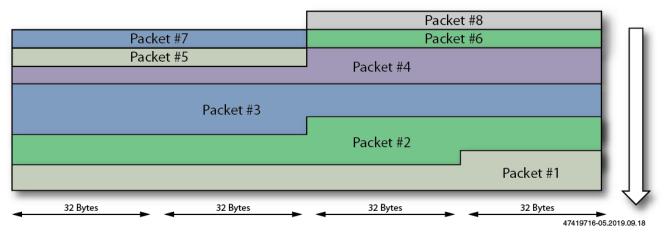

At higher data rates, 200G and 400G, it is impractical to transmit the full bandwidth through a single NAP (for 400 Gbps, this rate would require an operating frequency of 2 GHz for the associated fabric logic). Therefore, the EIU and NoC support spreading the bandwidth across four NAPs. There are then two operating modes for these four NAPs:

- Quad segmented mode (QSI). The four NAPs are combined to form a single 1024-bit bus. The packet is rotated around the four NAPs such that a new packet will start on the lane after the previous packet ended. For example, if the NAPs are identified as NAP-1 to NAP-4, then if the end-of-packet (EoP) word is output on NAP-2, and the next packet asserts it's start-of-packet (SoP) word on NAP-3.

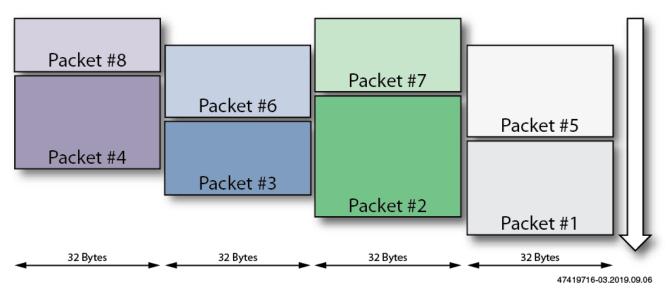

- **Packet mode**. The four NAPs each process a whole packet, providing four 100G streams to the fabric. Each NAP operates through its 256-bit data bus interface. The EIU transmits the next available packet to whichever NAP is not currently transmitting a packet.

For additional details on each of these modes, including diagrammatic representations of the packet structure, refer to Speedster7t Ethernet NoC Connectivity. (see page 28)

#### **Mode Considerations**

The two schemes each have advantages and disadvantages:

- For QSI, packet ordering is guaranteed as the NAPs present a single 1024-bit bus for both transmit and receive. However, the width of the bus can create routing challenges, or difficulties with interfacing the data to other interface subsystems, such as memory. The NAP's native data width is 256 bits, requiring buffering and pipelining for the 1024-bit bus to be written to another NAP. In addition the requirement to barrel shift the packet around the bus for different packet start lanes can add complexity to a design.

- Packet mode has the advantage of having whole packets contained within a single 256-bit bus, which can

then be easily connected to other NAPs, and hence to other interface subsystems or other parts of the

design. However, in packet mode the four streams are separate with no guaranteed packet ordering. In

many systems, this lack of ordering is not an issue; however, if point-to-point communication is being

used, and packet ordering is required, then packet ordering will need to be implemented.

#### Note

In the Ethernet standard does not guarantee packet ordering due to the architecture of multiple routes through a network. Packet sequence ordering is supported in higher level protocols such as TCP/IP.

#### Warning!

For packet mode transmission, the Ethernet subsystem forwards a packet as it is delivered from the EIU. This ordering is dependent upon not only the order that packets are input to their respective NAPs, but also on the buffering within the NAP, NoC and EIU. As a result, it is not possible to implement transmit packet ordering in packet mode.

The choice as to which mode is most suitable will be based on many factors. These include the ease of interfacing to the 1024-bits of Quad Segmented mode, or the requirement for packet ordering performed at a hardware level. The user is directed to investigate the two approaches as implemented within the Speedster7t Ethernet Reference Designs

### Configuration

The EIU configuration is controlled by parameters set on each NAP within the user design. These parameters set the NAP column location, channel speed, channel mode (packet or QSI), etc. These parameters are then used by both the simulation environment and ACE to ensure the EIU is correctly configured.

## NAP Data Connections

The data streams to and from the Ethernet MACs are interfaced to the user design with the use of NAPs. The specific NAP component is an ACX\_NAP\_VERTICAL, full details of which can be found in the *Speedster7t IP Component Library User Guide* (UG086). When connected to the EIU (see page 15), the NAP connections are listed below.

#### Table 4: Ethernet NAP Data Ports

| Name           | Direction | Description                                                                                                                                                                                 | Ethernet NAP<br>Usage                                           |

|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| rstn           | Input     | Asynchronous reset input. This signal resets the NAP interface. This signal does not affect the NoC.                                                                                        |                                                                 |

| output_rstn    | Output    | (Do not use) Reset output from NAP to fabric logic. Intended<br>for use with partial reconfiguration. Signal controlled by write to<br>configuration space. Currently signal fixed to 1'b0. | Same.                                                           |

| clk            | Input     | All operations are fully synchronous and occur upon the active edge of the clk input.                                                                                                       |                                                                 |

| tx_ready       | Output    | Asserted high when the NAP can accept data.                                                                                                                                                 | Same. Used to flow                                              |

| tx_valid       | Input     | Assert high to issue a word of data to the NAP.                                                                                                                                             | control transmit data.                                          |

| tx_dest[3:0]   | Input     | The 4-bit destination ID of the row that this word of data should be sent to.                                                                                                               | Must be set to 4'hf<br>(EIU reserved<br>address)                |

| tx_sop         | Input     | Start of packet and end of packet indicators. These values are                                                                                                                              | Same.                                                           |

| tx_eop         | Input     | sent unmodified to the destination.                                                                                                                                                         | Same.                                                           |

|                |           |                                                                                                                                                                                             | tx_data[255:0] = Data                                           |

| tx_data[292:0] | Input     | Data transmitted to the destination node.                                                                                                                                                   | tx_data[260:256] =<br>Mod. Only used when<br>tx_eop is asserted |

| Name             | Direction   | Description                                                                                | Ethernet NAP<br>Usage                                                     |

|------------------|-------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| tx_data[292:0]   | Input       |                                                                                            | tx_data[290:261] =<br>Transmit flags or<br>timestamp (see table<br>below) |

|                  |             |                                                                                            | tx_data[292:291] =<br>Unused                                              |

| rx_ready         | Input       | Asserted high by user logic to indicate it is ready to receive data.                       | Same. Used to flow control received data.                                 |

| rx_valid         | Output      | Asserted high with each valid rx_data word.                                                | control received data.                                                    |

| rx_src[3:0]      | Output      | The 4-bit transmission source ID indicating the row that originated the data.              | Will always be 4'f ,<br>indicating packet is<br>from the EIU              |

| rx_sop<br>rx_eop | Output      | Start of packet and end of packet indicators. These values are unmodified from the source. | Same.                                                                     |

|                  | 2:0] Output |                                                                                            | rx_data[255:0] = Data                                                     |

|                  |             |                                                                                            | rx_data[260:256] =<br>Mod. Only valid when<br>rx_eop is asserted          |

| rx_data[292:0]   |             |                                                                                            | rx_data[290:261] =<br>Receive flags or<br>timestamp (see table<br>below)  |

|                  |             |                                                                                            | rx_data[292:291] =<br>Unused                                              |

### Timestamp

For both transmit and receive, when SoP is asserted, the flag field, data[290:261], is set to equal the timestamp value:

- For transmission the user design can generate a free running counter and insert this value into the flag field aligned with tx\_sop. This value can then be inserted into the outgoing Ethernet packet by enabling the appropriate timestamp mode.

- For reception the timestamp field is a free running value, updated by a 1 GHz clock within the Ethernet interface system. This value represents the time at which the packet was output from the MAC to the EIU (see page 15).

For full details of how the timestamp fields are generated and used, including IEEE-1588 1-Step updating, refer to Speedster7t Ethernet IEEE Timestamping.

### Transmit Flags

In addition to the timestamp, during the remaining packet period, the flag field can contain a number of important flags to indicate packet status.

#### Table 5: Ethernet NAP Transmit Flags

| Slice       | Direction | Flag Name    | Description                           |  |  |

|-------------|-----------|--------------|---------------------------------------|--|--|

| Flag[16:0]  | Output    | ID           | One-step update control vector        |  |  |

| Flag[17]    | Output    | Frame        | Set to indicate IEEE 1588 event frame |  |  |

| Flag[18]    | Output    | Error        | Frame error                           |  |  |

| Flag[19]    | Output    | CRC          | CRC indicator                         |  |  |

| Flag[20]    | Output    | CRC invert   | CRC inverted indicator                |  |  |

| Flag[21]    | Output    | CRC overflow | CRC overflow indicator                |  |  |

| Flag[22]    | Output    | Class A      | Class A packet                        |  |  |

| Flag[23]    | Output    | Class B      | Class B packet                        |  |  |

| Flag[29:24] | Output    | Unused       | Should be set to 6'b0                 |  |  |

| Table Note  |           |              |                                       |  |  |

Table Note

If the user design does not wish to make use of any of the transmit flags, or the transmit timestamp field, then the appropriate fields should be set to 1'b0.

Table 6: One-Step Update Control Vector Values

| Bit   | Description                                                                                                                                                                                                                    |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|       | Frame Identifier. An arbitrary value that can be used to mark specific frames. This value is available at the transmit status pins when the frame has been transmitted. The usage of the identifier is transparent to the MAC. |  |  |

| [3:0] | Note<br>The ID vector is only valid when frame=1'b1.                                                                                                                                                                           |  |  |

| 4     | <ul> <li>1'b1 – A one-step field update for the frame should occur. All following bits are valid.</li> <li>1'b0 – No update occurs, and all following bits have no relevance.</li> </ul>                                       |  |  |

| Bit    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5      | <ul> <li>1'b1 – Add the peer_delay value to the correction field in addition to the transient time update. This setting is required for peer-to-peer transparent clocks.</li> <li>1'b0 – Only the transient time will be added.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                        |

| 6      | <ul> <li>1'b1 – Indicates that the 1588v2 message is using UDP/IP and the UDP checksum needs to be corrected. This setting modifies the last two bytes of the payload (two bytes before frame CRC).</li> <li>1'b0 – Indicates that no UDP checksum update should be done. See Speedster7t Ethernet IEEE Timestamping on usage and limitations of this function.</li> </ul>                                                                                                                                                                                                                                                        |

| [14:7] | Start offset from begin of frame where the field to update is found (index to most significant byte). An 8-bit value given in steps of byte. The offset must respect all MAC headers, VLAN tags and other protocol headers accordingly.<br>Offset Examples:<br>• Ethernet L2 frame: 22 (14:MAC Header+8 correction field offset in header).<br>• UDP/IPv4 frame: 50 (14:MAC header, 20: IPv4 header, no options; 8:UDP header; 8:correction field offset).<br>• UDP/IPv6 frame: 70 (40 for IPv6 header instead 20 of IPv4).<br>Note<br>• The minimum offset for field update is 16.<br>• VLAN tags require adding +4 accordingly. |

| 15     | <ul> <li>Perform 64-bit seconds/nanoseconds time field update:.</li> <li>1'b1 – Bits 5 and 6 cannot be used and must be 0. The offset defines the start of a 64-bit field (byte granularity) within the frame. The field is updated with 8 bytes from TX timestamp. The first byte of the field is the most significant). The minimum offset for 64-bit field update is 16.</li> <li>1'b0 – No update will occur.</li> <li>Note         This function sets the field, overwriting the previous frame contents.     </li> </ul>                                                                                                    |

| 16     | <ul> <li>Perform 48-bit correction field update from delta value (see pins).</li> <li>1'b1 – The update adds the application provided delta value to the current correction field value extracted from the frame. Bit 5 cannot be used and must be 0.</li> <li>1'b0 – No update will occur</li> </ul>                                                                                                                                                                                                                                                                                                                             |

### **Receive Flags**

In addition to the timestamp, during the remaining packet period, the received flag field can contain a number of important flags to indicate packet status.

#### Table 7: Ethernet NAP Received Flags

| Slice       | Direction | Flag<br>Name    | Description                                                                                                                                                   |

|-------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flag[0]     | Input     | Error           | Frame error indicator.                                                                                                                                        |

| Flag[8:1]   | Input     | Error<br>Status | Frame error status. Indicates the type of frame error.                                                                                                        |

| Flag[13:9]  | Input     | Sequence<br>ID  | Frame sequence indicator. Details the order that the packet was output from the MAC. Used particularly in packet mode to reassemble original packet sequence. |

| Flag[29:14] | Input     | Unused          | Set to 16'b0.                                                                                                                                                 |

### **Receive Sequence ID**

The receive sequence ID is a 5-bit count which indicates the order in which packets were transmitted from the EIU (see page 15):

- For a single stream (all data rates up to and including 100G), a continuous count of receive sequence IDs will be received at the single NAP.

- For Quad Segmented Mode (see page ) (200 and 400G), the same sequence ID will be present on all segments of the same packet.

- For Packet Mode (see page ) (200 and 400G), the next sequence ID in order could be presented at any of the four possible NAP endpoints. If receive packet ordering is required, then each NAP must be checked to locate the next packet in sequence.

### Transmit Clock Frequencies

At all data rates, the complete Ethernet transmission subsystem must ensure that an Ethernet packet is transmitted as a contiguous whole; no part of the system must be allowed to run empty between a start of packet (SoP) and an end of packet (EoP). This restriction places differing requirements on the NAPs based on the selected data rate.

#### 10G/25G/50G/100G

In these modes the EIU is operating with no buffering; therefore, it can be considered that the packet is transmitted directly from the NAP to the MAC. In this case, the NAP must operate at a sufficient frequency that matches the required line rate in order, that when the longest potential frame is transmitted, the whole frame can be sent within the required time.

Assuming a system needs to support jumbo frames with a NAP data width of 256-bits, the following transmit frequencies are required.

| Data Rate<br>(Gbps) | Frequency<br>(MHz) |

|---------------------|--------------------|

| 10                  | 40                 |

| 25                  | 98                 |

| 50                  | 195                |

| 100                 | 390                |

#### Table 8: NAP Lower Data Rate Transmit Minimum Frequencies

#### Note

The transmit frequencies above will only achieve the full stated line rate if all packets are of a length that fits the NAP data width exactly; hence, all packet lengths are a multiple of 32 bytes. If packets of varying lengths are used, then the transmit frequencies need to increase to support the loss in bandwidth caused by having unused data bytes in the last word of a packet. For example, if a packet of 1488 bytes is transmitted (46 full words of 256-bits or 32 bytes, followed by one word of 16 bytes) then the 47 transmit cycles delivers 46.5 cycles of data. Hence, to achieve full line rate, the transmit frequency needs to be increased by a ratio of 47/46.5.

#### 200G/400G

For these line rates the EIU operates in a store-and forward mode, as it has to process each packet based on the stream configuration of quad segmented or packet mode. Therefore, there are no requirements on the transmit frequency. The NAP can transmit at any frequency as the EIU will wait until it has received a whole packet, before transferring that packet to the MAC.

#### **Receive Clock Frequencies**

For received packets, there are the same requirements that a packet must not overflow during any stage as it is input to the MAC, and sent via the EIU to a NAP.

#### 10G/25G/50G/100G

For these data rates the EIU is operating in transparent mode — a packet traverses directly from MAC to NAP. As the receive path is designed for packets of any length, including worst-case lengths of  $n \times 32 + 1$  bytes, the receive operating frequency must be high enough to support these worst-case scenarios.

#### Table 9: NAP Lower Data Rate Receive Minimum Frequencies

| Data Rate<br>(Gbps) | Frequency<br>(MHz) |

|---------------------|--------------------|

| 10                  | 57                 |

| 25                  | 143                |

| 50                  | 254                |

| Data Rate | Frequency |

|-----------|-----------|

| (Gbps)    | (MHz)     |

| 100       | 507       |

#### 200G/400G

At these data rates, the EIU will transmit packets direct to the NAP. The NAP receive clock rate must be sufficient to match the EIU transmission rate

#### Table 10: NAP Higher Data Rate Receive Minimum Frequencies

| Data Rat0<br>(Gbps) | Frequency<br>(MHz) |

|---------------------|--------------------|

| 200                 | 254                |

| 400                 | 507                |

### Combined TX and RX Frequencies

Although it is possible to configure the NAPs as either transmit or receive only, in most scenarios it is expected that the same NAP will be used for both transmit and receive. In these configurations the higher of the transmit or receive clock frequency will need to be met for the NAP single clock.

### **Transmit Rate Limiting**

In the case where a NAP is both receiving and transmitting, the operating frequency will then be high enough to support worst-case length packets. However, with these higher frequencies, it is also possible that the NAP can exceed the transmit bandwidth, leading to overflows and data loss. For example, for a 100G configuration with a NAP frequency set at 507 MHz, each NAP has a theoretical bandwidth of 130 Gbps, which is in excess of what the EIU would support from a single NAP. Therefore, it is necessary to implement transmission rate limiting for an Ethernet NAP to ensure that the overall data rate is not exceeded.

In the example above, the maximum of 130 Gbps is 13/10 faster than the MAC and EIU can sustain. Therefore, in the Speedster7t Ethernet Reference Designs a transmit rate limiter control block is included which monitors the rate and maintains a 10/13 ratio maximum duty cycle for all transmissions. A version of this block or an equivalent should be used to ensure the correct transmit data rate is maintained.

#### Note

When using lower data rates with the EIU operating in transparent mode, it is suggested that any transmit flow control is performed between packets, rather than breaking up a single packet transmission. However, if very large packets are used, it may be necessary to insert flow control breaks at intervals within the packet.

### **Receive Flow Control**

Similarly to transmission, the reception of Ethernet traffic should not rely on buffering within the EIU or NAP. Therefore, any design should be structured to receive the full packet from a NAP without de-assertion of the receive ready. In the Speedster7t Ethernet Reference Designs, where this receive flow control could occur, a FIFO is connected to the NAP to ensure that full packets can be received uninterrupted. Receive flow control is then enacted on the FIFO output as opposed to the NAP output.

The receive FIFO can be composed of either four Speedster7t LRAM2K\_FIFO (each set to 72-bit width each) or two Speedcore7t BRAM72K\_FIFO (set to 144-bit width each).

### Flow Control and Status Signals

The flow control and status signals have a logical and consistent naming scheme, consisting of <prefix>\_<mac\_identifier>\_function. The details of <prefix> and <mac\_identifier> are listed below.

### Prefix

Configuration of the Ethernet Interface is performed using ACE I/O Designer, as detailed in Ethernet IP Software Support in ACE (see page 36). Each Ethernet Interface is named during generation. The Ethernet Interface name is prefixed to each signal name to distinguish different Ethernet Interfaces and to aid users in having separate logical names for each instance. In the tables below, this prefix is shown as cprefix>\_ on each signal name.

### MAC Identifier

The control and status lines use identifiers to logically group signals from the same MAC:

- m[1:0] is for 400G/200G MAC

- mq0 is for QUAD0 MAC

- mql is for QUAD1 MAC

This identifier follows the prefix field in the signal name table below.

#### Table 11: Ethernet Controller Direct Connect Interface

| Pin Name <sup>(1,2)</sup>                | Direction | Width | Comments                                                                                                                                                                                                                                                                                                                                                                                                         | Clock                                                                        | Raw Mode = 0<br>Data Going<br>to Ethernet |

|------------------------------------------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------|

| Quad MAC                                 |           |       |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              |                                           |

| <prefix>_mq<n>_tx_hold_req</n></prefix>  | Input     | 4     | Per channel 100G MACs. Holds and preempts if needed the pMAC (optional, e.g., for test/debug or if higher layer function anticipates an eMAC frame being written soon and wants to prepare the MAC instead having the MAC doing it automatically from the eMAC FIFO being non-empty).                                                                                                                            | Synchronous to<br>(Application0<br>Clock)/2                                  | mq <n>_tx_hol<br/>d_req</n>               |

| <prefix>_mq<n>_lpi_txhold</n></prefix>   | Input     | 4     | Per channel 100G MACs. Prevents MAC transmit from transmitting a frame even if data is stored in FIFO.                                                                                                                                                                                                                                                                                                           | Asynchronous<br>Input<br>Synchronized<br>internally on<br>Reference<br>Clock | mq <n>_lpi_txh<br/>old</n>                |

| <prefix>_mq<n>_time_1ms_tgl</n></prefix> | Input     | 4     | Per MAC channel 1 ms time base. It is required for internal timing functions. The signal must toggle its value every 1 ms.                                                                                                                                                                                                                                                                                       | Asynchronous<br>Input                                                        | mq <n>_time_<br/>1ms_tgl</n>              |

| <prefix>_mq<n>_mac_stop_tx</n></prefix>  | Input     | 4     | Per channel control of MAC transmit. For each lane, when<br>it's respective input is asserted (1'b1), the MAC transmit<br>state machine stops after any ongoing frame has been sent<br>completely (i.e., does not corrupt outgoing frames). If further<br>frames are available in the transmit FIFO the MAC will not<br>begin transmitting them until the respective mac_stop_tx is<br>de-asserted (1'b0) again. | Synchronous<br>to (ref_clk)/2                                                | mq <n>_mac_s<br/>top_tx[3:0]</n>          |

| Pin Name <sup>(1,2)</sup>                      | Direction | Width | Comments                                                                                                                                                                                                                                                                                                                                                                                      | Clock                                               | Raw Mode = 0<br>Data Going<br>to Ethernet      |

|------------------------------------------------|-----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------|

| <prefix>_mq<n>_emac_xoff_gen</n></prefix>      | Input     | 32    | Transmit flow control generate (8 bits per channel) to eMAC<br>/pMAC. When PFC pause mode is enabled, an 8-bit input                                                                                                                                                                                                                                                                          | Asynchronous<br>input<br>synchronized<br>to ref_clk | mq <n>_emac<br/>_xoff_gen[31:<br/>0]</n>       |

| <prefix>_mq<n>_pmac_xoff_gen</n></prefix>      | Input     | 32    | vector is used to signal the creation of PFC control frames.<br>When link pause mode is enabled, bit 0 (per channel, i.e.,<br>bits 0,8,16,24) is used only.                                                                                                                                                                                                                                   |                                                     | mq <n>_pmac<br/>_xoff_gen[31:<br/>0]</n>       |

| <prefix>_mq<n>_mac_peer_delay</n></prefix>     | Input     | 120   | A peer delay value that can be added to the correction field<br>for all one-step updates (30 bits per channel). Must be wired<br>to 0 if unused.                                                                                                                                                                                                                                              | Synchronous<br>to ref_clk                           | mq <n>_mac_<br/>peer_delay_va<br/>I[119:0]</n> |

| <prefix>_mq<n>_mac_peer_delay_val</n></prefix> | Input     | 4     | Per channel valid strobe for mac_peer_delay (1 bit per<br>channel). Must assert for 1 ref_clk clock cycle when the<br>peer delay was updated to write the mac_peer_delay value<br>to the MAC internal register. Once the value has been<br>written (i.e., peer_delay_val 0 again) the peer_delay input is<br>no longer relevant and can have arbitrary data. Must be<br>wired to 0 if unused. | Synchronous to (ref_clk)/2.                         | mq <n>_mac_<br/>peer_delay_va<br/>I[3:0]</n>   |

| <prefix>_mq<n>_pmac_pause_on</n></prefix>      | Output    | 32    | Transmit paused/class congestion Indication (8-bit value per channel) from eMAC/pMAC. Bit 0 (per channel, i.e., bits 0,8,16,24) is also used to indicate link pause. When asserted to '1' indicates a running pause counter that has                                                                                                                                                          |                                                     | mq <n>_pmac<br/>_pause_on[31:<br/>0]</n>       |

| <prefix>_mq<n>_emac_pause_on</n></prefix>      | Output    | 32    | been started because a Xoff frame (pause/PFC) was<br>received. In link pause mode, the transmitter is also stopped<br>when the command_config configuration bit<br>PAUSE_PFC_COMP is not set. When the<br>PAUSE_PFC_COMP bit is set, the transmitter will not be<br>stopped and it is the responsibility of the application to<br>assert mac_stop_tx to implement proper flow control.        | Synchronous<br>to ref_clk/2                         | mq <n>_emac<br/>_pause_on[31:<br/>0]</n>       |

| <prefix>_mq<n>_pmac_pause_en</n></prefix>      | Output    | 4     | General-purpose indication that the eMAC/pMAC is configured to react on pause frames (1-bit per channel). It is                                                                                                                                                                                                                                                                               | Synchronous<br>to reg_clk                           | mq <n>_pmac<br/>_pause_en[3:<br/>0]</n>        |

| <prefix>_mq<n>_emac_pause_en</n></prefix>      | Output    | 4     | a direct result of the inverted COMMAND_CONFIG<br>(PAUSE_IGNORE) control bit.                                                                                                                                                                                                                                                                                                                 |                                                     | mq <n>_emac<br/>_pause_en[3:<br/>0]</n>        |

| <prefix>_mq<n>_pmac_enable</n></prefix>        | Output    | 4     | General-purpose indication that the eMAC/pMAC datapaths<br>have been enabled. It is a direct result of both the<br>COMMAND_CONFIG(TX_EN & RX_EN) control bits. Per                                                                                                                                                                                                                            | Synchronous<br>to reg_clk                           | mq <n>_pmac<br/>_enable[3:0]</n>               |

| <prefix>_mq<n>_emac_enable</n></prefix>        | Output    | 4     | channel from 100G MACs. Can be left unconnected if not<br>used.           Note           ① A corresponding signal from the 200G MAC does<br>not exist.                                                                                                                                                                                                                                        |                                                     | mq <n>_emac<br/>_enable[3:0]</n>               |

| <prefix>_mq<n>_mac_tx_ovr_err</n></prefix>     | Output    | 4     | FIFO overflow truncation error indication. Asserts when the                                                                                                                                                                                                                                                                                                                                   |                                                     | mq <n>_mac_t<br/>x_ovr_err[3:0]</n>            |

| <prefix>_mq<n>_ffp_tx_ovr</n></prefix>         | Output    | 4     | FIFO write control logic had to truncate a frame as either the ff_tx_rdy deassertion was not respected by the application, or the frame transferred is larger than the FIFO                                                                                                                                                                                                                   |                                                     | mq <n>_ffp_tx<br/>_ovr[3:0]</n>                |

| <prefix>_mq<n>_ffe_tx_ovr</n></prefix>         | Output    | 4     | in store-and-forward mode of operation.                                                                                                                                                                                                                                                                                                                                                       |                                                     | mq <n>_ffe_tx<br/>_ovr[3:0]</n>                |

| <prefix>_mq<n>_mac_tx_underflow</n></prefix>   | Output    | 4     | Transmit FIFO became empty during transmission. A frame has been corrupted.                                                                                                                                                                                                                                                                                                                   | Synchronous to ref_clk/2                            | mq <n>_mac_t<br/>x_underflow[3:<br/>0]</n>     |

| Pin Name <sup>(1,2)</sup>                     | Direction | Width | Comments                                                                                                                                                                                                                                                               | Clock                                               | Raw Mode = 0<br>Data Going<br>to Ethernet                                                                                          |

|-----------------------------------------------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| <prefix>_mq<n>_pmac_tx_empty</n></prefix>     | Output    | 4     | Transmit FIFO Empty Indication from pMAC. When set to 1, indicates that the transmit FIFO is empty. When set to 0, indicates transmit FIFO has data. When the Quad operates in 200G, pmac_tx_empty[0] indicates empty for the 200G MAC FIFO.                           | Synchronous                                         | mq <n>_pmac<br/>_tx_empty[3:<br/>0]</n>                                                                                            |

| <prefix>_mq<n>_emac_tx_empty</n></prefix>     | Output    | 4     | Transmit FIFO Empty Indication from eMAC. When set to 1, indicates that the transmit FIFO is empty. When set to 0, indicates transmit FIFO has data. When the Quad operates in 200G, emac_tx_empty is unused/not relevant.                                             |                                                     | mq <n>_emac<br/>_tx_empty[3:<br/>0]</n>                                                                                            |

| <prefix>_mq<n>_mac_tx_isidle</n></prefix>     | Output    | 4     | Transmit datapath is not transmitting when 1. Will toggle during normal operation, but is not necessarily frame accurate (i.e., may not always de-assert during minimum IPG).                                                                                          | Synchronous<br>to ref_clk/2                         | mq <n>_mac_t<br/>x_isidle[3:0]</n>                                                                                                 |

| <prefix>_mq<n>_link_up</n></prefix>           | Input     | 4     | Per channel indication from the PCS that the link is up. The application must drive this signal from the PCS link_status, and potentially from loc_fault and rem_fault. It is used to detect a link loss in the MAC's transmit merge sub-layer to disable pre-emption. | Synchronous<br>to (ref_clk)/2                       | mq <n>_link_u<br/>p[3:0]</n>                                                                                                       |

| <prefix>_mq<n>_mac_tx_ts_val</n></prefix>     | Output    | 4     | Timestamp valid. Asserted for one clock cycle to indicate that mac_tx_ts_id and mac_tx_tsN are valid. The signal is not asserted for internally generated pause frames.                                                                                                | Synchronous to ref_clk/2                            | mq <n>_mac_t<br/>x_ts_val[3:0]</n>                                                                                                 |

| <prefix>_mq<n>_mac_tx_ts_id</n></prefix>      | Output    | 16    | Frame identifier return (4-bit value per channel). The value that was provided by the application at ff_tx_id(3:0) for the frame.                                                                                                                                      | Synchronous<br>to ref_clk                           | mq <n>_mac_t<br/>x_ts_id[4*4-1:<br/>0]</n>                                                                                         |

| <prefix>_mq<n>_mac_fault_ored4l</n></prefix>  | Output    | 1     | Local, remote, and link interruption faults. ORed into a single output.                                                                                                                                                                                                | Synchronous<br>to ref_clk/2                         | mq <n>_mac_l<br/>oc_fault[3:0])<br/>  <br/>( mq<n>_mac<br/>_rem_fault[3:<br/>0])   <br/>( mq<n>_mac<br/>_li_fault[3:0]</n></n></n> |

| <prefix>_mq<n>_mac_tx_ts</n></prefix>         | Output    | 256   | Frame timestamp value return (64-bit value per channel).<br>Transmit timestamp value for the frame sent with the frame<br>identifier set on mac_tx_ts_id. Returns the value sampled<br>from mac_frc_i_tx.                                                              | Synchronous<br>to ref_clk                           | mq1_mac_tx_t<br>s                                                                                                                  |

| 400G/200G MAC <sup>(3)</sup>                  |           |       |                                                                                                                                                                                                                                                                        |                                                     |                                                                                                                                    |

| <prefix>_m80_c<m>_xoff_gen</m></prefix>       | Input     | 8     | Transmit flow control generate. When PFC pause mode is enabled, an 8-bit input vector is used to signal the creation of PFC control frames. When link pause mode is enabled, bit 0 is used only.                                                                       | Asynchronous<br>input<br>synchronized<br>to ref_clk | m80_c <m>_xo<br/>ff_gen[7:0]</m>                                                                                                   |

| <prefix>_m80_c<m>_tx_smhold</m></prefix>      | Input     | 1     | Instructs the MAC to stop reading further data from the transmit FIFO at the next possible frame boundary.                                                                                                                                                             | Synchronous<br>to (ref_clk)/2                       | m80_c <m>_tx<br/>_smhold</m>                                                                                                       |

| <prefix>_m80_c<m>_peer_delay</m></prefix>     | Input     | 30    | Current value of the link delay measured at the ingress port<br>that receives SYNC messages from a master. This input is<br>a global value which is updated from time to time by the<br>PTP software when implementing peer-to-peer transparent<br>clock systems.      | Synchronous to ref_clk                              | m80_c <m>_p<br/>eer_delay[29:<br/>0]</m>                                                                                           |

| <prefix>_m80_c<m>_peer_delay_val</m></prefix> | Input     | 1     | Indicates validity of peer_delay(). Must be a pulse for one cdmii_txclk cycle whenever the peer_delay() input was updated.                                                                                                                                             | Synchronous to (ref_clk)/2.                         | m80_c <m>_p<br/>eer_delay_val</m>                                                                                                  |

| Pin Name <sup>(1,2)</sup>                   | Direction | Width | Comments                                                                                                                                                                                                                                                                                                                                         | Clock                       | Raw Mode = 0<br>Data Going<br>to Ethernet                       |

|---------------------------------------------|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------|

| <prefix>_m80_c<m>_pause_on</m></prefix>     | Output    | 8     | Transmit paused/class congestion indication, one bit per<br>priority class. When asserted to '1' indicates a running<br>pause counter has been started because an Xoff frame<br>(pause/PFC) was received. In link pause mode, the<br>transmitter is also stopped (if not disabled by<br>COMMAND_CONFIG.PAUSE_PFC_COMP configuration<br>setting). | Synchronous to ref_clk/2    | m80_c <m>_p<br/>ause_on[7:0]</m>                                |

| <prefix>_m80_c<m>_tx_ovr_err</m></prefix>   | Output    | 1     | FIFO overflow truncation error indication. Asserts when the FIFO write control logic had to truncate a frame as either the ff_tx_rdy de-assertion was not respected by the application, or the frame transferred is larger than the FIFO in store-and-forward mode of operation.                                                                 | Synchronous to ref_clk/2    | m80_c <m>_tx<br/>_ovr_err</m>                                   |

| <prefix>_m80_c<m>_tx_underflow</m></prefix> | Output    | 1     | Transmit FIFO became empty during transmission. A frame has been corrupted.                                                                                                                                                                                                                                                                      | Synchronous<br>to ref_clk/2 | m80_c <m>_tx<br/>_underflow</m>                                 |

| <prefix>_m80_c<m>_fault</m></prefix>        | Output    | 1     | Rx receives a local or remote fault.                                                                                                                                                                                                                                                                                                             | Synchronous<br>to ref_clk/2 | m80_c <m>_lo<br/>c_fault   <br/>m80_c<m>_re<br/>m_fault</m></m> |

| <prefix>_m80_c<m>_tx_ts</m></prefix>        | Output    | 64    | Frame timestamp value return (64-bit value per channel).<br>Transmit timestamp value for the frame sent with the frame<br>identifier set on mac_tx_ts_id. Returns the value sampled<br>from mac_frc_i_tx.                                                                                                                                        | Synchronous<br>to ref_clk   | m80_c <m>_tx<br/>_ts[63:0]</m>                                  |

| <prefix>_m80_c<m>_tx_ts_id</m></prefix>     | Output    | 4     | Frame identifier return (4-bit value per channel). The value that was provided by the application at ff_tx_id(3:0) for the frame.                                                                                                                                                                                                                | Synchronous<br>to ref_clk   | m80_c <m>_tx<br/>_ts_id[3:0]</m>                                |

| <prefix>_m80_c<m>_tx_ts_val</m></prefix>    | Output    | 1     | Timestamp valid. Asserted for one clock cycle to indicate that mac_tx_ts_id and mac_tx_tsN are valid. The signal is not asserted for internally generated pause frames.                                                                                                                                                                          | Synchronous<br>to ref_clk/2 | m80_c <m>_tx<br/>_ts_val</m>                                    |

| <prefix>_m80_c<m>_tx_empty</m></prefix>     | Output    | 1     | Transmit FIFO empty.                                                                                                                                                                                                                                                                                                                             | Synchronous<br>to ref_clk/2 | m80_c <m>_tx<br/>_empty</m>                                     |

| <prefix>_m80_c<m>_tx_isidle</m></prefix>    | Output    | 1     | Indicates (when 1) transmit state machine is not transmitting a frame currently.                                                                                                                                                                                                                                                                 | Synchronous<br>to ref_clk/2 | m80_c <m>_tx<br/>_isidle</m>                                    |

| <prefix>_m80_c<m>_frm_drop</m></prefix>     | Output    | 1     | Frame drop indication. A frame drop occurs when a frame contains less than 64 data bytes or the application was not ready to accept a frame ( $ff_x_rdy=0$ ) at begin of the frame. In both cases, the frame is not delivered to the application.                                                                                                | Synchronous to ref_clk/2    | m80_c <m>_fr<br/>m_drop</m>                                     |

| Common                                      |           |       |                                                                                                                                                                                                                                                                                                                                                  |                             |                                                                 |