# Speedster7t Configuration User Guide (UG094)

Speedster FPGAs

UG094 2.0 – April 02, 2024

# Copyrights, Trademarks and Disclaimers

Copyright © 2024 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedcore, Speedster, and ACE are trademarks of Achronix Semiconductor Corporation in the U.S. and/or other countries All other trademarks are the property of their respective owners. All specifications subject to change without notice.

#### Notice of Disclaimer

The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

# Achronix Semiconductor Corporation

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail: info@achronix.com

# Table of Contents

| Chapter 1 : | Overview                                             | 1  |

|-------------|------------------------------------------------------|----|

| Chapter 2 : | Interface Performance                                | 3  |

| Chapter 3 : | Bitstream Programming Modes for Speedster7t FPGAs    | 4  |

|             | Bitstream Programming Time                           | 5  |

|             | Bitstream Programming Via CPU                        | 5  |

|             | CPU Mode Bitstream Programming Flow                  | 5  |

|             | Generating the CPU Mode Bitstream Files From ACEACE  | 5  |

|             | How To Use the ACE-Generated CPU Bitstream File      | 6  |

|             | CPU Mode Hardware Interface                          | 7  |

|             | Bitstream Programming via Flash Memories             | 9  |

|             | Serial Flash Bitstream Programming Flow              | 9  |

|             | Generating the Serial Flash Bitstream Files from ACE | 9  |

|             | Using ACE-Generated Serial Flash Bitstream Files     | 11 |

|             | spi::program_bitstream Command                       | 11 |

|             | spi::program_all_bitstreams Command                  | 12 |

|             | Reading Back Data Stored In Flash                    | 13 |

|             | spi::read_bitstream Command                          | 13 |

|             | Serial Flash Hardware Interface                      | 14 |

|             | Flash Interface                                      | 15 |

|             | Flash Device Configurations                          | 16 |

| 1D Configuration                                          |    |

|-----------------------------------------------------------|----|

| 4D Configuration                                          | 17 |

| Addressing Modes and Memory Organization                  | 20 |

| Address Range                                             | 21 |

| Flash Configuration Header (PageO Header)                 | 21 |

| Flash Configuration Protocol                              | 23 |

| Flash Modes                                               | 24 |

| SPI Mode                                                  | 25 |

| Dual Mode                                                 | 25 |

| Quad Mode                                                 | 26 |

| Octa Mode                                                 | 27 |

| Flash Memory Size Requirements                            | 27 |

| Flash Configuration Using FTDI                            | 27 |

| FTDI Board-Level Device Connections                       | 28 |

| Bitstream Programming via JTAG                            | 30 |

| Generating the JTAG Bitstream Files From ACE              | 30 |

| How To Use the ACE-Generated JTAG Bitstream Files         | 30 |

| JTAG Programming using the ACE Download View              | 31 |

| ACE JTAG Connection Preference Page                       | 31 |

| ACE JTAG Download View                                    | 32 |

| JTAG Programming using the ACE Flow Steps                 | 34 |

| JTAG Programming using the Tcl Library API                | 36 |

| Variables Under ACE Tcl Console                           | 36 |

| Tcl Command Tables                                        | 37 |

| Programming the Board Using JTAG and Read/Write Registers | 43 |

| JTAG Hardware Overview                                    | 45 |

| Introduction                                              | 45 |

|             | JTAG Configuration Overview                            | 45 |

|-------------|--------------------------------------------------------|----|

|             | JTAG Instructions                                      | 49 |

|             | JTAG Configuration Using FTDI                          | 52 |

|             | Overview                                               | 52 |

|             | FTDI Board-Level Device Connections                    | 55 |

|             | FTDI Interface in ACE                                  | 62 |

|             | Programming Speeds and Requirements                    | 62 |

|             | Known Device Limitations                               | 63 |

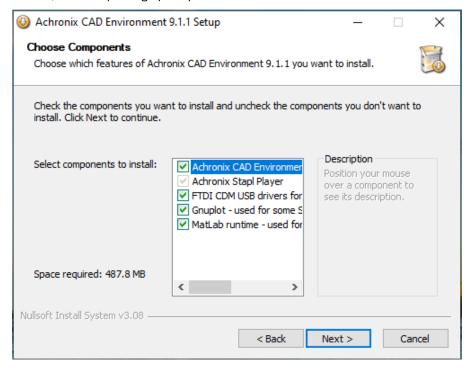

|             | Software and Driver Install for FTDI                   | 64 |

|             | Connecting the FTDI Device                             | 67 |

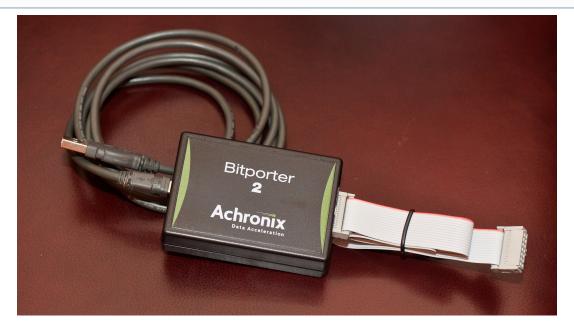

|             | JTAG Configuration Using the Bitporter2 Pod            | 68 |

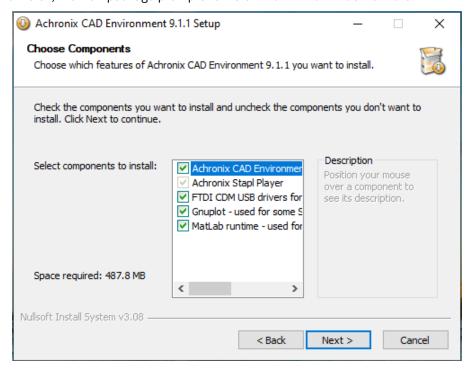

|             | Software and Driver Install for Bitporter2             | 69 |

|             | Connecting the Bitporter2 Pod                          | 71 |

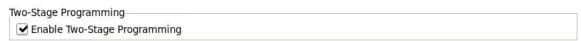

|             | Two-Stage Bitstream Programming via PCI Express        | 75 |

|             | PCIe Bitstream Programming Flow                        | 75 |

|             | Generating the PCIe Bitstream Files from ACE           | 75 |

|             | How to use the ACE-generated PCIe Bitstream FilesFiles | 76 |

| Chapter 4 : | FPGA Configuration Unit (FCU)                          | 77 |

|             | Overview                                               | 78 |

|             | Configuration Pin Tables                               | 79 |

| Chapter 5 : | Bitstream Generation Software Support in ACE           | 83 |

|             | Bitstream Generation                                   | 83 |

|             | Bitstream Output File Formats                          | 83 |

|             | Serial Flash Configuration Options                     | 85 |

|             |                                                        |    |

|             | Encryption Options                                | 87  |

|-------------|---------------------------------------------------|-----|

|             | Two-Stage Configuration Option                    | 89  |

|             | Partial Reconfiguration Configuration Options     | 90  |

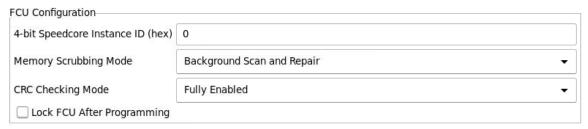

|             | FCU Configuration Options                         | 91  |

|             | Bitstream ID Configuration Options                | 92  |

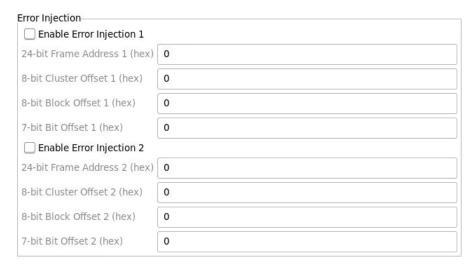

|             | CMEM Error Injection Options                      | 93  |

| Chapter 6 : | Configuration Sequence and Power-Up               | 95  |

|             | Device Power-Up                                   | 95  |

| Chapter 7 : | Configuration Error Correction and SEU Mitigation | 96  |

|             | Configuration Memory Architecture and Addressing  | 98  |

|             | Error Injection and Reporting                     | 100 |

|             | ACE Implementation Options                        | 100 |

|             | Bitstream Error Injection                         | 101 |

|             | Bitstream Single-Bit Error Injection Example      | 102 |

|             | Bitstream Dual-Bit Error Injection Example        | 103 |

|             | Scrubbing Reset                                   | 103 |

|             | Scrubbing FCU Registers                           | 104 |

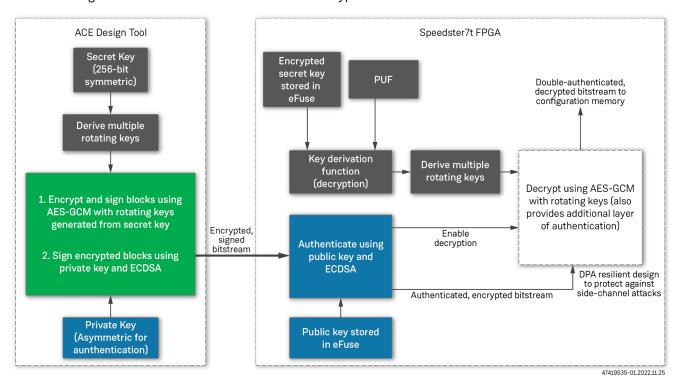

| Chapter 8 : | Design Security for Speedster7t FPGA              | 105 |

|             | Bitstream Authentication                          | 105 |

|             | Bitstream Encryption                              | 105 |

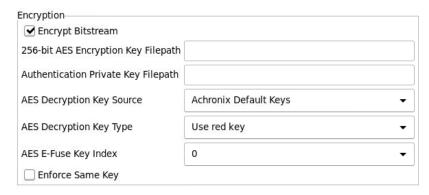

|             | Generating Encrypted Bitstreams                   | 106 |

|             | Encrypting a Speedster7t AC7t1500 Bitstream       | 107 |

|             | Using the ACE GUI                                 | 107 |

|             | Using Tcl Commands                                               | 108 |

|-------------|------------------------------------------------------------------|-----|

|             | Hardware Security                                                | 109 |

|             | Physically Unclonable Function                                   | 109 |

|             | Key Derivation Function                                          | 109 |

|             | Rules for Encryption                                             | 110 |

|             | Security Fuses                                                   | 111 |

|             | Fuses Set at Manufacturing                                       | 111 |

|             | Fuses Set By Customer                                            | 111 |

|             | Default Keys                                                     | 112 |

|             | Generating a Public and Private Key Pair on Speedster7t AC7t1500 | 112 |

|             | Programming the Encryption Keys Into Speedster7t AC7t1500 eFuses | 113 |

|             | Loading Encrypted Bitstreams                                     | 114 |

|             | Programming an AC7t1500 Encrypted Bitstream                      | 115 |

|             | Device DNA                                                       | 116 |

|             | ACE Placements to Read Device DNA                                | 116 |

| Chapter 9 : | Partial Reconfiguration                                          | 118 |

|             | Design Considerations                                            | 119 |

|             | Using Partial Reconfiguration                                    | 120 |

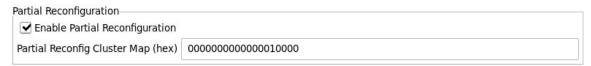

|             | ACE Implementation Options                                       | 120 |

|             | Partial Reconfiguration Steps                                    | 120 |

| Chapter 10  | : Speedster7t Configuration User Guide Revision History          | 121 |

|             | Revision History                                                 | 121 |

# Chapter 1: Overview

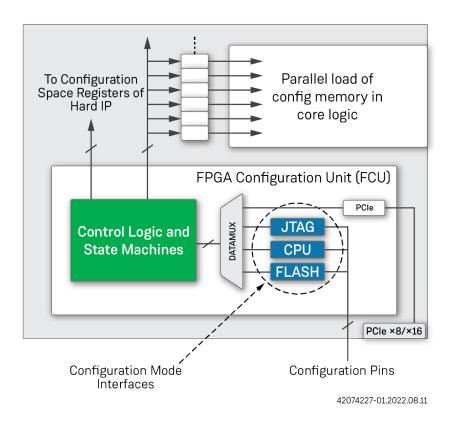

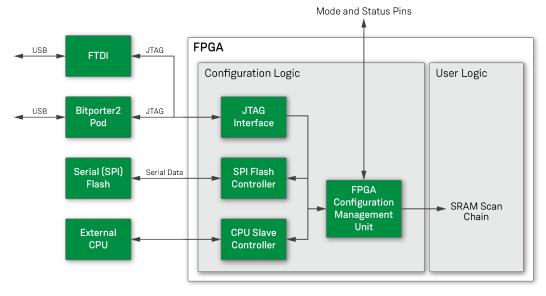

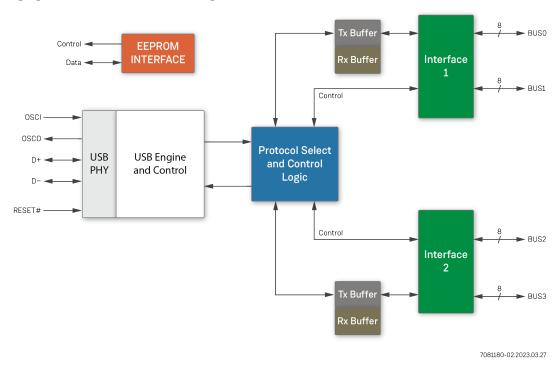

At startup, Speedster®7t FPGAs require configuration via a bitstream. This bitstream can be programmed through one of four available interfaces in the FPGA configuration unit (FCU), the logic controlling the configuration process.

The term FPGA configuration unit (FCU) refers to logic that controls the configuration (bitstream programming) process of the Speedster7t FPGA. This logic is responsible for the following:

- · Receiving data on a variety of external interfaces (depending on the selected programming mode)

- · Decoding instructions

- Sending configuration bit values to the appropriate destination (e.g., core configuration memory, the core boundary ring configuration memory, FCU registers, etc.)

- · Controls the startup and shutdown sequences that drive resets to the on-chip logic

- · Bitstream CRC checks

- · SEU mitigation with CMEM scrubbing

- · Bitstream Encryption Security

- · Any core-level housekeeping that occurs on the de-assertion of reset (i.e., clearing of configuration memory)

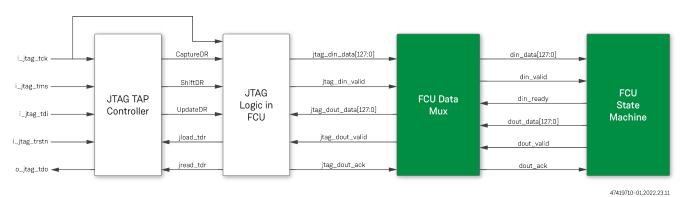

Data from the configuration pins is brought into the FCU located in the core boundary logic. Depending on the configuration mode, this data passes through one of four interfaces and is then provided to the control logic and state machines in the FCU. At this point, the data bus is standardized to a configuration mode independent common interface. Data is processed and propagated to the configuration registers in the core boundary ring, to the core configuration memory, or to the hard IP blocks in the FPGA I/O ring.

When all of the configuration bits are successfully loaded, the FCU transitions the Speedster7t FPGA into user mode, allowing full operation of the custom design.

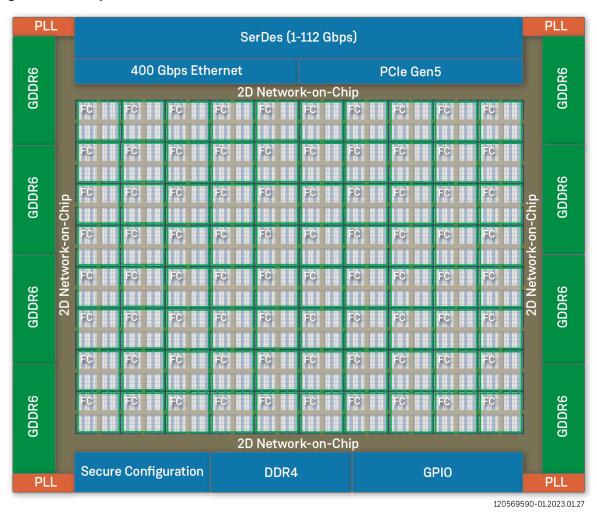

Figure 1 • Speedster7t Configuration Block

# Chapter 2: Interface Performance

The following table lists the various configuration interfaces supported by the Speedster7t FPGA and their corresponding maximum operating frequency.

Table 1 • Configuration Modes and Maximum Frequencies

| Configuration Mode | Maximum Frequency |

|--------------------|-------------------|

| JTAG               | 50 MHz            |

| CPU                | 250 MHz           |

| Serial flash       | 62.5 MHz          |

All of the programming modes and interfaces are capable of running up to 250 MHz at the configuration pins. The FCU and all associated circuitry are also capable of running up to 250 MHz. Since the internal data bus in the FCU is 128 bits wide, and in most configuration modes, the data pin count is less than 128, the incoming data stream goes through a gearbox to reduce the throughput. This configuration ensures that the internal programming circuitry runs at less than 250 MHz to process the incoming data stream. In the widest data mode (CPU ×128), the gearbox is bypassed and the entire configuration interface can run at the full 250 MHz bandwidth. Depending on the mode and configuration data width, the total bandwidth varies, and the programming time changes accordingly.

#### (i) Note

CPU x128 mode is primarily for ATE use and not a recommended mode for design configuration.

www.achronix.com 2.0 3

# Chapter 3 : Bitstream Programming Modes for Speedster7t FPGAs

Speedster7t FPGAs support four configuration modes:

- 1. Flash

- 2. JTAG

- 3. CPU

- 4. PCI Express

The selection between these modes is controlled by setting the FCU\_CONFIG\_MODESEL pins to the values shown in the following table. Both JTAG and PCle modes are independent of the FCU\_CONFIG\_MODESEL pin setting. The JTAG mode overrides all other configuration modes except PCle until disabled.

Table 2 • Pin Settings for Various Configuration Modes

| Configuration Mode                      | Data<br>Width | FCU_CONFIG_<br>MODESEL [3:0] | FCU_CONFIG_<br>SYSCLK_BYPASS <sup>(1)</sup> | FCU_CONFIG_<br>CLKSEL <sup>(1)</sup> |

|-----------------------------------------|---------------|------------------------------|---------------------------------------------|--------------------------------------|

| PCle                                    | -             | xxxx                         | х                                           | 0                                    |

| JTAG <sup>(2) (3)</sup>                 | _             | xxxx                         | Х                                           | 0/1                                  |

|                                         | 1 (SPI)       | 0001                         |                                             |                                      |

| Flash single device (1D) <sup>(4)</sup> | 2 (Dual)      | 1000                         |                                             |                                      |

| Flash single device (1D) (7             | 4 (Quad)      | 1010                         |                                             |                                      |

|                                         | 8 (Octa)      | 1100                         | 0/1                                         | 0                                    |

|                                         | 1 (SPI)       | 0010                         | 0/1                                         | G .                                  |

| Flash four devices (4D) <sup>(4)</sup>  | 2 (Dual)      | 1001                         |                                             |                                      |

| riasii iour devices (4D)                | 4 (Quad)      | 1011                         |                                             |                                      |

|                                         | 8 (Octa)      | 1101                         |                                             |                                      |

|                                         | 1             | 0011                         |                                             |                                      |

|                                         | 8             | 0100                         |                                             |                                      |

| CPU                                     | 16            | 0101                         | 1                                           | 0                                    |

|                                         | 32            | 0110                         |                                             |                                      |

|                                         | 128 (5)       | 0111                         |                                             |                                      |

| Configuration Mode  Data FCU_CONFIG_ FCU_CONFIG_ FCU_CONFIG_ SYSCLK_BYPASS (1) CLKSE |

|--------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------|

#### **Table Notes**

- 1. These straps select the configuration clock source:

- 0 on-chip oscillator clock

- 1 FCU\_CPU\_CLK

- 2. Always active. Enabled in the JTAG TAP controller.

- 3. If FCU\_CONFIG\_MODELSEL [3:0] pins are set such that flash or CPU configuration mode is selected, the JTAG override should be issued after flash programming has completed or the CPU mode interface is inactive.

- 4. In 1D mode, the flash bitstream is downloaded from one flash device. In 4D mode, the flash bitstream is downloaded from four flash devices.

- 5. Speedster7t FPGAs have 32 dedicated data I/O pins for the CPU interface supporting up to a ×32 interface. For ×128 mode, the upper 96 pins are shared with the DDR4 interface.

$\textbf{CAUTION:} \ \text{CPU} \ \text{x} 128 \ \text{is primarily for ATE use and not a recommended mode for design configuration}.$

# Bitstream Programming Time

Bitstream programming time is determined by the following formula in seconds:

(Total number of programming bits) / (programming data-width × clock frequency)

#### Note

When programming via JTAG, the clock frequency applied to the formula should be the frequency of JTAG. TCK.

# Bitstream Programming Via CPU

# **CPU Mode Bitstream Programming Flow**

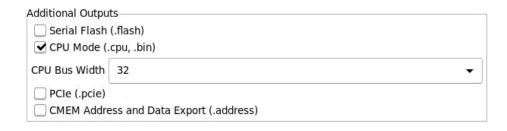

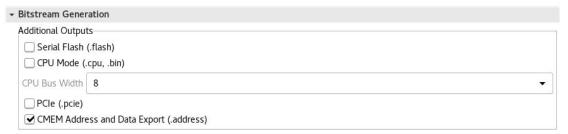

# Generating the CPU Mode Bitstream Files From ACE

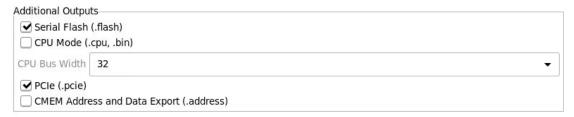

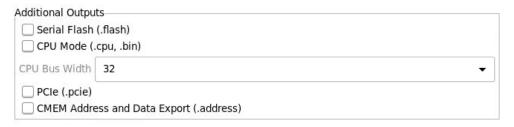

- 1. In ACE, select the CPU mode additional output.

- 2. Select the CPU bus width to generate .cpu and \_cpu.bin files for use in CPU programming mode as shown in the following example.

- 3. Run the Generate Bitstream flow step:

> run -step write\_bitstream

Figure 2 · ACE Additional Output Options Dialog

Table 3 · Bitstream Generation Implementation Options For CPU Mode

| Option          | ACE impl_option            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU Mode (.cpu) | bitstream_output_cpu       | Enables generation of an additional CPU mode (.cpu) formatted output file with the same name as the .hex file. The file contains hexadecimal-formatted data organized with "CPU bus width" number of bits per file line. File data is sent to the FCU CPU interface line by line (one line per clock cycle), where the left-most bit on each line is the MSB and the right-most bit is the LSB. In simulation, this file can be loaded using the readmemh function. For convenience, an additional binary representation of the CPU mode output (_cpu.bin) file is written with the same name as the .hex file. It contains the same data in the same bit order as the .cpu file but in a binary format with no new-lines. |

| CPU Bus Width   | bitstream_output_cpu_width | Controls the bit width of the CPU-mode formatted output file. When using the CPU interface in ×8 mode, set this value to 8. If using the CPU interface in ×32 mode, set this to 32. The value determines how many bitstream bits are printed per line in the . cpu output file. The bit sequence required by the FCU (and output in the generated bitstream file) might be different for each CPU bus width setting. It is important to set this option to match the actual CPU hardware interface width.                                                                                                                                                                                                                  |

#### How To Use the ACE-Generated CPU Bitstream File

There are two different CPU mode output file formats generated by ACE:

- 1. The \*.cpu file format. This file uses hexadecimal formatting and contains one CPU write per data line. If CPU bus width is set to 8, each line in the \*.cpu file contains eight bits of hex-formatted data in big-endian format.

- 2. The \*\_cpu.bin format. This file is a pure binary formatted file (with no newlines) and is formatted according to the CPU bus width in little-endian format. If CPU bus width is set to 8, every eight bits of binary file data represents the eight bits of data needed for each sequential CPU write.

To use either file format to program the ACE-generated bitstream into the FPGA, simply loop over the bitstream file from start to end and perform a CPU write operation with (CPU bus width) bits of data from the file on the FCU\_CPU\_DQ\_IN\_OUT bus. Details on the hardware interface follow.

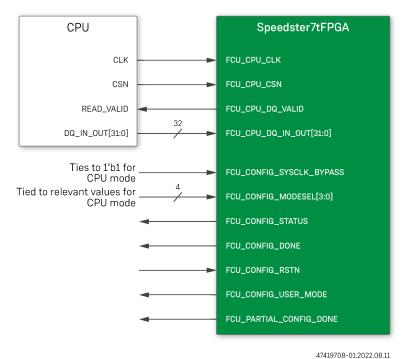

#### CPU Mode Hardware Interface

In CPU configuration mode, an external CPU controls the programming operations to the Speedster7t FPGA and offers a high-speed method for loading configuration data. Depending on the setting of the FCU\_CONFIG\_MODESEL pins, the CPU mode can be either a 1-, 8-, 16- or 32-bit wide parallel interface (128-bit wide is available for ATE test only). This interface is clocked using FCU CPU CLK with chip select support to indicate valid data. This mode supports a maximum clock rate of 250 MHz.

Figure 3 • External CPU Connectivity to a Speedster7t FPGA

#### (i) Note

The CPU only needs to connect to the first 1, 8, 16 or 32 bits of FCU\_CPU\_DQ\_IN\_OUT depending on the CPU mode selected. All unused signals should be tied to ground.

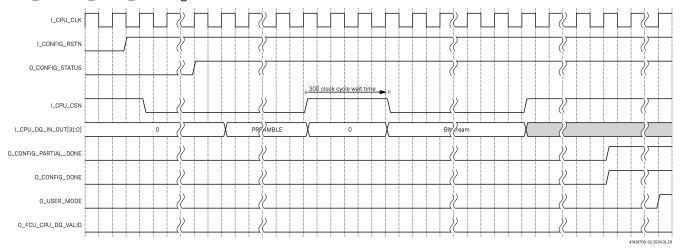

As described in the Configuration Sequence and Power-up (page 95) section, the configuration mode-specific operations occur between the release of FCU\_CONFIG\_STATUS (indicating that the configuration memory has been cleared and that the Speedster7t FPGA is ready to accept bitstream data) and the assertion of FCU\_CONFIG\_DONE (stating completion of configuration). The following example waveform for CPU×8 mode illustrates the sequence of events, clocking and control signal states needed for successful configuration in CPU mode:

1. After FCU\_CONFIG\_RSTN is de-asserted, FCU\_CPU\_CLK must continue to cycle to ensure that the FPGA cycles through the FCU states and the configuration memory is cleared. At that point, FCU\_CONFIG\_STATUS is driven high.

www.achronix.com 7 2.0

- 2. After at least 5 clock cycles of FCU\_CONFIG\_STATUS being driven high, FCU\_CPU\_CSN must be pulled low to begin writing the bitstream data into the Speedster7t FPGA. When the last set of data is written into the Speedster7t FPGA, FCU\_CPU\_CSN is pulled back high.

- 3. When FCU\_CPU\_CSN is pulled high, FCU\_CPU\_CLK must continue being clocked. When the FCU cycles through all of the configuration states, FCU\_CONFIG\_DONE is driven high to indicate that the Speedster7t FPGA was successfully programmed.

- 4. As the FCU\_CPU\_CLK toggles, the FCU cycles through its states to move the Speedster7t FPGA from programming mode into user mode, taking the fabric out of reset and performing operations to enable usermode functions for all parts of the core. The FCU\_CONFIG\_USER\_MODE signal is asserted to indicate when the Speedster7t FPGA has successfully transitioned into user mode.

At any point during the configuration, if FCU\_CPU\_CSN is asserted low, the FCU\_CPU\_DQ\_IN\_OUT bus should contain valid data or NOPs. A NOP is represented by logic 0 on all data pins. During this time, the FCU\_CPU\_DQ\_VALID pin should be held low, indicating that the data pins can be driven by a device external to the FPGA as mentioned in **Configuration Pin Tables** (page 79). If FCU\_CPU\_CSN is high, the data on FCU\_CPU\_DQ\_IN\_OUT is ignored. When the bitstream is programmed, FCU\_CPU\_CSN can be held low while sending NOPs to the Speedster7t FPGA. This action does not affect the assertion of FCU\_CONFIG\_DONE or FCU\_CONFIG\_USER\_MODE signals.

Figure 4 · Clocking and Control Signals for Successful Configuration

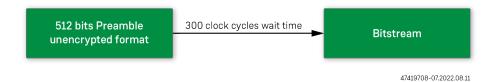

Figure 5 · Bitstream Data Sequence For Unencrypted Bitstream

#### (i) Note

During the 300 clock cycle wait time, CPU\_CSN is pulled high for encrypted bitstreams.

When programming an encrypted bitstream, there are additional wait clock cycle requirements. Please refer to the details in the Design Security for Speedster7t FPGA (page 105) section of this document.

# Bitstream Programming via Flash Memories

#### Caution!

Speedster7t FPGAs can interface to serial NOR flash devices only. Parallel NOR, NAND or other flash variants are not supported.

# Serial Flash Bitstream Programming Flow

#### Generating the Serial Flash Bitstream Files from ACE

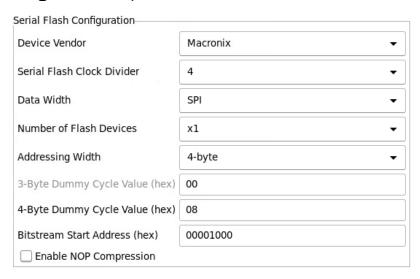

1. In ACE, select the Serial Flash additional output to generate the .flash and \_page0.flash files for use in Serial Flash programming mode as shown in the following example.

Figure 6 · ACE Additional Output Options Dialog

2. Run the Generate Bitstream flow step:

Table 4 · Bitstream Generation Implementation Options For Serial Flash Mode

| Option                | ACE impl_option        | Description                                                                                                                                                                                                                                                                           |

|-----------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Flash (.flash) | bitstream_output_flash | Enables generation of the serial flash-formatted .flash output file and the page0 header _page0 .flash files in addition to, and with the same name as, the default .hex file. The .flash file contains a binary image that can be directly loaded into a single serial flash memory. |

www.achronix.com 9 2.0

The following bitstream implementation options must be set correctly for the board serial flash hardware configuration.

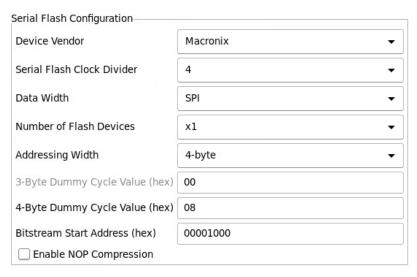

Figure 7 • ACE Serial Flash Configuration Options Dialog

Table 5 · Bitstream Generation Serial Flash Configuration Options

| Option                            | ACE impl_option                   | Description                                                                                                                                                  |

|-----------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Vendor                     | bitstream_page0_vendor            | Selects the flash device vendor. Allowed values:  Macronix (0)  Micron (1)                                                                                   |

| Serial Flash Clock Divider        | bitstream_page0_sf_clock_div      | Selects serial flash clock divider. Allowed values:  2  4  8                                                                                                 |

| Data Width                        | bitstream_page0_data_width        | Selects flash data readback width. Allowed values:  SPI (0)  DUAL (1)  QUAD (2)  OCT (3)                                                                     |

| Number of Flash Devices           | bitstream_page0_num_devices       | Selects number of devices based on targeted x1 or x4 PROM. Allowed values: x1 (0) x4 (1)                                                                     |

| Addressing Width                  | bitstream_page0_addr_width        | Selects 3-byte or 4-byte addressing mode to support flash devices >1Gb. Allowed values:  3-byte (0)  4-byte (1)                                              |

| 3-Byte Dummy Cycle Value<br>(hex) | bitstream_page0_dummy_cycle_3byte | Specifies the 3-byte addressing dummy cycle value. The default value is <b>00</b> and varies by device vendor. Must be specified as a 2-character hex value. |

| Option                            | ACE impl_option                   | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-Byte Dummy Cycle Value<br>(hex) | bitstream_page0_dummy_cycle_4byte | Specifies the 4-byte addressing dummy cycle value. The default value is <b>08</b> and varies by device vendor. Must be specified as a 2-character hex value.                                                                                                                                                                                                                                             |

| Bitstream Start Address           | bitstream_page0_start_addr        | Specifies the bitstream start address. Should be a non-zero multiple of 4096. Must be specified as an 8-character hex value.                                                                                                                                                                                                                                                                             |

| Enable NOP Compression            | bitstream_page0_compress_nops     | When unchecked (0), the $\star$ . flash file for I/O Ring programming is similar to other programming modes (CPU, JTAG, Hex, etc). When checked, the $\star$ . flash file bitstream contents are compressed, to help meet the 100ms PCIe link-up time. This results in a different bitstream for serial flash, which is dependent on the overall FCU data width (Number of Devices x Device Data Width). |

#### Using ACE-Generated Serial Flash Bitstream Files

The flash device is programmed using Tcl with .flash and \_page0.flash files. The spi::program\_all\_bitstreams ACE Tcl command is the recommended serial flash bitstream programming command because it automatically determines the offset and is useful for two-stage bitstream programming over PCle as discussed in the Two-Stage Bitstream Programming via PCl Express (page 75) section. If using spi::program\_bitstream, the command must be issued twice to first program the stage0 header flash file followed by programming the stage1 or full flash file at the specified offset.

#### spi::program\_bitstream Command

#### Example

spi::program\_bitstream <board\_config> <flash\_file> <number\_of\_proms> -device\_id

<pod\_name/FTDI\_device> -offset <int>

#### **Arguments**

Table 6 ⋅ spi::program\_bitstream Command Arguments

| Argument                                 | Default | Description                                                                                       |  |

|------------------------------------------|---------|---------------------------------------------------------------------------------------------------|--|

| <pre><board_config></board_config></pre> | -       | The board or part name of the targeted Achronix device (e.g., MEP/FT2232H or VectorPath/FT4232H). |  |

| <flash_file></flash_file>                | -       | The bitstream flash file to program from.                                                         |  |

| <number_of_proms></number_of_proms>      | -       | The number of PROM devices:  1 - single PROM 4 - x4 PROM                                          |  |

| Argument   | Default | Description                                                                                                                                                                                                              |  |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -device_id | -       | Argument followed by the Bitporter 2 pod name or FTDI device connected to the FPGA board. Use the JTAG Tcl command, jtag::get_connected_devices, to query available FTDI devices when more than one device is connected. |  |

| -offset    | 0       | Argument followed by the byte offset of the flash file within all of the PROMs. Must be specified when programming the .flash or _stage0.flash file.                                                                     |  |

## spi::program\_all\_bitstreams Command

#### Example

spi::program\_all\_bitstreams <board\_config> <page0\_file> <flash\_file> <number\_of\_proms>

-device\_id <pod\_name> -stage\_1\_header\_file <file\_name>

#### Arguments

Table 7 ⋅ spi::program\_all\_bitstreams Command Arguments

| Argument                                 | Default | Description                                                                                                                                                                                                              |

|------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre><board_config></board_config></pre> | -       | The board or part name of the targeted Achronix device (e.g., MEP/FT2232H or VectorPath/FT4232H).                                                                                                                        |

| <pre><page0_file></page0_file></pre>     | -       | The bitstream page0 flash file to program from: $\star$ _page0.flash for full flash file, or $\star$ _stage0_page0.flash for two-stage bitstream programming.                                                            |

| <flash_file></flash_file>                | -       | The bitstream flash file name: either .flash for full flash file, or *_stage0.flash for two-stage bitstream programming.                                                                                                 |

| <number_of_proms></number_of_proms>      | -       | The number of PROM devices:  1 - single PROM  4 - x4 PROM                                                                                                                                                                |

| -device_id                               | -       | Argument followed by the Bitporter 2 pod name or FTDI device connected to the FPGA board. Use the JTAG Tcl command, jtag::get_connected_devices, to query available FTDI devices when more than one device is connected. |

| -stage_1_header_file                     | -       | Argument followed by the ACE-generated bitstream binary stage1 header flash file to program from: *_stage1_header.flash (used only with two-stage encrypted bitstream programming over PCIe).                            |

#### Flash Programming Example

```

cmd> spi::program_bitstream config1 <flash_file> <number_of_proms> -offset 4096

-device_id <pod_name>

Device: config1 bringup board

Successfully opened SPI device: <pod_name>

205056 of 1333712 blocks written

410112 of 1333712 blocks written

615168 of 1333712 blocks written

820224 of 1333712 blocks written

1025280 of 1333712 blocks written

1230336 of 1333712 blocks written

Successfully programmed PROM devices with 1333968 bytes of data

```

#### Reading Back Data Stored In Flash

The contents stored in flash may be read back in ACE using the spi::read\_bitstream Tcl command which reads back the bitstream from the connected PROMs and outputs the contents to a file.

#### spi::read\_bitstream Command

#### Example

```

spi::read_bitstream <board_config> <flash_file> <number_of_proms> <number_of_bytes>

-device_id <pod_name> -offset <int>

```

#### **Arguments**

Table 8 ⋅ spi::read\_bitstream Command Arguments

| Argument                                       | Default | Description                                                                                                                  |  |

|------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------|--|

| <box><box<br></box<br>d_config&gt;</box>       | -       | The board or part name of the targeted Achronix device (e.g., MEP/FT2232H or VectorPath/FT4232H).                            |  |

| <flash_file></flash_file>                      | -       | The bitstream binary flash file to be written. A single file is written for either a single PROM or a x4 PROM configuration. |  |

| <number_of_proms></number_of_proms>            | -       | The number of PROM devices:  1 - single PROM 4 - x4 PROM                                                                     |  |

| <pre><number_of_bytes></number_of_bytes></pre> | -       | The total number of bytes to read back from all PROM devices.                                                                |  |

| Argument   | Default | Description                                                                                                                                                                                                              |  |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -device_id | -       | Argument followed by the Bitporter 2 pod name or FTDI device connected to the FPGA board. Use the JTAG Tcl command, jtag::get_connected_devices, to query available FTDI devices when more than one device is connected. |  |

| -offset    | 0       | Argument followed by the byte offset of the flash file within all of the PROMs.                                                                                                                                          |  |

#### Flash Readback Example

#### Serial Flash Hardware Interface

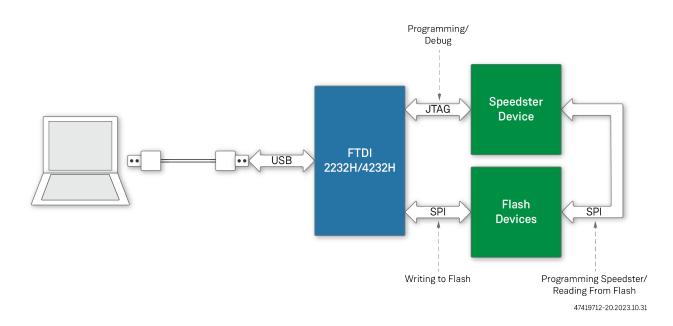

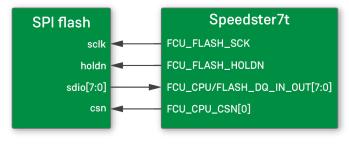

Flash programming mode allows configuring Speedster7t FPGAs with flash memories. In this mode, the FPGA controls the programming operations and supplies the clock to the flash memory.

The clock supplied from the FPGA (on the FCU\_FLASH\_SCK pin) to the attached flash device(s) can be driven either by the FCU\_CPU\_CLK or the on-chip oscillator clock depending on the configuration options selected as described in the Bitstream Programming Modes for Speedster7t FPGAs (page 4) chapter. The frequency of this clock can be selected from one of the variants of the clock sources arriving at the FCU: the divide-by-4 or divide-by-8. This selection is configured using the Serial Flash Clock Divider drop-down menu in the "Bitstream Generation Implementation Options" section of the ACE GUI. This setting ensures that only the flash state machine runs at the slower frequency. All other FCU and ACB logic continues to operate at the original input clock frequency. Details on downloading a bitstream into the flash devices via FTDI is presented in the Flash Configuration Using FTDI (page 27) chapter. It is very critical that the FTDI chip is used in combination with the FCU to write data to the flash devices. Therefore, all boards that intend to make use of flash configuration must have this component mounted accordingly. The following diagram details the appropriate connections needed to write to the flash devices and to subsequently program the Speedster7t FPGA.

Figure 8 • FTDI Cable Connection Detail

#### Note

At power-on, the device defaults to the divide-by-8 setting. The FCU then sets the appropriate configuration register to control the clock divider based on the user selection in ACE. The transition from a divide-by-8 clock to any other selected clock frequency is glitch free. Also, flash write is always SPI only while read can be in SPI, DUAL, QUAD or OCTA mode as summarized in the following table.

# Flash Interface

The configuration block is equipped with a flash interface that supports programming the FPGA from flash memory. A bitstream is assumed to be loaded into the flash memory using an external SPI interface. Flash registers within the configuration block assist with this process (refer to Registers and Addressing (page 0)). The complete feature list of the flash interface is described in the following table.

Table 9 • Flash Features

| Feature               | Description        |

|-----------------------|--------------------|

| Programming interface | SPI – JTAG, PCIe   |

| Security mode         | Double encryption. |

| Device mode           | X1, X4.            |

| Feature      | Description                                         |  |

|--------------|-----------------------------------------------------|--|

| Flash Read   | SPI, Dual, Quad, Octa.                              |  |

| Page0 Header | Holds read address, read counts, and read commands. |  |

# Flash Device Configurations

Speedster7t FPGAs support two flash device configurations:

- 1. Single flash device (1D).

- 2. Four flash devices (4D).

#### 1D Configuration

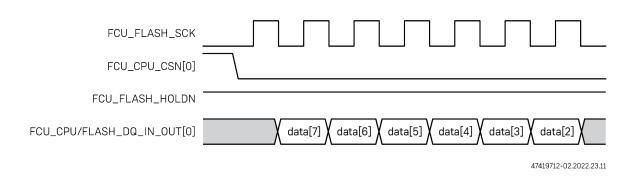

The 1D programming configuration is composed of a Speedster7t FPGA controlling communications with a single flash device. The o\_flash\_sck signal is used for clocking. The o\_flash\_sdi signal is the data output from the FPGA to communicate instructions to the flash device and i\_flash\_sdo[0] is the single-bit FPGA input pin which receives the bitstream from the flash in ×1 mode. The o\_flash\_csn[0] signal is pulled low as soon as communication between the FPGA and flash device begins, and stays low during the valid bitstream window.

The FPGA can communicate with the flash device in SPI, Dual, Quad or Octa modes in the 1D configuration.

The following figure provides a block diagram detailing how a serial flash device can be connected to a Speedster7t FPGA in Octa mode.

47419712-01.2022.08.11

Figure 9 · Speedster7t FPGA 1D Octa Mode Flash Programming Configuration

Figure 10 · 1D Flash SPI Read Data Ordering

### **4D Configuration**

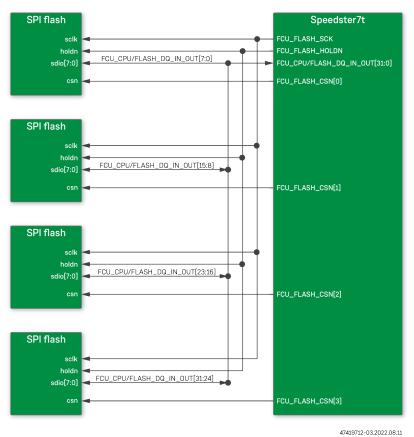

Serial 4D flash programming mode is essentially an enhanced and higher bandwidth implementation of the serial flash 1D configuration. The FPGA again controls communications and interfaces with not one but four flash memory devices to increase the data bandwidth four times.

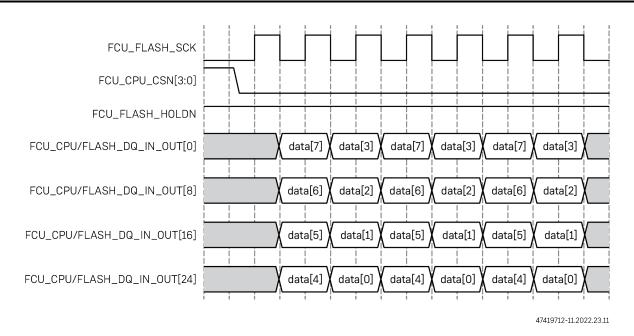

When writing to the four flash memories, all four chip selects, o\_flash\_csn[3:0], are pulled low simultaneously and 1-bit of bitsream data is sent to each flash device in SPI mode. When reading from the four flash memories, the FPGA pulls all of the o\_flash\_csn[3:0] signals low. Four-wide configuration data is read from the flash memories and transferred to the FPGA through the i\_flash\_sdo ports. When bitstream operations are complete (i.e., flash memory contents are read), transitioning from the end of the bitstream to user mode is performed as in CPU and flash 1D modes.

Each flash device can operate in SPI, Dual, Quad or Octa modes. The following figure provides a block diagram detailing how four serial flash devices (4D configuration) can be connected to a Speedster7t FPGA in Octa (x8) mode.

Figure 11 · Speedster7t FPGA 4D Flash Programming Configuration

Figure 12 · 4D Flash SPI Read Data Ordering

The FCU\_FLASH\_HOLDN signal must be held high at all times for both read and write accesses to the flash.

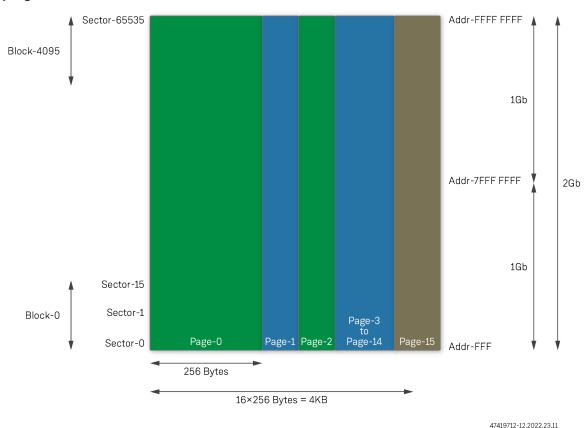

# Addressing Modes and Memory Organization

Addressing modes for flash memory are based on the size of the device. A three-byte addressing mode is required for 128 Mb flash and smaller, and a four-byte addressing mode is required to support memory sizes above 128 Mb. Writes to the flash memory occur as pages, with each page consisting of 256 bytes. The following figure shows the memory organization.

Figure 13 · Speedster7t FPGA Flash Memory Organization

#### **Address Range**

The following table shows the address ranges when two images are stored on a single flash device, assuming that each image is 1Gb in size.

Table 10 · Address Ranges For Two Bitstream Images on a Single Device

| Address Range<br>(32 bits)       | Description                                                                                                                                                                        | Configuration<br>Details                                                                                                                                       |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x0000_0000<br>to<br>0x0000_00FF | Page-0 address space. This range contains header information described in the flash configuration header section. This address range cannot be used for storing actual bitstreams. | These addresses are not user configurable.                                                                                                                     |  |

| 0x0000_1000<br>to<br>0x07FF_FFFF | FPGA current address space.                                                                                                                                                        | The start address can be configured via the current address in the page-0 header. This example assumes the address starts at 0x0000_1000 for a 1 Gb bitstream. |  |

# Flash Configuration Header (Page 0 Header)

#### Note

The page 0 header information does not need to be manually created. ACE generates the  $_{\rm page 0}$ . flash file during bitstream generation.

The first 256 bytes in the flash memory (page0) holds control information that describes how the subsequent bitstream should be read from the flash device. This information can be written to the flash device in two ways:

- 1. Via the JTAG interface along with the bitstream.

- 2. Pre-programmed into the device by the manufacturer.

This space is not used for storing the device bitstream. It is formatted as described in the following table and is generated by ACE when the flash file output option is selected according to the flash configuration options previously described.

Table 11 • Page 0 Header Format

| Address      | Bits | Value                                                    | Description                                                                                                                                                                                                                                                      | Device Specifics                          |

|--------------|------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 0x0 to 0x3   | 32   | Stage0 or full bitstream read address (new image).       |                                                                                                                                                                                                                                                                  |                                           |

| 0×4 to 0×7   | 32   | Bitstream read control.                                  | Bit 0 – flash read enable. Bit 1 – flash fall back enable. Bit [5:2] – retry count. Bit [21:6] – timeout count. Bit 22 – enable 4-byte addressing. Bit [27:23] – dummy read cycles. Bit [30:28] – flash SCK div count. Bit [31]: 1'b1 – Micron, 1'b0 – Macronix. | Bit 1 is 1 ' b0 for AC7t1500/<br>AC7t1450 |

| 0x8 to 0xB   | 32   | Flash configuration Stage0 or full bitstream read count. |                                                                                                                                                                                                                                                                  |                                           |

| 0xC to 0xF   | 32   | Read command.                                            |                                                                                                                                                                                                                                                                  |                                           |

| 0x18 to 0x20 | 24   | Reserved.                                                |                                                                                                                                                                                                                                                                  |                                           |

| 0×1C         | 8    | Page0 Header version.                                    | 0×01, Version 1 (as of ACE 9.1.1).                                                                                                                                                                                                                               |                                           |

| 0x28         | 2    | Bitstream mode.                                          | Bit 0 - NOT encrypted.<br>Bit 1 - full bitstream.                                                                                                                                                                                                                |                                           |

| 0x30 to 0x33 | 32   | Stage1 header read address (new image).                  | Calculated as stage0 read address + stage0 bitstream size (in bytes), aligned at 4kB boundary.                                                                                                                                                                   | AC7t1500/AC7t1450 only.                   |

| 0x38 to 0x3B | 32   | Flash configuration Stage1 header read count.            |                                                                                                                                                                                                                                                                  | AC7t1500/AC7t1450 only.                   |

| 0x40 to 0x43 | 32   | Number of wait cycles between Stage0 and Stage1.         |                                                                                                                                                                                                                                                                  | AC7t1500/AC7t1450 only.                   |

# Flash Configuration Protocol

With the FCU\_CONFIG\_MODESEL[3:0], FCU\_CONFIG\_CLKSEL and FCU\_CONFIG\_SYSCLK\_BYPASS straps set for serial flash programming, operations begin as soon as the FPGA is powered up and the FCU receives the clock input. Immediately after reset is released, bitstream data is read out from the flash device through the flash interface (at this time the default is SPI (×1) mode). The bitstream read is performed in two stages described as follows:

Stage 1 - flash configuration header read from flash device:

- The FCU sends a default read command and address of 0x0000\_0000 (32 bits) in SPI mode to the flash device and reads the flash configuration header.

- · Internal registers are then updated, including the start address for the bitstream and flash read command.

#### Stage 2 - bitstream read from flash device:

- Based on the read mode obtained from the flash configuration header (×1/×2/×4/×8), the command and start address are sent to the flash device.

- The FCU reads the first 512 bits of bitstream data from the flash device and enters a wait state.

- If encryption is not enabled, the FCU reads the complete bitstream and configures the FPGA. If encryption is enabled and the efuse key is ready, the FCU reads the header segment0 data and sends it to the secure boot core. The flash read state machine then waits for 2.6 ms after which the FCU reads the complete bitstream and configures the FPGA.

Bitstream programming in all configuration modes is MSB to LSB. For transmitting a 32-bit FCU command, the ordering in the serial ×1 mode for 1D and 4D configuration is as follows:

- 1D flash configuration the flash device transmits command bit 31 on the first clock and bits 30, 29, 28, etc. on subsequent clocks all the way down to bit 0 on the 32<sup>nd</sup> (last) clock.

- 4D flash configuration the four flash devices transmit command bits [31:28] on the first clock, all the way down to bits [3:0] on the eighth (last) clock. The ordering within the 4-bit nibble corresponds to the flash device ordering. Specifically, on the first clock, flash[3] transmits bit 31, flash[2] transmits bit 30, flash[1] transmits bit 29 and flash[0] transmits bit 28

#### Flash Modes

The following section describes the various modes supported for read operations from attached flash device(s). Read operations from the flash device can be configured either as SPI, quad or octa modes for both 1D and 4D configurations. To write to the flash device(s), please consult the Flash Configuration Using FTDI (page 27) section.

#### (i) Note

A flash write can be performed via either the JTAG or PCIe modes. The PCIe or JTAG port can access the data and command registers using an indirect addressing mode.

The following table describes the different combinations of the flash device configurations and modes supported in the Speedster7t FPGA.

Table 12 • Flash Device Configurations and Modes

| Flash Programming<br>Mode/Configuration | Flash Interface Width | No. of Flash Devices | Read Width<br>SO[n:0] × No. of Flash<br>Devices |

|-----------------------------------------|-----------------------|----------------------|-------------------------------------------------|

| SPI (1D)                                | 1                     | 1                    | 1                                               |

| SPI (4D)                                | 1                     | 4                    | 4                                               |

| Dual (1D)                               | 2                     | 1                    | 2                                               |

| Dual (4D)                               | 2                     | 4                    | 8                                               |

| Quad (1D)                               | 4                     | 1                    | 4                                               |

| Quad (4D)                               | 4                     | 4                    | 16                                              |

| Octa (1D)                               | 8                     | 1                    | 8                                               |

| Octa (4D)                               | 8                     | 4                    | 32                                              |

www.achronix.com 2.0 24 Following are read operation timing diagrams for each of the flash interface widths.

#### (i) Note

These diagrams pertain to Macronix devices. For details regarding other device vendors, please consult the flash device vendor datasheet.

#### **SPI Mode**

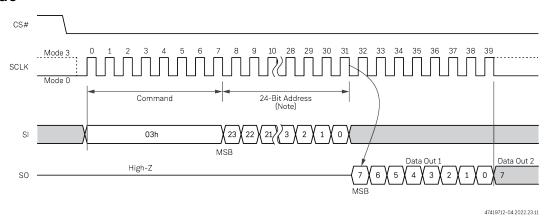

Figure 14 · SPI Read Mode Timing

#### **Dual Mode**

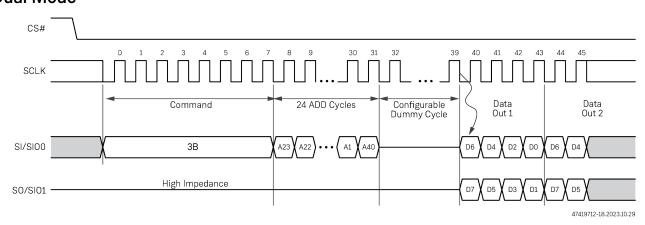

Figure 15 · Dual Read Mode (DREAD) Timing

www.achronix.com 2.0 25

47419712-07.2022.23.11

#### **Quad Mode**

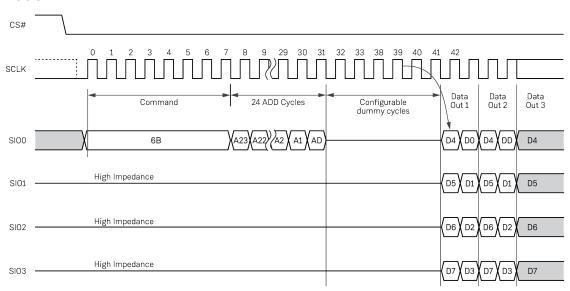

Figure 16 • Quad Read Mode (QREAD) Timing

#### Octa Mode

#### Warning!

#### **Octa Mode Device Limitations:**

For Octa Mode, Speedster7t devices currently only support flash devices in the 1-1-8 mode.

For context, normally flash devices have a SPI sequence that sets a configuration register value that fully converts everything to octa. Command, address, (return) data are all in octa: 8-bits on 8 lines throughout, or 8-8-8 mode. Some flash devices have a read command that works more like QSPI, and does not require writing a configuration register to enable. The command and address are sent on a single line (SDI) similar to SPI, and after a fixed number of dummy cycles, the data is read on all 8 lines. This is referred to as 1-1-8 mode.

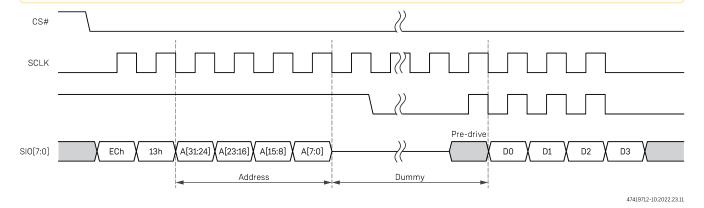

The following figure represents 8-8-8 mode.

Figure 17 · Octa Read Mode (8READ) Timing

# Flash Memory Size Requirements

As a general rule of thumb to cover the largest bitstream size, a 1 Gb flash memory is recommended to store one bitstream.

#### Note

Please work with the Achronix support team to evaluate the best Flash device size for any specific target device and end user design application.

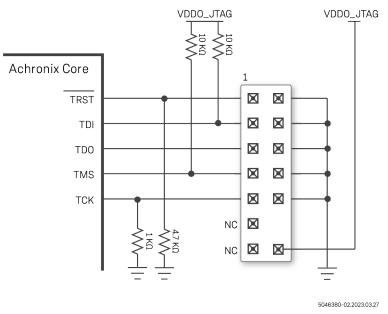

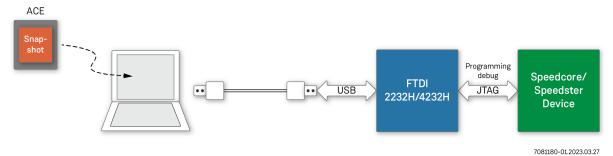

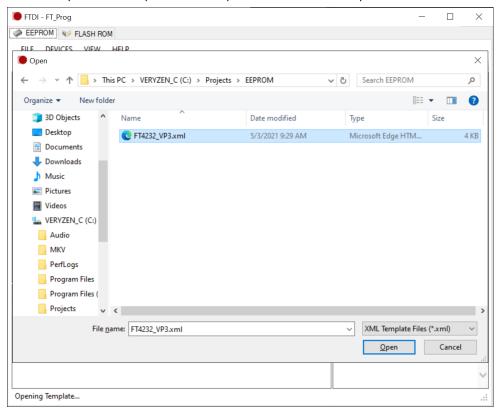

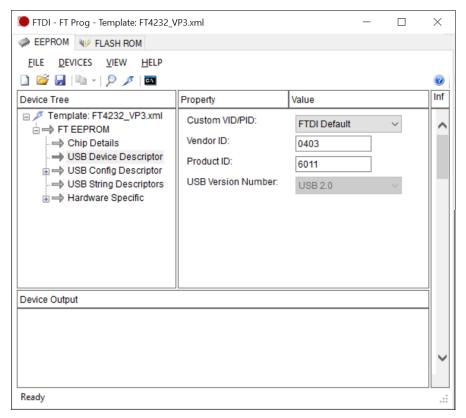

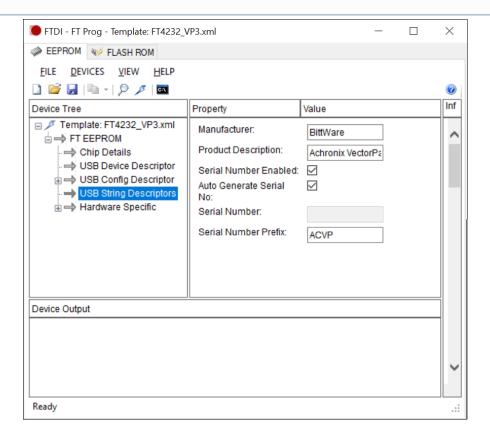

# Flash Configuration Using FTDI

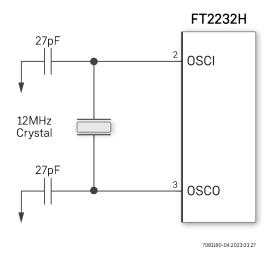

The FTDI device multi-protocol synchronous serial engine (MPSEE) is configured for USB-to-SPI communication to program the flash device. SPI protocol lines are implemented using the MPSEE channels ADBUS0-7, ACBUS0, ACBUS3, and BCBUS5.

www.achronix.com 27 2.0

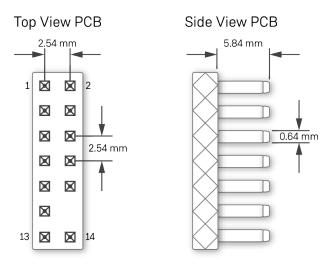

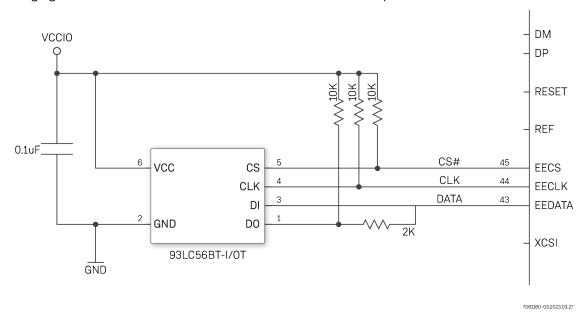

#### FTDI Board-Level Device Connections

ACE supports flash programming for three types of pin-out connections from FTDI to the flash device:

- · Configuration 1

- · Configuration 2

- · Configuration 3

The FTDI devices supported by ACE are FT2232 and FT4232H. For pin-out connections config1 and config3, the signal SPI\_MODE\_EN is not required but can be used in situations where a multiplexer is placed between the FTDI device and another device that can access the flash memory. The three configuration connection types are described in the following tables.

#### FTDI Flash Pinout To FT2232

Table 13 • FTDI FT2232-to-Flash Connections (Configuration 1)

| FTDI<br>Port Name | FTDI Device<br>Pin Number | FTDI<br>Net name | Flash<br>Pin |

|-------------------|---------------------------|------------------|--------------|

| ADBUS0            | 16                        | FTDI_AD0         | SPI_CLK      |

| ADBUS1            | 17                        | FTDI_AD1         | FCU_DQ1      |

| ADBUS2            | 18                        | FTDI_AD2         | FCU_DQ9      |

| ADBUS3            | 19                        | FTDI_AD3         | FCU_DQ17     |

| ADBUS4            | 21                        | FTDI_AD4         | FCU_DQ25     |

| ADBUS5            | 22                        | FTDI_AD5         | SPI_SDI      |

| ADBUS6            | 23                        | FTDI_AD6         | SPI_CS_N[3]  |

| ADBUS7            | 24                        | FTDI_AD7         | SPI_CS_N[2]  |

| ACBUS0            | 26                        | FTDI_ACBUS[0]    | SPI_CS_N[0]  |

| ACBUS3            | 29                        | FTDI_ACBUS[3]    | SPI_CS_N[1]  |

| BCBUS5            | 57                        | FTDI_BCBUS[5]    | SPI_MODE_EN  |

#### FTDI Flash Pinout To FT4232H

Table 14 • FTDI FT4232-to-Flash Connections (Configuration 2)

| FTDI<br>Port Name | FTDI Device<br>Pin Number | FTDI<br>Net name | Flash<br>Pin |

|-------------------|---------------------------|------------------|--------------|

| ADBUS0            | 16                        | FTDI_AD0         | SPI_CLK      |

| ADBUS1            | 17                        | FTDI_AD1         | NC           |

| ADBUS2            | 18                        | FTDI_AD2         | SPI_CS_N[1]  |

| ADBUS3            | 19                        | FTDI_AD3         | SPI_CS_N[2]  |

| ADBUS4            | 21                        | FTDI_AD4         | SPI_CS_N[3]  |

| ADBUS5            | 22                        | FTDI_AD5         | SPI_MOSI     |

| ADBUS6            | 23                        | FTDI_AD6         | SPI_MISO     |

| ADBUS7            | 24                        | FTDI_AD7         | SPI_CS_N[0]  |

#### (i) Note

Configuration 2 is the hardware configuration used with the VectorPath® S7t-VG6 accelerator card.

#### FTDI Flash Pinout To FT2232/4232H

Table 15 • FTDI FT2232/4232H-to-Flash Connections (Configuration 3)

| FTDI<br>Port Name | FTDI Device<br>Pin Number | FTDI<br>Net name | Flash<br>Pin |

|-------------------|---------------------------|------------------|--------------|

| ADBUS0            | 16                        | FTDI_AD0         | SPI_CLK      |

| ADBUS1            | 17                        | FTDI_AD1         | SPI_MOSI     |

| ADBUS2            | 18                        | FTDI_AD2         | SPI_MISO     |

| ADBUS3            | 19                        | FTDI_AD3         | SPI_CS_N[2]  |

| ADBUS4            | 21                        | FTDI_AD4         | SPI_CS_N[3]  |

www.achronix.com 2.0 29

| FTDI<br>Port Name | FTDI Device<br>Pin Number | FTDI<br>Net name | Flash<br>Pin |

|-------------------|---------------------------|------------------|--------------|

| ADBUS5            | 22                        | FTDI_AD5         | SPI_CS_N[0]  |

| ADBUS6            | 23                        | FTDI_AD6         | SPI_CS_N[1]  |

| BCBUS5            | 57                        | FTDI_BCBUS[5]    | SPI_MODE_EN  |

## (i) Note

If using configuration 3 with the FTDI FT4232H, the SPI\_MODE\_EN pin is not used because it is not available on that device.

# Bitstream Programming via JTAG

# Generating the JTAG Bitstream Files From ACE

The JTAG . hex file is the default file and is always generated when running the Generate Bitstream flow step (run -step write\_bitstream). Advanced bitstream features are covered in the Design Security for Speedster7t FPGA (page 105), Partial Reconfiguration (page 118), and Configuration Error Correction and SEU Mitigation (page 96) sections.

# How To Use the ACE-Generated JTAG Bitstream Files

There are three ways to program a JTAG bitstream . hex file created during the Generate Bitstream flow step to program over JTAG. These methods are detailed in the following pages.

- JTAG Programming using the ACE Download View (page 31)

- · JTAG Programming using the ACE Flow Steps (page 34)

- JTAG Programming using the Tcl Library API (page 36)

www.achronix.com 2.0 30

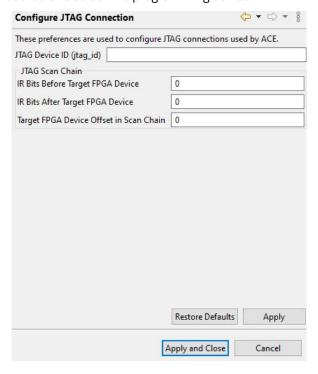

# JTAG Programming using the ACE Download View

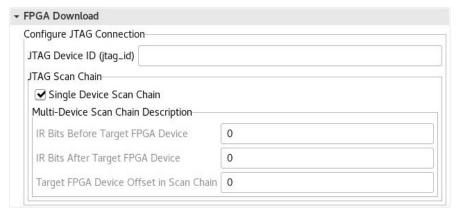

# **ACE JTAG Connection Preference Page**

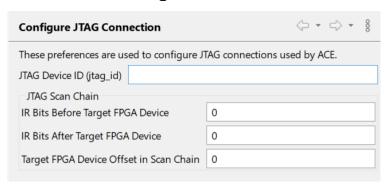

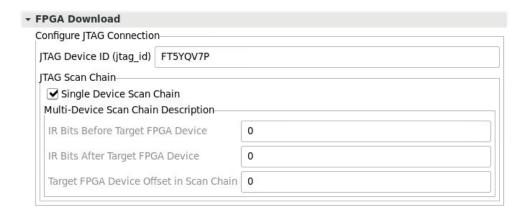

Figure 18 · Configure JTAG Connection Preference Page Example

**Table 16 · Configure JTAG Interface Preference Page Options**

| Option                                      | Description                                                                                                                                                                                           |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | The name of the JTAG device which should be used for all ACE JTAG interactions with the chosen FPGA or eFPGA. If the name is not specified, auto-detection of JTAG devices is attempted.              |

| JTAG Programmer Device Name (1)             | Performance Tip                                                                                                                                                                                       |

| JIAG Programmer Device Name **              | Even if only one JTAG device is connected, specifying the JTAG device by name (instead of relying upon autodetection) can save up to several seconds of initialization time on every JTAG connection. |

| JTAG Scan Chain                             |                                                                                                                                                                                                       |

| IR Bits Before the Target FPGA Device (2)   | Sets the (decimal) number of instruction register bits between the board JTAG TDI pin and the target device.                                                                                          |

| IR Bits After the Target FPGA Device (2)    | Sets the (decimal) number of instruction register bits between the target device and the board JTAG TDO pin.                                                                                          |

| Target FPGA Device Offset in Scan Chain (2) | Sets the device count (in decimal) between the board JTAG TDI pin and target FPGA device.                                                                                                             |

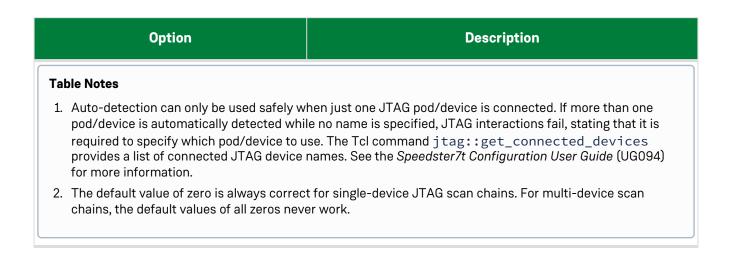

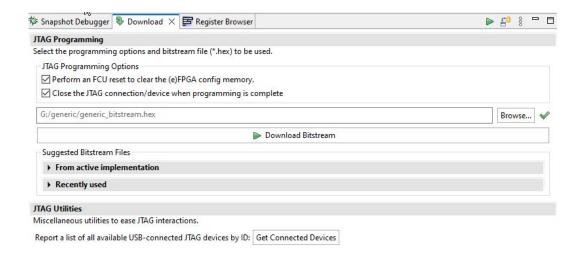

## **ACE JTAG Download View**

The Download view provides a graphical interface for choosing and downloading (via JTAG) a bitstream  $\star$ . hex file to an Achronix FPGA connected to the workstation using USB via a Bitporter2 pod or FTDI FT2232H or FT4232H device.

Figure 19 · Download View Example

Table 17 • Download View Options

| Option             |                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Programmir    | ng                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | JTAG Programming Options                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | Perform an FCU reset to clear the (e)FPGA config memory.         | When checked, performs a soft reset and clears all device configuration memory before beginning programming. This reset is typically only disabled for multi-stage programming (after stage 0 programming has completed, before programming later stages begins), or for "partial reconfig" when partial bitstreams are in use (see the chapter titled Partial Reconfiguration in the Speedster7t Configuration User Guide (UG094) for more details). |

| Browse             |                                                                  | Allows choosing any * . hex bitstream file from the file system using a graphical file system browser.                                                                                                                                                                                                                                                                                                                                                |

| Download Bitstream |                                                                  | Pressing this button performs the actual download by calling the appropriate Tcl commands in the jtag:: namespace. See also: Speedster7t Configuration User Guide (UG094).                                                                                                                                                                                                                                                                            |

|                    | Suggested Bitstream Files                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | From active implementation.                                      | A list of all *.hex bitstream files (shown as hyperlinks) found in the output directory of the current Active Implementation. Select any of these hyperlinks to choose that file for download.                                                                                                                                                                                                                                                        |

|                    | Recently used.                                                   | A list of the most recently used $\star$ . hex bitstream files (shown as hyperlinks). Select any of these hyperlinks to choose that file for download.                                                                                                                                                                                                                                                                                                |

| JTAG Utilities     |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | Report a list of all available USB-connected JTAG devices by ID. | Press the button to run a Tcl command (jtag::get_connected_devices) to report a list of all connected JTAG devices in the Tcl Console view.                                                                                                                                                                                                                                                                                                           |

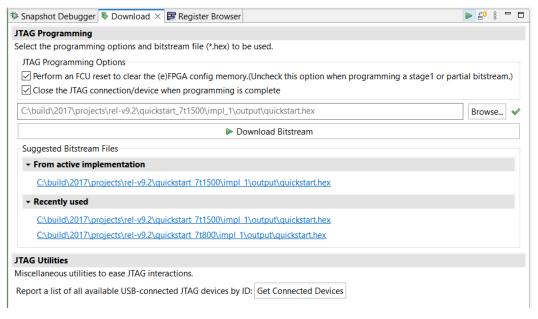

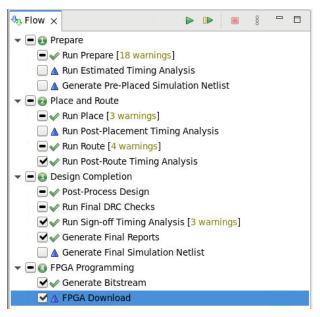

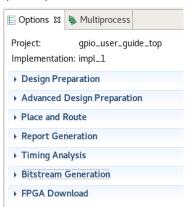

# JTAG Programming using the ACE Flow Steps

ACE has a flowstep that, upon completion of the "Generate Bitstream" flowstep, allows downloading a generated bitstream into a connected Speedster7t FPGA.

Figure 20 · ACE FPGA Download Flow Step

Figure 21 · ACE FPGA Download Options Dialog

Table 18 • FPGA Download Implementation Options - JTAG Scan Chain

| Option                   | ACE impl_option         | Description                                                                                                                                                                                                                                                |

|--------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Device ID (jtag_id) | download_jtag_id        | Specifies the JTAG programming device name to attempt connecting to during FPGA download. If not populated, autodetection of JTAG programming devices is attempted, and the download fails if more than one JTAG device is auto-detected.                  |

| Single Device Chain      | download_single_device  | This option should be enabled when the target is the only device on the JTAG scan chain (single-device JTAG scan chain). If this option is set to 0, the pre-IR, post-IR, and chain offset options are used to configure the scan chain.                   |

| IR Bits Before Target    | download_preir_padding  | Sets the (decimal) number of instruction register bits between the board JTAG TDI pin and the target device instruction register. Used for multi-device scan chains in order to pad the IR chain properly with ones, placing other devices in bypass mode. |

| IR Bits After Target     | download_postir_padding | Sets the (decimal) number of instruction register bits between the target device and the board JTAG TDO pin. Used for multi-device scan chains in order to pad the IR chain properly with ones, placing other devices in bypass mode.                      |

| Chain Offset of Target   | download_chain_offset   | Sets the device count (in decimal) between the board JTAG TDI pin and target FPGA device. Setting this to 1 selects the second device on the chain, and so on.                                                                                             |

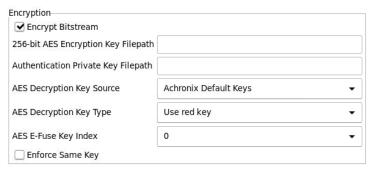

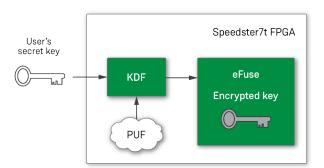

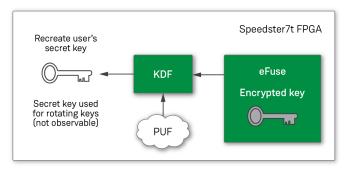

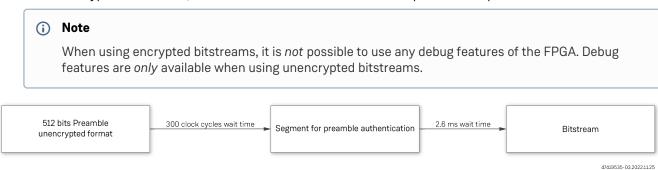

# JTAG Programming using the Tcl Library API