**Speedster FPGAs**

**Preliminary Data**

**Preliminary Data**

# Copyrights, Trademarks and Disclaimers

Copyright © 2021 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedcore, Speedster, and ACE are trademarks of Achronix Semiconductor Corporation in the U.S. and/or other countries All other trademarks are the property of their respective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

### **Preliminary Data**

This document contains preliminary information and is subject to change without notice. Information provided herein is based on internal engineering specifications and/or initial characterization data.

### Achronix Semiconductor Corporation

2903 Bunker Hill Lane Santa Clara, CA 95054 USA Website: www.achronix.com

E-mail : info@achronix.com

# **Table of Contents**

| Chapter - 1: Overview                                                         | 6  |

|-------------------------------------------------------------------------------|----|

|                                                                               |    |

| Chapter - 2: Interface Performance                                            |    |

| Chapter - 3: Configuration Modes for Speedster7t FPGAs                        |    |

| Configuration via CPU                                                         |    |

| Programming Data Ordering                                                     | 13 |

| Configuration via Flash Memories                                              |    |

| Flash Interface                                                               |    |

| Flash Device Configurations                                                   |    |

| Addressing Modes and Memory Organization         Flash Configuration Protocol |    |

| Flash Modes                                                                   |    |

| Registers and Addressing                                                      |    |

| Configuration via JTAG                                                        |    |

| JTAG Instructions                                                             |    |

| Chapter - 4: Configuration Pin Tables                                         | 33 |

| Chapter - 5: FPGA Configuration Unit (FCU)                                    |    |

| Overview                                                                      | 37 |

| Speedster 7t1500 FCU Command List                                             |    |

| Command Formats and Details                                                   | 38 |

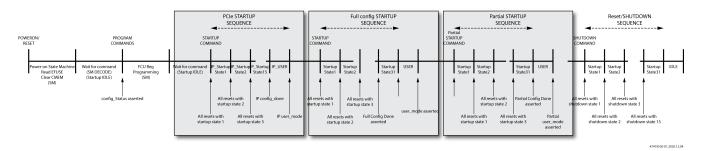

| Chapter - 6: Configuration Sequence and Power-Up                              | 50 |

| Device Power-Up                                                               | 50 |

| Read Non-Volatile Memories                                                    | 51 |

| Clear Configuration Memory                                                    | 51 |

| Bitstream Sync, JTAG ID and Instance ID                                       | 53 |

| Load Configuration Bits                                                       | 53 |

| CRC                                                                           | 54 |

| Startup Sequence                                                              |    |

| User Mode                                                                     |    |

| Chapter - 7: Speedster7t Bitstream Generation                                 | 56 |

| Chapter - 8: Achronix Configuration Bus (ACB)                                                                                            |        |

|------------------------------------------------------------------------------------------------------------------------------------------|--------|

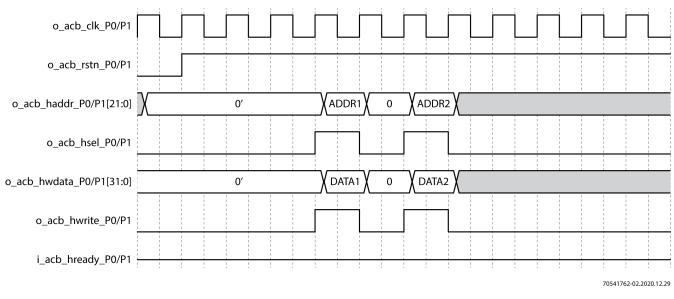

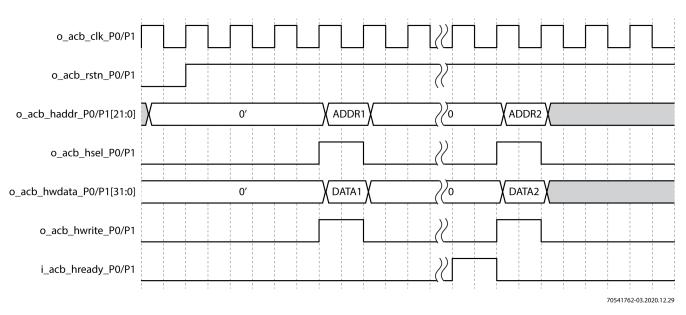

| ACB Address Space                                                                                                                        | 2      |

| ACB Write and Read Protocols                                                                                                             | 3      |

| Read from Memory                                                                                                                         | 5      |

| Chapter - 9: Partial Reconfiguration 6                                                                                                   | 7      |

| Design Considerations                                                                                                                    | 3      |

| Partial Reconfiguration Steps                                                                                                            | 3      |

| Chapter - 10: Remote Update                                                                                                              | 9      |

| Introduction                                                                                                                             | 9      |

| Implementation       70         Fallback on Error       7                                                                                |        |

| Chapter - 11: Design Security for Speedster 7t FPGA                                                                                      | 2      |

| Bitstream Authentication                                                                                                                 | 2      |

| Bitstream Encryption    72      Generating Encrypted Bitstreams    73      Hardware Security    73                                       | 3      |

| Security Fuses       74         Fuses Set at Manufacturing       74         Fuses Set By Customer       74         Default Keys       76 | 5<br>5 |

| Loading Encrypted Bitstreams                                                                                                             | 3      |

| Chapter - 12: eFuse                                                                                                                      | 7      |

| Revision History                                                                                                                         | )      |

# Chapter - 1: Overview

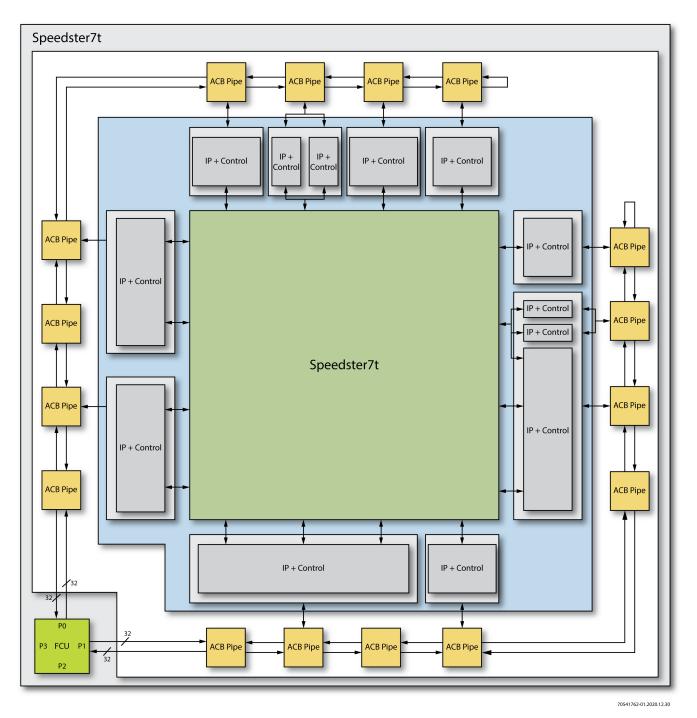

At startup, Speedster7t FPGAs require configuration by the end user via a bitstream. This bitstream can be programmed through one of four available interfaces in the FPGA configuration unit (FCU).

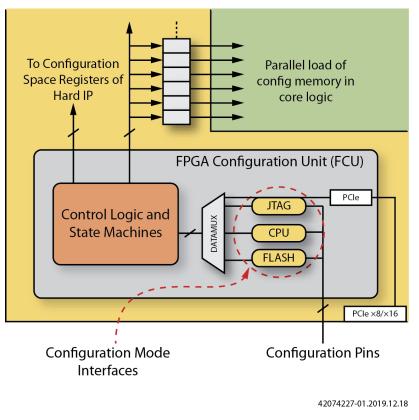

The term FPGA Configuration Unit (FCU) refers to logic that controls the configuration process of the Speedster7t FPGA. This logic is responsible for the following:

- Receiving data on a variety of core interfaces (depending on the selected programming mode)

- Decoding instructions

- Sending configuration bit values to the appropriate destination (core configuration memory, the core's boundary ring configuration memory, FCU registers, etc.)

- · Controls the startup and shutdown sequences that drive resets to the rest of the core

- CRC checks

- SEU mitigation

- Security

- Any core-level housekeeping that occurs on the de-assertion of reset (e.g., clearing of configuration memory)

Data from the configuration pins is brought into the FCU located in the core's boundary logic. Depending on the configuration mode, this data passes through one of four interfaces and is then provided to the control logic and state machines in the FCU. At this point, the data bus is standardized to a common interface (configuration mode independent). This data is processed and propagated to the configuration registers in the core's boundary ring, to the core's configuration memory, or to the hard IP blocks in the FPGA's I/O ring.

When all of the configuration bits are successfully loaded, the FCU transitions the Speedster7t FPGA into user mode, allowing the user to provide stimuli and enable operation.

Figure 1: Speedster7t Configuration Block

# Chapter - 2: Interface Performance

The table below lists the various configuration interfaces supported by the Speedster7t FPGA and their corresponding maximum operating frequency.

**Table 1: Configuration Modes and Maximum Frequencies**

| Configuration Mode | Maximum Frequency |

|--------------------|-------------------|

| JTAG               | 50 MHz            |

| CPU                | 250 MHz           |

| Serial flash       | 62.5 MHz          |

All of the programming modes and interfaces are capable of running up to 250 MHz at the configuration pins. The FCU and all associated circuitry is also capable of running up to 250 MHz. Since the internal data bus in the FCU is 128 bits wide, and in most configuration modes, the data pin count is less than 128, the incoming data stream goes through a gearbox to reduce the throughput. This configuration ensures that the internal programming circuitry runs at less than 250 MHz to process the incoming data stream. In the widest data mode (CPU ×128), the gearbox is bypassed and the entire configuration interface can run at the full 250 MHz bandwidth. Depending on the mode and configuration data width, the total bandwidth varies, and the programming time changes accordingly.

#### Note

CPUx128 is primarily for ATE use and not a recommended mode for design configuration.

# Chapter - 3: Configuration Modes for Speedster7t FPGAs

Speedster7t FPGAs support four configuration modes: Flash, JTAG, CPU and PCI Express. The selection between these modes is controlled by setting the FCU\_CONFIG\_MODESEL pins to the values shown in the table below. Both JTAG and PCIe modes are independent of the FCU\_CONFIG\_MODESEL pin setting and must be enabled by sending FCU commands that set the appropriate bits in FCU register space. The JTAG mode can be enabled by writing to the user data register of the JTAG TAP controller. The PCI Express mode is enabled by writing to the PCIe mode enable register in the FCU address space. The JTAG mode overrides all other configuration modes until disabled.

#### Note

PCIe mode is enabled by writing the PCIe mode enable register in the FCU address space, refer to Configuration via PCIe Express. The PCIE mode is set as highest priority over the other modes listed in the Table below.

#### **Table 2: Pin Settings for Various Configuration Modes**

| Configuration Mode       | Data<br>Width      | FCU_CONFIG_MODESEL [3:0] | FCU_CONFIG_SYSCLK_BYPASS <sup>(3)</sup> | FCU_CONFIG_CLKSEL <sup>(3)</sup> |  |

|--------------------------|--------------------|--------------------------|-----------------------------------------|----------------------------------|--|

| JTAG <sup>(1)</sup>      | -                  | XXXX <sup>(2)</sup>      | x                                       | 1                                |  |

| PCIe                     | -                  | xxxx                     | х                                       | 0                                |  |

|                          | 1 (SPI)            | 0001                     |                                         |                                  |  |

| Flash single device (1D) | 2 (Dual)           | 1000                     |                                         |                                  |  |

| Flash single device (TD) | 4 (Quad)           | 1010                     |                                         |                                  |  |

|                          | 8 (Octa)           | 1100                     | 0/1                                     | 0                                |  |

|                          | 1 (SPI)            | 0010                     | 0/1                                     |                                  |  |

| Flock foundations (4D)   | 2 (Dual)           | 1001                     |                                         |                                  |  |

| Flash four devices (4D)  | 4 (Quad)           | 1011                     |                                         |                                  |  |

|                          | 8 (Octa)           | 1101                     |                                         |                                  |  |

|                          | 1                  | 0011                     |                                         |                                  |  |

|                          | 8                  | 0100                     |                                         | 0                                |  |

| CPU                      | 16                 | 0101                     | 1                                       |                                  |  |

|                          | 32                 | 0110                     |                                         |                                  |  |

|                          | 128 <sup>(4)</sup> | 0111                     |                                         |                                  |  |

| Confi                                                                                                                                                                                                                                                                                                         | igurat | on Mode      | Data<br>Width   | FCU_CON       | IFIG_MODESEL [3:0]       | FCU     | _CONFIG_S    | YSCLK_BYPASS        |         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|-----------------|---------------|--------------------------|---------|--------------|---------------------|---------|

|                                                                                                                                                                                                                                                                                                               |        |              |                 |               |                          |         |              |                     |         |

| ٦                                                                                                                                                                                                                                                                                                             |        | Notes        |                 |               |                          |         |              |                     |         |

|                                                                                                                                                                                                                                                                                                               | 1.     | Always activ | e. Enabled in t | the JTAG TA   | AP controller.           |         |              |                     |         |

|                                                                                                                                                                                                                                                                                                               |        | _            | _               |               | s are set such that flas |         | •            |                     |         |

|                                                                                                                                                                                                                                                                                                               |        | override sho | uld be issued   | after flash p | rogramming has comp      | leted o | or the CPU m | ode interface is in | active. |

|                                                                                                                                                                                                                                                                                                               | 3.     | These straps | s select the co | nfiguration o | lock source.             |         |              |                     |         |

| FCU_CONFIG_SYSCLK_BYPASS Clock Selected                                                                                                                                                                                                                                                                       |        |              |                 |               |                          |         |              |                     |         |

| On-chip oscillator clock                                                                                                                                                                                                                                                                                      |        |              |                 |               |                          |         |              |                     |         |

| 1 FCU_CPU_CLK                                                                                                                                                                                                                                                                                                 |        |              |                 |               |                          |         |              |                     |         |

| <ul> <li>4. Speedster7t FPGAs have 32 dedicated data I/O pins for the CPU interface, which supports an up to ×32 interface. For ×128 mode, the upper 96 pins are shared with the DDR4 interface.</li> <li>5. CPUx128 is primarily for ATE use and not a recommended mode for design configuration.</li> </ul> |        |              |                 |               |                          |         |              |                     |         |

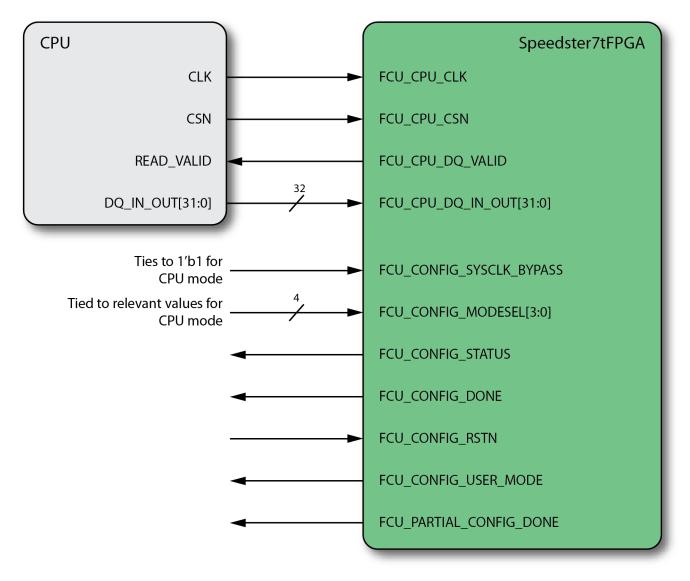

# Configuration via CPU

In CPU configuration mode, an external CPU acts as the master controlling the programming operations to the Speedster7t FPGA and offers a high-speed method for loading configuration data. Depending on the setting of the FCU\_CONFIG\_MODESEL pins, the CPU mode can be either a 1-, 8-, 16-, 32- or 128-bit wide parallel interface, clocked using FCU\_CPU\_CLK, with chip select support to indicate valid data. This mode is the fastest programming mode as it provides the widest data interface and a maximum supported clock rate of 250 MHz.

47419708-01.2019.01.04

#### Note

In the CPU master needs only to connect to the first 1, 8, 16, 32 bits of FCU\_CPU\_DQ\_IN\_OUT depending on the CPU mode selected. All unused signals should be tied to ground.

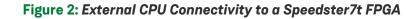

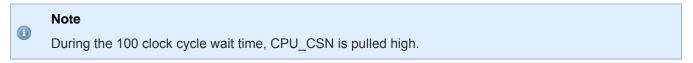

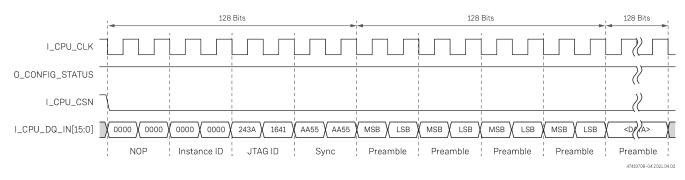

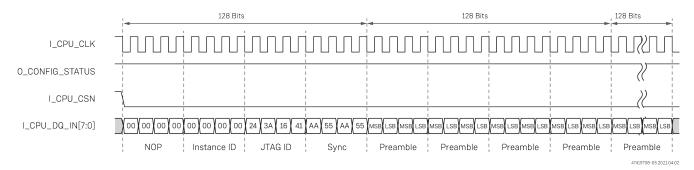

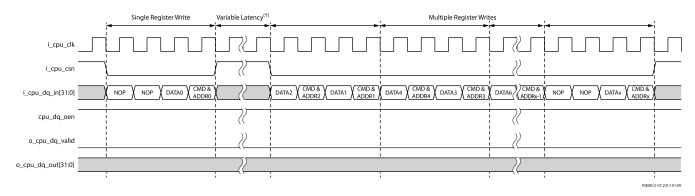

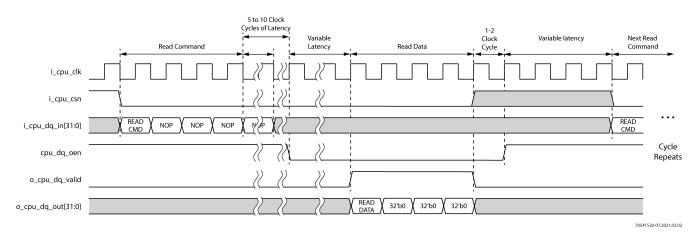

As described in the Configuration Sequence and Power-up (see page 50) section, the configuration modespecific operations occur between the release of FCU\_CONFIG\_STATUS (indicating that the configuration memory has been cleared and that the Speedster7t FPGA is ready to accept bitstream data) and the assertion of FCU\_CONFIG\_DONE (stating completion of configuration). The example waveform below for CPU×8 mode illustrates the sequence of events, clocking and control signal states needed for successful configuration in CPU mode:

- 1. After FCU\_CONFIG\_RSTN is de-asserted, FCU\_CPU\_CLK must continue to cycle to ensure that the FPGA cycles through the FCU states and the configuration memory is cleared. At that point, FCU\_CONFIG\_STATUS is driven high.

- 2. After at least 5 clock cycles of FCU\_CONFIG\_STATUS being driven high, FCU\_CPU\_CSN must be pulled low to begin writing the bitstream data into the Speedster7t FPGA. When the last set of data is written into the Speedster7t FPGA, FCU\_CPU\_CSN is pulled back high.

- 3. When FCU\_CPU\_CSN is pulled high, FCU\_CPU\_CLK needs to continue being clocked. When the FCU cycles through all of the configuration states, FCU\_CONFIG\_DONE is driven high to indicate that the Speedster7t FPGA was successfully programmed.

- 4. As the FCU\_CPU\_CLK toggles, the FCU cycles through its states to move the Speedster7t FPGA from programming mode into user mode, taking the fabric out of reset and performing operations to enable user-mode functionality for all parts of the core. The FCU\_CONFIG\_USER\_MODE signal is asserted to indicate when the Speedster7t FPGA has successfully transitioned into user mode.

At any point during the configuration, if FCU\_CPU\_CSN is asserted low, then the bus FCU\_CPU\_DQ\_IN\_OUT should have valid data or NOPs, if FCU\_CPU\_CSN is high, the data on FCU\_CPU\_DQ\_IN\_OUT is ignored. When the bitstream is programmed, FCU\_CPU\_CSN can be held low while sending NOPs to the Speedster7t FPGA. This action will not affect the assertion of FCU\_CONFIG\_DONE or FCU\_CONFIG\_USER\_MODE signals.

Figure 3: Clocking and Control Signals for Successful Configuration

### Programming Data Ordering

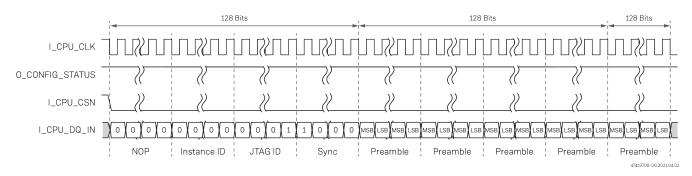

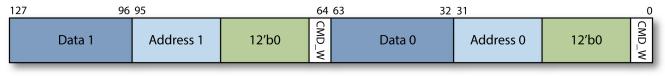

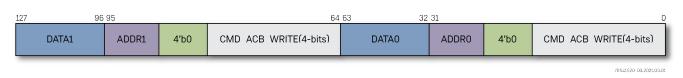

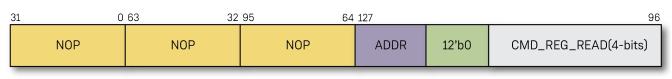

In Speedster7t FPGAs, the configuration memory data bus is 128 bits wide, but the command and FCU register buses are 32 bits wide. Data transmission occurs MSB to LSB at both the byte and 32-bit packet levels. Commands are executed 32 bits at a time, but the data register is 128 bits wide and requires that four sets of 32-bit packets be transmitted. At the 128-bit full payload level, the data transmission needs to occur in the following order: i3, i2, i1, i0, where ix is a 32-bit packet. The sequence of instructions is i0, i1, i2 and then i3.

This structure makes the bitstream programming implementation very uniform for CPU×1, CPU×8, CPU×16 and CPU×32 modes. The various potential data orders are illustrated in the example waveforms below, each showing the transmission of the same bitstream contents in the five different CPU widths.

#### Note

The figures in this section are to show methodologies and generalized scenarios. For detailed waveforms for specific commands, refer to the respective section in FCU Command List. Also, the JTAG ID values in the waveforms below are indicative and not specific to a device.

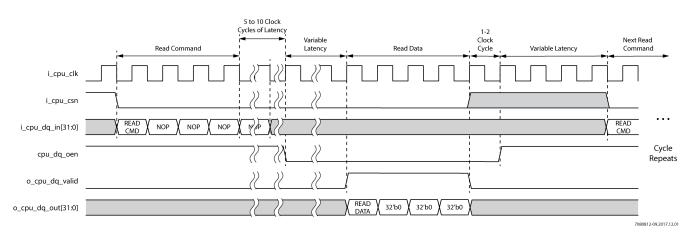

### CPU×32

As shown in the waveform below, a command is issued on each clock cycle in CPUx32 mode:

- The first 128-bit payload shows that the order of loading is NOP, Instance ID, JTAG ID and then Sync, with each 32-bit packet transmitted MSB to LSB. However, as indicated above, the sequence in which these are processed by the FCU are Sync, JTAG ID, Instance ID and finally NOP.

- The second 128-bit payload operates the same way where the 32 bit preamble data is transmitted first, followed by the next three preamble data, but the execution occurring in the reverse order with the 1st preamble data being executed last. Also, when a write or read command is issued, it needs to be the last 32-bit FCU command in the 128-bit sequence. This requirement is because the FCU expects data input or provides data output immediately following the write and read operations respectively.

- When the write command has been issued for a particular frame, subsequent clocks have CMEM frame data transmitted on every clock, again in 128-bit payload sets.

The signal FCU\_CPU\_CSN must be held low during the entire time when FCU commands are being issued for write operations. If FCU\_CPU\_CSN is asserted during the (128/CPU\_data\_width) continuous clock cycles of one request, that request is discarded. When the FCU\_CPU\_CSN signal returns low, the next request is handled normally.

Figure 5: Bitstream Programming in CPU×32 Mode

### CPU×16

CPU×16 mode is very similar to CPU×32 mode. The only difference is that 16-bits of data are transmitted on each FCU clock cycle, i.e., each FCU command is transmitted over two FCU clock cycles, MSB to LSB (as shown in the waveform below).

Figure 6: Bitstream Programming in CPU×16 Mode

### CPU×8

CPU×8 mode follows along the lines of CPU×16 and CPU×32 modes, with each FCU command requiring four FCU clock cycles for transmission, MSB to LSB, as detailed in the waveform below.

### Figure 7: Bitstream Programming in CPU×8 Mode

### CPU×1

In CPU×1 mode, a single bit of the FCU command (or write data) is transmitted on each FCU clock cycle, MSB to LSB, for a 32-bit packet, but in reverse order for the 128-bit payload as described in the other CPU width modes. The waveform below shows these details.

### Note

Contact Achronix Support for more details on the CPU x128 mode.

| CPUx32 ACE Programming File Example                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preamble 512 bit:                                                                                                                                    |

| NOP                                                                                                                                                  |

| Instance ID<br>JTAG ID                                                                                                                               |

| Sync                                                                                                                                                 |

| 32-bit length preamble to indicate number of 128 bit blocks of unencrypted bitstream                                                                 |

| 64 bit preamble Information only valid for encrypted bitstream<br>32-bit length preamble to indicate number of 128 bit blocks of encrypted bitstream |

| 256 bits of zeros that are reserved                                                                                                                  |

| <br>NOP                                                                                                                                              |

| Write Cmd                                                                                                                                            |

| NOP                                                                                                                                                  |

| NOP                                                                                                                                                  |

| NOP                                                                                                                                                  |

| Write Data                                                                                                                                           |

|                                                                                                                                                      |

### **Configuration via Flash Memories**

### Caution!

Speedster7t FPGAs can interface to serial NOR flash devices only. Parallel NOR, NAND or other flash variants are *not* supported.

Flash programming mode allows flash memories to be used to configure Speedster7t FPGAs. In this mode, the FPGA is the master and supplies the clock to the flash memory.

The clock supplied from the FPGA (on the FCU\_FLASH\_SCK pin) to the attached flash device(s) can be driven by the FCU\_CPU\_CLK or the on-chip oscillator clock depending on the configuration options selected as described in the Configuration Modes for Speedster7t FPGAs (see page 9) chapter. The frequency of this clock can be selected from one of four variants of the clock sources arriving at the FCU: the original (divide-by-1), divide-by-2, divide-by-4 or divide-by-8. This selection is configured using the 'Serial Flash Clock Divider' drop-down menu in the 'Bitstream Generation Implementation Options' section of the ACE GUI. This setting ensures that only the flash state machine runs at the slower frequency. All other FCU and ACB circuitry continues to operate at the original input clock frequency.

#### Note

At power-on, the device defaults to the divide-by-8 setting. The FCU then sets the appropriate configuration register to control the clock divider based on the user selection in ACE. The transition from a divide-by-8 clock to any other selected clock frequency is glitch free. Also, flash write is always SPI only while read can be in SPI, DUAL, QUAD or OCTA mode as summarized in the table below.

### Flash Interface

The configuration block is equipped with a flash interface that supports flash programming and readback. A bitstream can be programmed into flash through JTAG or the PCIe interface. Flash registers (refer to Registers and Addressing (see page 26)) within the configuration block assist with this process. The complete feature list of the flash interface is as described in the table below.

#### Table 3: Flash Features

| Feature               | Description                                                                                                                   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Programming interface | SPI – JTAG, PCIe (Remote update programming via FPGA).                                                                        |

| Security mode         | Double encryption.                                                                                                            |

| Device mode           | X1, X4.                                                                                                                       |

| I/O Mode              | SPI, DUAL, QUAD, OCTA.                                                                                                        |

| Flash write           | SPI.                                                                                                                          |

| Flash Read            | SPI, DUAL, QUAD, OCTA.                                                                                                        |

| Header                | Holds fallback, current address and read commands.                                                                            |

| Two image<br>support  | Flash can store two images, golden and new image.                                                                             |

| Remote update         | Flash can be stored with new or updated images remotely.                                                                      |

| Error fallback        | If a CRC error occurs in the updated bitstream, the flash interface uses the fallback address specified in the page-0 header. |

### Flash Device Configurations

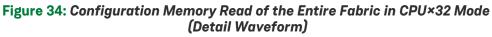

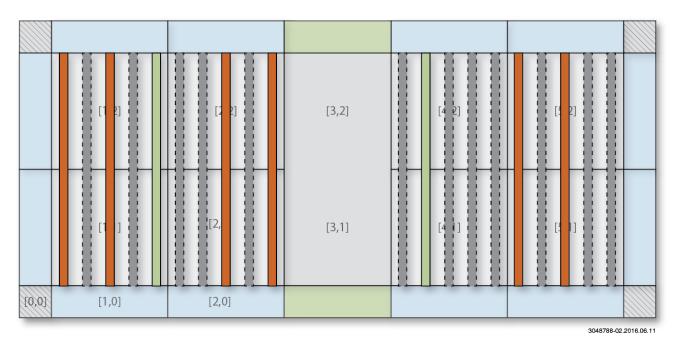

Speedster7t FPGAs support two flash device configurations, single flash device (1D) and four flash devices (4D).

### **1D Configuration**

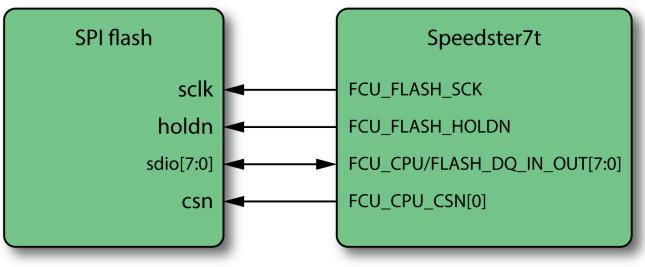

The 1D programming configuration is composed of a Speedster7t FPGA acting as the master and communicating with a single flash device. The  $o_flash_sck$  signal is used for clocking. The  $o_flash_sdi$  signal is the data output from the FPGA to communicate instructions to the flash device and  $i_flash_sdo[0]$  is the single-bit FPGA input pin which receives the bitstream from the flash in ×1 mode. The  $o_flash_csn[0]$  signal is pulled low as soon as communication between the FPGA and flash device begins, and stays low during the valid bitstream window.

The FPGA can communicate with the flash device in SPI, Dual, Quad or Octa modes in 1D configuration.

The figure below provides a block diagram of how a serial flash device can be connected to a Speedster7t FPGA in Octa (x8) mode.

47419712-01.2021.02.13

Figure 9: Speedster7t FPGA 1D Flash Programming Configuration

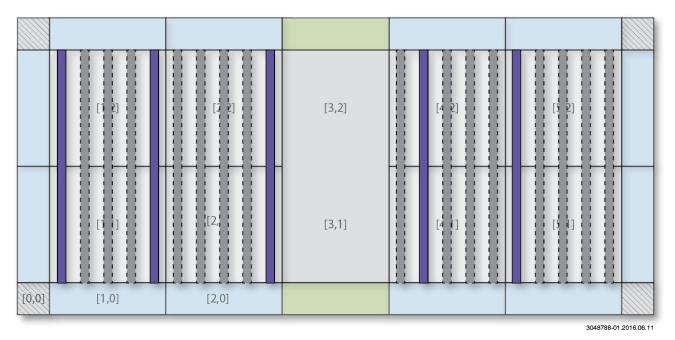

### **4D Configuration**

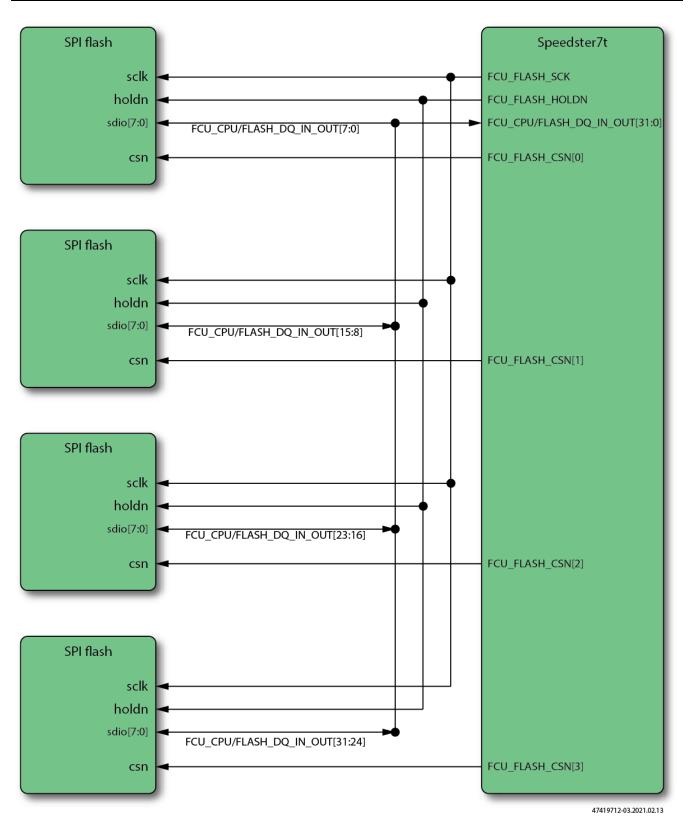

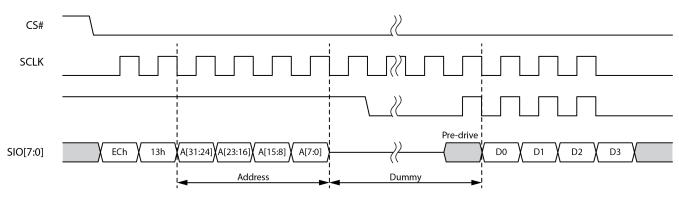

Serial 4D flash programming mode is essentially an enhanced and higher bandwidth implementation of the serial flash 1D configuration. The FPGA is again the master, and interfaces with not one but four flash memory devices to increase the data bandwidth four times.

When writing to the four flash memories, all four chip selects  $o_flash_csn[3:0]$  are pulled low simultaneously and 1-bit of bitsream data is sent to each flash device in SPI mode. When reading from the four flash memories, the FPGA pulls all of the  $o_flash_csn[3:0]$  signals low. Four-wide configuration data is read from the flash memories and transferred to the FPGA through the  $i_flash_sdo$  ports. When bitstream operations are complete (flash memory contents are read), transitioning from the end of the bitstream to user mode is performed as in CPU and flash 1D modes.

Each flash device can operate in SPI, Dual, Quad or Octa modes. The figure below provides a block diagram of how four serial flash devices (4D configuration) can be connected to a Speedster7t FPGA in Octa (x8) mode.

Figure 11: Speedster7t FPGA 4D Flash Programming Configuration

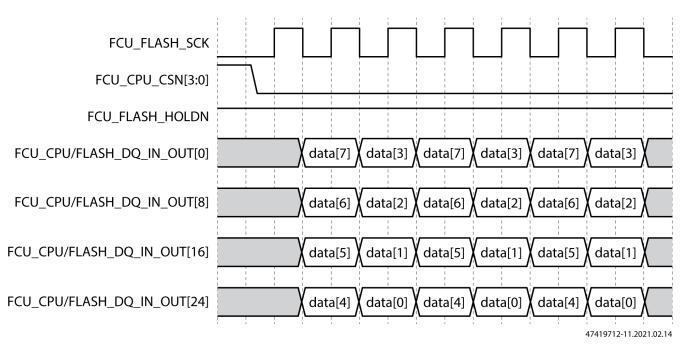

Figure 12: 4D Flash SPI Read Data Ordering

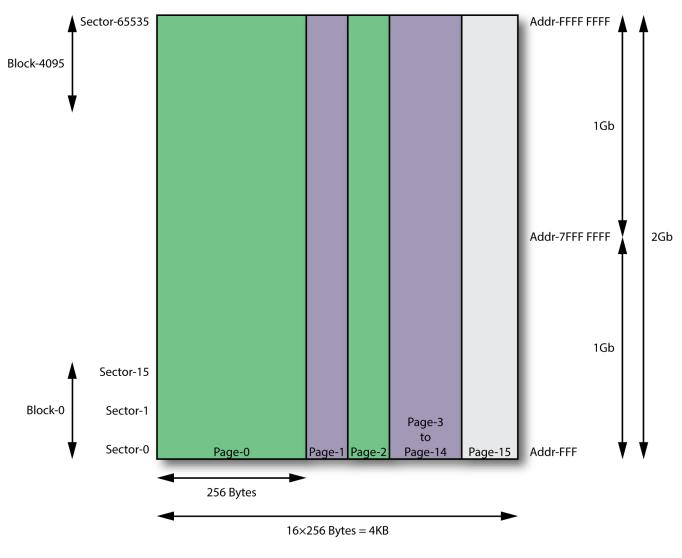

### Addressing Modes and Memory Organization

Addressing modes for flash memory are based on the size of the device. A three-byte addressing mode is required for 128 Mb flash and smaller, and a four-byte addressing mode is required to support memory sizes above 128 Mb. Writes to the flash memory occur as pages, with each page consisting of 256 bytes. The figure below shows the memory organization:

47419712-12.2021.03.24

### Address Range

The following table shows the address ranges when two images are stored on a single flash device, assuming that each image is 1Gb in size.

#### Table 4: Address Ranges for Two Bitstream Images on a Single Device

| Address<br>Range (32<br>bits)    | Description                                                                                                                                                                                 | Configuration Details                      |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 0x0000_0000<br>to<br>0x0000_00FF | Page-0 address space. This range contains<br>header information described in the flash<br>configuration header section. This address range<br>cannot be used for storing actual bitstreams. | These addresses are not user configurable. |

| Address<br>Range (32<br>bits)    | Description                 | Configuration Details                                                                                                                                                   |

|----------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000_1000<br>to<br>0x07FF_FFFF | FPGA image 1 address space. | The start address can be configured via the current/fallback address in the page-0 header. This example assumes the address starts at 0x0000_1000 for a 1 Gb bitstream. |

| 0x0800_0000<br>to<br>0x0FFF_FFF  | FPGA image 2 address space. | The start address can be configured via the current/fallback address in the page-0 header. This example assumes the bitstream starts at address 0x0800_0000.            |

### Flash Configuration Header (Page-0 Header)

The first 256 bytes in the flash memory (page 0) store control information that describe how the subsequent bitstream should be read from the flash device. This information can be written to the flash device in two ways:

- Via the JTAG interface along with the bitstream.

- Pre-programmed into the device by the manufacturer.

This space is not used for storing the device bitstream.

#### Table 5: Page-0 Header Format

| Address      | Bits | Value                                      | Description                                                                                                                                                                                                                                                                     |

|--------------|------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0xC to 0xF   | 32   | Read command.                              |                                                                                                                                                                                                                                                                                 |

| 0x8 to 0xB   | 32   | Flash configuration header read count.     |                                                                                                                                                                                                                                                                                 |

| 0x4 to 0x7   | 32   | Bitstream read control.                    | bit 0 – Flash read enable.<br>bit 1 – Flash fall back enable.<br>bit [5:2] – Retry count.<br>bit [21:6] – Timeout count.<br>bit 22 – Enable 4-byte addressing.<br>bit [27:23] – Dummy read cycles.<br>bit [31:28] – Flash SCK div count.<br>bit 32 - 1'b1 Micron, 1'b0 Macronix |

| 0x0 to 0x3   | 32   | Bitstream read address (new image).        |                                                                                                                                                                                                                                                                                 |

| 0x14 to 0x17 | 32   | Bitstream fallback address (golden image). |                                                                                                                                                                                                                                                                                 |

| 0x10 to 0x13 | 32   | Fallback read command.                     |                                                                                                                                                                                                                                                                                 |

| 0x18 to 0x20 | 24   | Reserved.                                  |                                                                                                                                                                                                                                                                                 |

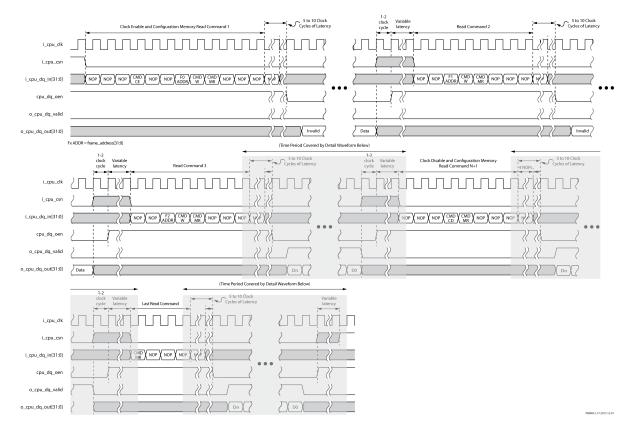

### Flash Configuration Protocol

With the FCU\_CONFIG\_MODESEL[3:0], FCU\_CONFIG\_CLKSEL and FCU\_CONFIG\_SYSCLK\_BYPASS straps set for serial flash programming, operations begin as soon as the FPGA is powered up and the FCU receives the clock input. Immediately after reset is released, bitstream data is read out from the flash device through the flash interface (at this time the default is SPI (×1) mode). The bitstream read is performed in two stages as described below:

Stage 1 – Flash configuration header read from flash device:

- The FCU sends a default read command and address of 0x0000\_0000 (32 bits) in SPI mode to the flash device and reads the flash configuration header.

- Internal registers are then updated, including the start address for the bitstream and flash read command.

Stage 2 – Bitstream read from flash device:

- Based on the read mode (×1/×2/×4/×8) obtained from the flash configuration header, the command and start address are sent to the flash device.

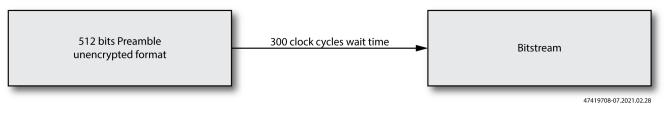

- The FCU reads the first 512 bits of bitstream data from the flash device and enters a wait state.

- If encryption is not enabled, the FCU reads the complete bitstream and configures the FPGA. If encryption is enabled and the efuse key is ready, the FCU reads the header segment0 data and sends it to the secure boot core. The flash read state machine then waits for 2.6 ms after which the FCU reads the complete bitstream and configures the FPGA.

Bitstream programming in all configuration modes is MSB to LSB. For transmitting a 32-bit FCU command, the ordering in the serial ×1 mode for 1D and 4D configuration is as follows:

- 1D flash configuration The flash device transmits command bit 31 on the first clock and bits 30, 29, 28, etc. on subsequent clocks all the way down to bit 0 on the 32<sup>nd</sup> (last) clock.

- 4D flash configuration The four flash devices transmit command bits [31:28] on the first clock, all the way down to bits [3:0] on the eighth (last) clock. The ordering within the 4-bit nibble corresponds to the flash device ordering. Specifically, on the first clock, flash[3] transmits bit 31, flash[2] transmits bit 30, flash[1] transmits bit 29 and flash[0] transmits bit 28

### Flash Modes

The following section describes the various modes supported for read and write operations to/from an attached flash device. Read operations from the flash device can be configured either as SPI, Quad or Octa modes for both 1D and 4D configurations while write operations to the flash device always occur in SPI mode.

#### Note

A flash write can be performed via either the JTAG or PCIe modes. The PCIe or JTAG port can access the data and command registers using an indirect addressing mode.

The following table describes the different combinations of the flash device configurations and modes supported in the Speedster7t FPGA.

| Flash Programming Mode<br>/Configuration | Flash<br>Interface<br>width | No. of Flash<br>Devices | Write Width<br>SO[0] Pin × No. of<br>Flash Devices | Read Width<br>SO[n:0] × No. of<br>Flash Devices |

|------------------------------------------|-----------------------------|-------------------------|----------------------------------------------------|-------------------------------------------------|

| SPI ×1 (1D)                              | 1                           | 1                       | 1                                                  | 1                                               |

| SPI ×1 (4D)                              | 1                           | 4                       | 4                                                  | 4                                               |

| Quad ×4(1D)                              | 4                           | 1                       | 1                                                  | 4                                               |

| Quad ×4 (4D)                             | 4                           | 4                       | 4                                                  | 16                                              |

| Octa ×8 (1D)                             | 8                           | 1                       | 1                                                  | 8                                               |

| Octa ×8 (4D)                             | 8                           | 4                       | 4                                                  | 32                                              |

Table 6: Flash Device Configurations and Modes

Read operation timing diagrams for each of the modes are described below:

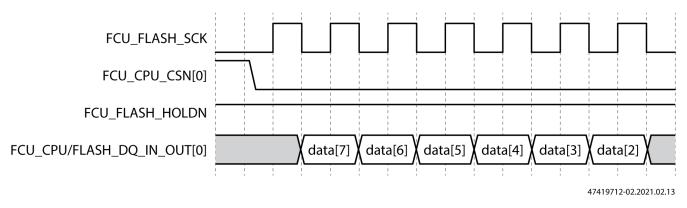

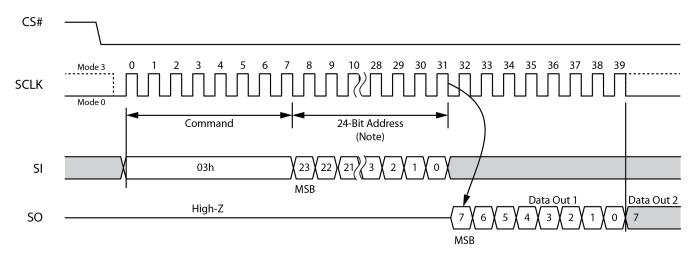

### SPI Mode (x1)- 1D flash

47419712-04.2019.12.18

Speedster7t Configuration User Guide (UG094)

Figure 15: SPI Mode (×1) Write

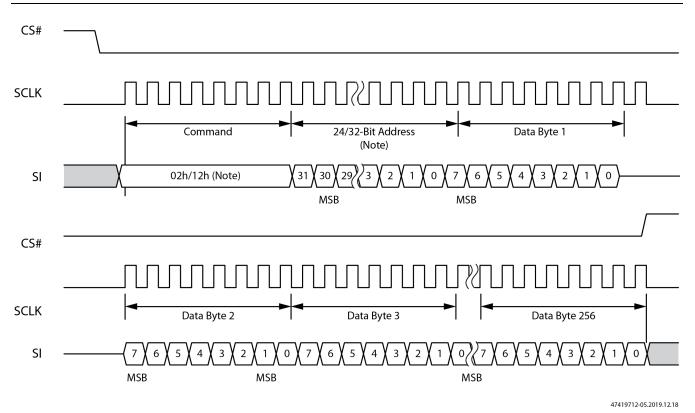

### Quad Mode (x4)- 1D flash

#### Reads

47419712-07.2019.12.18

Figure 16: Quad Read Mode (QREAD)

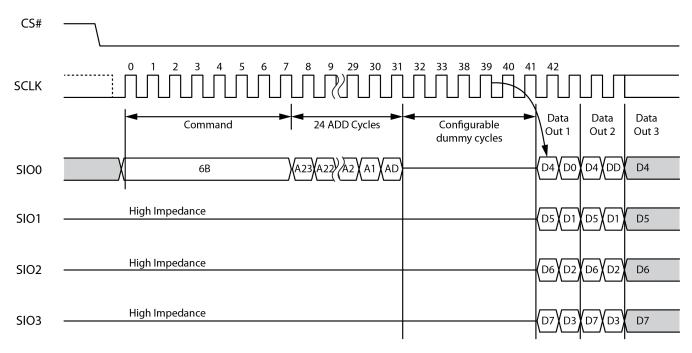

Octa Mode (x8)- 1D flash

47419712-10.2019.12.18

Figure 17: OCTA Read Mode (8READ)

### **Registers and Addressing**

### Table 7: Flash Controller Register Map

| Register Name                             | Address | Description                            |

|-------------------------------------------|---------|----------------------------------------|

| Flash write control register              | 0x1038  | Flash write control register.          |

| Flash write count                         | 0x1048  | Flash write count register.            |

| Flash write configuration register        | 0x1050  | Flash configuration register.          |

| Flash write status                        | 0x1060  | Flash status register.                 |

| Flash write data1                         | 0x1040  | Flash write data register.             |

| Flash write data2                         | 0x11d4  | Flash write data register.             |

| Flash write data3                         | 0x11d8  | Flash write data register.             |

| Flash write data4                         | 0x1044  | Flash write data register.             |

| Flash bitstream current address           | 0x12bc  | Flash bitstream read current address.  |

| Flash fallback bitstream fallback address | 0x12b8  | Flash bitstream read fallback address. |

| Flash write command 1                     | 0x103c  | Flash command register.                |

| Flash write command 2                     | 0x104c  | Flash command register.                |

| Flash write command 3                     | 0x1054  | Flash command register.                |

| Flash write command 4                     | 0x1058  | Flash command register.                |

### Table 8: Flash Write Control Register

| Register Field                 | Bit<br>Position | Туре | Reset<br>value | Description                                                                               |

|--------------------------------|-----------------|------|----------------|-------------------------------------------------------------------------------------------|

| Flash write enable             | 0               | RW   | 0x0            | Initiate the flash write operation.                                                       |

| Flash write clock<br>div count | 4:1             | RW   | 0x1            | Clock divider. Set to 4'b0001 default, divide by 2 clock which is required for JTAG mode. |

| Flash write Stop               | 5               | RW   | 0x0            | Suspend the current operation.                                                            |

| Flash write wait               | 6               | RW   | 0x0            | Flash wait operation.                                                                     |

| Flash write ×1<br>mode         | 7               | RW   | 0x0            | Flash write in SPI ×1 device mode.                                                        |

| Register Field         | Bit<br>Position | Туре | Reset<br>value | Description                        |

|------------------------|-----------------|------|----------------|------------------------------------|

| Flash write ×4<br>mode | 8               | RW   | 0x0            | Flash write in SPI ×4 device mode. |

| Reserved               | 31:9            | RW   | 0x0            | Reserved.                          |

### Table 9: Flash Write Count

| Register Field    | Bit Position | Туре | Reset Value | Description                                        |

|-------------------|--------------|------|-------------|----------------------------------------------------|

| Flash write count | 31:0         | RW   | 'h0000_0000 | Number of 128-bit blocks of data written to flash. |

### Table 10: Flash Write Data 1

| Register Field     | Bit Position | Type Reset Valu |             | Description          |

|--------------------|--------------|-----------------|-------------|----------------------|

| Flash write data 1 | 31:0         | RW              | 'h0000_0000 | Write data to flash. |

#### Table 11: Flash Write Data 2

| Register Field          | Bit Position | Туре | Reset Value | Description          |

|-------------------------|--------------|------|-------------|----------------------|

| Flash write data 2 31:0 |              | RW   | 'h0000_0000 | Write data to flash. |

### Table 12: Flash Write Data 3

| Register Field     | Bit Position | Туре | Reset Value | Description          |

|--------------------|--------------|------|-------------|----------------------|

| Flash write data 3 | 31:0         | RW   | 'h0000_0000 | Write data to flash. |

### Table 13: Flash Write Data 4

| Register Field     | Bit Position | Туре | Reset Value | Description          |

|--------------------|--------------|------|-------------|----------------------|

| Flash write data 4 | 31:0         | RW   | 'h0000_0000 | Write data to flash. |

### Table 14: Flash Write Configuration Register

| Register<br>Field            | Bit<br>Position | Туре                         | Reset<br>Value | Description                                                                                                                                                                                     |

|------------------------------|-----------------|------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash<br>write data<br>valid | 0               | RW<br>[Write<br>on<br>clear] | 0x0            | Write data valid, Indicates to the flash interface when data is written to the flash write register. Cleared when the flash interface reads the data and writes it into the internal registers. |

| Register<br>Field                  | Bit<br>Position | Туре | Reset<br>Value | Description                                                                                                                |

|------------------------------------|-----------------|------|----------------|----------------------------------------------------------------------------------------------------------------------------|

| Flash<br>write<br>command<br>valid | 1               | RW   | 0x0            | Flash write command valid, Indicates to the flash interface when the write command is written to the flash write register. |

| Flash<br>write<br>command<br>count | 8:2             | RW   | 0x8            | Write command count in number of bits.                                                                                     |

| Flash<br>write data<br>count       | 15:9            | RW   | 0x127          | Write data count in number of bits.                                                                                        |

| Flash<br>write data<br>request     | 16              | R    | 0x1            | Request write data, PCIe, should poll these bits, cleared when data is shifted to internal registers.                      |

### Table 15: Flash Write Status

| Register Field             | Bit Pposition | Туре | Reset Value | Description                                   |

|----------------------------|---------------|------|-------------|-----------------------------------------------|

| Flash state machine status | [4:0]         | RO   | 0x0         | Write state machine status.                   |

| Flash read done            | 5             | RO   | 0x0         | Flash read is complete.                       |

| Flash write done           | 6             | RO   | 0x0         | Flash write is complete.                      |

| Flash read error           | 7             | RO   | 0x0         | Flash read error, CRC error.                  |

| Flash write error          | 8             | RO   | 0x0         | Flash write error, flags flash device status. |

| Reserved                   | 31:9          | RO   | 0x0         | Reserved.                                     |

# Configuration via JTAG

The Speedster7t FPGA JTAG TAP controller is compliant to IEEE Std 1149.1 and is used for programming the bitstream and debug via Snapshot in ACE. The JTAG\_TMS and JTAG\_TCK inputs determine whether an instruction register scan or data register scan is performed. JTAG\_TMS and JTAG\_TDI are sampled on the rising edge of JTAG\_TCK, while JTAG\_TDO changes on the falling edge. JTAG configuration and operation mode is independent of FCU\_CONFIG\_MODESEL settings.

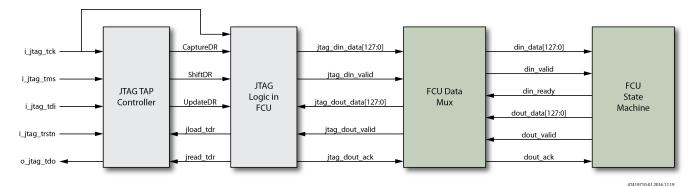

JTAG implementation in Speedster7t FPGAs, which allows for bitstream programming as well as real-time insystem control and observation, is composed of the blocks shown in the figure (see page 29) below.

The external interface is a standard 5-pin JTAG interface, connected directly to the JTAG TAP controller. The TAP controller operates independently from the Speedster7t FPGA FCU. It is always active and uses JTAG\_TCK

for clocking. The TAP controller takes the data from the pins and converts it to DR instructions to communicate to the JTAG logic in the FCU. It also takes in data in the form of load/read requests, translating it to the appropriate signals to drive and expect on the JTAG pins.

The JTAG logic in the FCU interprets these DR instructions and generates input data in the standard 128-bit Speedster7t FPGA frame size format, along with a data valid indicator, to be forwarded to the FCU data mux and, ultimately, to the FCU state machine for configuration memory loading. The FCU data mux takes in 128-bit output data from the FCU, which also comes with a valid signal for debug and read-back operations. The mux also provides an acknowledge signal to indicate to downstream circuitry that the data transfer was successful.

The FCU data mux simply selects between the configuration mode specific data buses coming in to the FCU. This logic is controlled by the static FCU\_CONFIG\_MODESEL straps and the JTAG override circuitry from the JTAG TAP controller.

Finally, the FCU state machine takes incoming data and uses it for loading the configuration memory. Conversely, it also provides output data from the configuration memory or Snapshot to be forwarded upstream.

Figure 18: Block Diagram for JTAG Instruction Processing in FCU

The JTAG programming sequence is highlighted in the following waveform (see page 30) to show the sequence of internal procedures that occur in the ACE generated jam file. An explanation of these steps follows:

- 1. DO\_RESET\_CHIP In this step, an internal signal generates a pulse on the FCU reset circuitry to reset it, similar to providing a pulse on the FCU\_CONFIG\_RSTN input pin.

- 2. DO\_ENTER\_JTAG This step provides a TAP command (override) to place the Speedster7t FPGA FCU in JTAG mode. After this step, regardless of the FCU\_CONFIG\_MODESEL settings, the FCU configuration mode (and the data muxes) are set to listen to the JTAG inputs, and the FCU clock is sourced from JTAG\_TCK.

- 3. DO\_ERASE This step cycles through the FCU states to ensure that the configuration memory is cleared. After this step, FCU\_CONFIG\_STATUS is asserted.

- DO\_PROGRAM In this step, the actual bitstream loading occurs. This operation consists of DRSCAN loops for every bit in the bitstream. Since the size of the bitstream is pre-determined, the loop count is set appropriately by ACE.

- 5. DO\_ENTER\_USER\_MODE In this step, IRSCAN and DRSCAN commands are provided to cycle through additional FCU states. Idle clocks are provided to ensure that the start-up state machine completes successfully and, in the process, o\_config\_done and FCU\_CONFIG\_USER\_MODE are asserted. After this step, functions hosted within a Speedster7t FPGA are active.

- 6. DO\_EXIT\_JTAG This step provides another TAP command, performed in parallel at the start of usermode operations, to quickly provide additional instructions to remove the JTAG override on the FCU.

| i_jtag_tck         |               |               |          |            |                    |                        |

|--------------------|---------------|---------------|----------|------------|--------------------|------------------------|

| i_jtag_tms         | DO_RESET_CHIP | DO_ENTER_JTAG | DO_ERASE |            | DO_ENTER_USER_MODE | DO_EXIT_JTAG           |

| i_jtag_trstn       | DO_RESET_CHIP | DO_ENTER_JTAG | DO_ERASE |            | DO_ENTER_USER_MODE | DO_EXIT_JTAG           |

| i_jtag_tdi         | DO_RESET_CHIP | DO_ENTER_JTAG | DO_ERASE | DO_PROGRAM | DO_ENTER_USER_MODE | DO_EXIT_JTAG           |

| o_jtag_tdo         | DO_RESET_CHIP | DO_ENTER_JTAG | DO_ERASE | DO_PROGRAM | DO_ENTER_USER_MODE | DO_EXIT_JTAG           |

| o_config_status    |               |               |          |            |                    |                        |

| o_config_done      |               |               |          |            |                    |                        |

| o_config_user_mode |               |               |          | /          |                    |                        |

|                    |               |               |          |            |                    | 47419710-02.2016.12.19 |

### Figure 19: JTAG Bitstream Programming Sequence

### JTAG Instructions

The table below lists all JTAG instructions supported by Speedster7t FPGAs.

#### Table 16: JTAG Instructions

| Instruction  | Opcode                                   | DR<br>Width | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BYPASS       | 23'b000000000000000000000000000000000000 | 1           | The required BYPASS instruction allows a Speedster7t FPGA to remain in a functional mode and selects the bypass register to be connected between JTAG_TDI and JTAG_TDO. The BYPASS instruction allows serial data to be transferred through the FCU from JTAG_TDI to JTAG_TDO without affecting the operation of the Speedster7t FPGA.                                                                                                                                                                                                                                                                                             |

| EXTEST       | 23'b11111111111111111101000              | _           | The required EXTEST instruction places the<br>Speedster7t FPGA into an external boundary-test<br>mode and selects the boundary-scan register to be<br>connected between JTAG_TDI and JTAG_TDO.<br>Output pins operate in test mode, driven from the<br>contents of the boundary-scan update latch. Input<br>data are captured in boundary-scan latches prior to<br>shift operation. During this instruction, the<br>boundary-scan register is accessed to drive test<br>data outside of the Speedster7t FPGA via the<br>boundary outputs and receive test data from<br>outside of the Speedster7t FPGA via the boundary<br>inputs. |

| EXTEST_PULSE | 23'b11111111111111111101001              | _           | The EXTEST_PULSE instruction generates a single pulse by entering and exiting the Run-Test /Idle state of the 1149.1 TAP controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Instruction        | Opcode                                   | DR<br>Width | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST_TRAIN       | 23'b11111111111111111101010              | _           | EXTEST_TRAIN generates a stream of pulses<br>while in the Run-Test/Idle state. A BSDL file for an<br>1149.6 device specifies the minimum number of<br>pulses and the maximum time period allowed for<br>pulse generation in the Run-Test/Idle state.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SAMPLE<br>/PRELOAD | 23'b1111111111111111111000               | _           | The required SAMPLE/PRELOAD instruction allows<br>a Speedster7t FPGA to remain in its functional<br>mode and selects the boundary-scan register to be<br>connected between JTAG_TDI and JTAG_TDO.<br>The output and input pins operate in normal mode.<br>Input pin data and core logic output data are<br>captured in the boundary-scan latches. During this<br>instruction, the boundary-scan register can be<br>accessed via a data scan operation to take a<br>sample of the functional data entering and leaving<br>the Speedster7t FPGA. This instruction is also used<br>to preload test data into the boundary-scan register<br>before loading an EXTEST instruction. |

| IDCODE             | 23'b11111111111111111111111              | 32          | The optional IDCODE instruction allows a<br>Speedster7t FPGA to remain in its functional mode<br>and selects the optional device identification<br>register to be connected between JTAG_TDI and<br>JTAG_TDO. The IDCODE register appears between<br>JTAG_TDI and JTAG_TDO after power-up, after the<br>TAP has been reset using the optional TRST pin, or<br>by otherwise moving to the Test-Logic-Reset state.                                                                                                                                                                                                                                                              |

| HIGHZ              | 23'b11111111111111111001111              | -           | The optional HIGHZ instruction sets all outputs (including two-state as well as three-state types) to a disabled (high-impedance) state and selects the bypass register to be connected between JTAG_TDI and JTAG_TDO.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CLAMP              | 23'b111111111111111111111111111111111111 | _           | The CLAMP instruction provides for "guarding" chip<br>outputs during in-circuit test or boundary-scan<br>functional test. Output pins operate in test mode,<br>driven from the content of the boundary-scan<br>update latch. The one-bit bypass register is<br>selected for shifting.                                                                                                                                                                                                                                                                                                                                                                                         |

| INTDR              | 23'b00000000000000000111101              | 97          | This instruction provides access to the test data register that is implemented internal to the TAP controller. This internal register is used for global configuration and monitoring of global status signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Instruction                                                                                                                     | Instruction Opcode          |                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| JLOAD                                                                                                                           | 23'b00000100000001100111010 | 128             | The JLOAD instruction enables the scan in of the configuration bitstream to the configuration logic (in this mode, the SHIFT-DR state is used to scan in the bitstream). For the read-back, the data register is read back. All of these operations are performed internally using a 128-bit parallel bus. Data is latched every 128 bits in the UPDATE-DR state.                                                        |  |

| JREAD                                                                                                                           | 23'b0000010000001000111010  | 128             | The JREAD instruction enables the data register for<br>read-back. When this instruction is decoded and<br>CAPTURE-DR is executed, the data from the<br>configuration logic is sampled as 32-bit data plus a<br>valid bit. Multiple words of the configuration memory<br>can be read back by cycling through the CAPTURE-<br>DR/SHIFT-DR states. The 33-bit status register is<br>selected between JTAG_TDI and JTAG_TDO. |  |

| JUSR1                                                                                                                           | 23'b00000100000000100111010 | User<br>defined | The JUSR1 instruction enables the USER1 TDR. <sup>(†)</sup>                                                                                                                                                                                                                                                                                                                                                              |  |

| JUSR2                                                                                                                           | 23'b00000100000000000111010 | User<br>defined | The JUSR2 instruction enables the USER2 TDR. <sup>(†)</sup>                                                                                                                                                                                                                                                                                                                                                              |  |

| JASYNCERR                                                                                                                       | 23'b0000000000001110111010  | _               | The JSYNCERR instruction enables the connection to the fabric error status scan register.                                                                                                                                                                                                                                                                                                                                |  |

| Table No                                                                                                                        | ote                         |                 |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| <sup>(I)</sup> <sup>†</sup> This TDR is implemented in the fabric and is used for supporting debug functionality in the fabric. |                             |                 |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

# Chapter - 4: Configuration Pin Tables

### Table 17: Interface Pin Table

| Pin Name                         | Direction            | Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |  |

|----------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|

| Configuration Interface          |                      | ^                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |  |

|                                  |                      | FPGA configuration unit (FCU) configuration mode selection inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |  |

|                                  |                      | Configuration Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CFG_MODESEL[3:0]   |  |

|                                  |                      | CPU x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0011               |  |

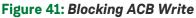

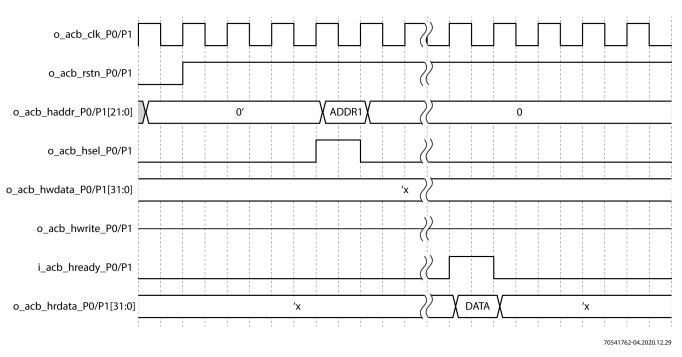

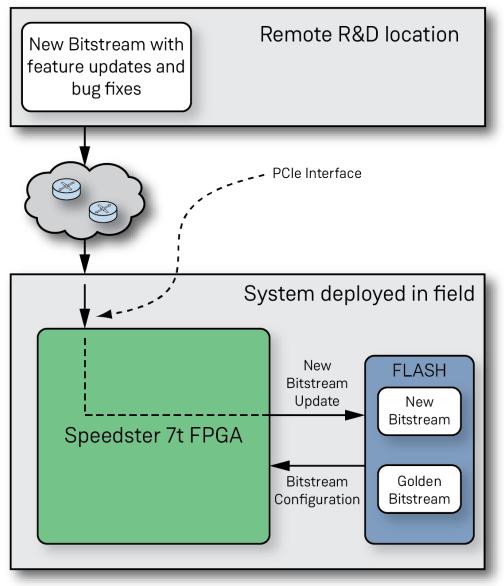

|                                  |                      | CPU x8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0100               |  |