## Speedster22i<sup>™</sup> FPGA Family Power Estimator Tool User Guide

UG054- July 28, 2015

Copyright © 2015 Achronix Semiconductor Corporation. All rights reserved. Achronix is a trademark and Speedster is a registered trademark of Achronix Semiconductor Corporation. All other trademarks are the property of their prospective owners. All specifications are subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, and disclaimers are listed at <u>http://www.achronix.com</u> and use of this document and the Information contained therein is subject to such terms

## **Table of Contents**

| 4  |

|----|

| 5  |

| 5  |

| 6  |

| 6  |

| 7  |

| 8  |

| 8  |

| 8  |

| 8  |

| 8  |

| 9  |

| 10 |

| 10 |

| 12 |

| 13 |

| 15 |

| 16 |

| 17 |

| 18 |

| 19 |

| 20 |

| 21 |

| 22 |

|    |

## **1** Power Estimator overview

The Achronix Power Estimator tool provides a platform to calculate the power requirements for Achronix Speedster 22i device families. This user guide gives a detailed overview of the various power components depending on the utilization of various components in the design. The power estimator tool can be used at any stage of the FPGA design to get an estimate of the total power dissipation from the device. It comes in handy to get a first hand estimate of the power specification at the start of the design so the design utilization can be altered based on the power requirements. This estimate could then be compared with post-implementation results for comparison purposes.

The Achronix Power Estimator is a spreadsheet that takes various parameters as inputs from the user to estimate the total power dissipated. This includes device characteristics, thermal characteristics and utilization of various components like BRAMs, LRAMs, I/Os, LUTs, Clocks and Hard IPs. To get a good estimate of the design's power profile, the user is required to enter a more realistic estimate of the design utilization.

## 2 System requirements and setup

- The Achronix Power Estimator tool is compatible with Microsoft Excel 2007

- For efficient functioning of the tool, macros should be enabled. By default, the security setting has macros disabled. This setting can be changed by enabling it in the Trust Center

- Click the Microsoft Office Button, and then click Excel Options.

- Click Trust Center, click Trust Center Settings, and then click Macro Settings.

- Enable macros

## 3.1 Power Central Worksheet

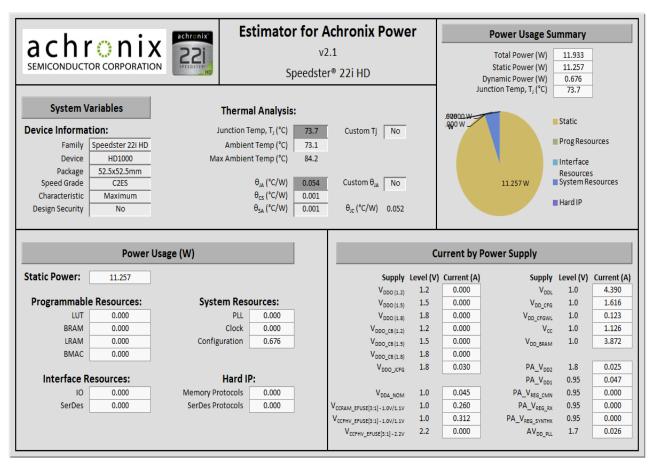

The Power Central worksheet is the main worksheet of the tool where the breakdown of various power dissipation components is displayed. It is split into four parts: System variables, Power usage in Watts, Current by power supply, Power usage summary

Figure 3-1 Power Central Worksheet

## 3.1.1 System variables

This part includes two sections which are the Device information and Thermal Analysis

#### **3.1.1.1 Device information**

The Device information takes in the following input parameters to calculate power

#### Table 3-1 System variables input parameters

| Parameter      | Description                                                                                              |

|----------------|----------------------------------------------------------------------------------------------------------|

| Family         | Achronix device for which power estimation need to be calculated                                         |

| Device         | Type of Speedster device : HD680/HD1000                                                                  |

| Package        | Type of package used :                                                                                   |

|                | 45x45 mm / 52.5x52.5 mm                                                                                  |

| Speed Grade    | This option allows the user to select the desired speed grade for the target                             |

|                | device: C2ES/C3ES                                                                                        |

|                | C2 offers fastest speed grade for HD1000 under normal conditions                                         |

| Characteristic | This option allows the user to select the device characteristics used for static power calculation:      |

|                | Typical – This is the average (50%) power dissipation characteristics used for static power calculation. |

|                | Maximum – Worst case device characteristics used for static power calculation.                           |

|                | In order to account for worst-case process variation, it is recommended to set the                       |

|                | characteristics to Maximum                                                                               |

| Design         | This option allows the user to enable or disable design security feature i.e if the                      |

| security       | application requires fuse blowing (eg. programming encryption fuses for design security)                 |

#### 3.1.1.2 Thermal Analysis

The following input parameters are present for user selection

| Parameter                                    | Description                                                                                                                                                                                                                                                             |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                              |                                                                                                                                                                                                                                                                         |

| Junction<br>Temperature, T <sub>J</sub> (°C) | The junction temperature or operating temperature refers to the temperature<br>of the silicon die within the package of the device when the device is<br>powered.                                                                                                       |

|                                              | $T_J = T_A + (P \times \theta_{JA})$ where<br>$T_J$ is the Junction temperature in °C<br>$T_A$ is the Ambient temperature in °C<br>P is the total power dissipated in Watts<br>$\theta_{JA}$ is the Junction-to-ambient thermal resistance in °C/W                      |

| Custom T <sub>J</sub>                        | Allows the user to enable/disable user-defined $T_J$<br>When custom $T_J$ is disabled, the junction temperature is calculated based on<br>the formula above and when enabled, the user has the choice to enter a<br>value.                                              |

| Ambient temperature,<br>(°C)                 | The ambient temperature refers to the temperature of the surrounding<br>environment (typically air) when the device is powered                                                                                                                                          |

| Max Ambient<br>temperature, (°C)             | The maximum ambient temperature should be such that the junction temperature does not exceed 85°C. Achronix devices support temperature range from 25 °C -85°C                                                                                                          |

| $\theta_{JA}$ (°C/W)                         | Junction-to-ambient thermal resistance $\theta_{JA} = \theta_{JC} + \theta_{CS} + \theta_{SA}$                                                                                                                                                                          |

| $\theta_{JC}(^{\circ}C/W)$                   | Junction-to-case thermal resistance                                                                                                                                                                                                                                     |

| $\theta_{\rm CS}(^{\circ}{\rm C/W})$         | Case-to-heat sink thermal resistance                                                                                                                                                                                                                                    |

| $\theta_{SA}(^{\circ}C/W)$                   | Heat sink-to-ambient thermal resistance                                                                                                                                                                                                                                 |

| Custom $\theta_{JA}$                         | This option when enabled, allows the user to enter a value for $\theta_{JA}$ keeping<br>the other thermal resistance values unchangeable<br>When disabled, the user may enter values for $\theta_{CS}$ and $\theta_{SA}$ and $\theta_{JA}$ is<br>calculated accordingly |

#### Table 3-2 Thermal Analysis input parameters

#### 3.1.2 Power Usage

#### 3.1.2.1 Power Dissipation in FPGA

The total power dissipated comprises two components; the static power and the dynamic power. Static power or standby power is the power dissipated when the device is in an unconfigured state after power-up. It depends on several factors including temperature, leakage current and operating voltages.

Dynamic or switching power dissipation is caused by switching activity inside FPGA and at I/O interfaces and is a function of switching frequency, operating voltage and capacitance. A higher operating frequency leads to more signal transitions thereby increasing dynamic power dissipation.

The power usage section gives a breakdown of the different power dissipation sources that contribute to static and dynamic power. These include

#### **Static Power**

The total static power value depends on the device and thermal characteristics. The maximum static power is 15W at 85 °C junction temperature for maximum (worst-case) device characteristic.

#### **Dynamic Power**

The remaining section in Power usage contributes towards dynamic power. The total dynamic power is a sum of all the following resources and Hard IPs

#### 3.1.2.2 Programmable resources

This section summarizes the power dissipated by the total LUTs, BRAMs, LRAMs and BMACs in the device. Each of these components has a separate worksheet for power calculation which will be explained in detail later in this document.

#### **3.1.2.3** Interface resources

This section includes power dissipated by I/O and SerDes interfaces in the device. Each of these components has a separate worksheet for power calculation which will be explained in detail later in this document.

#### 3.1.2.4 System resources

This includes power dissipated by the total PLLs and clocks used in the design and also the configuration power. The configuration power is the total power consumed from initial power up to stepping into user mode. The steps are illustrated in Table 3-1

#### Table 3-1 Power-up and Configuration Sequencing steps

| 1                | 2                     | 3                      | 4                     | 5                     | 6            | 7                   | 8            |

|------------------|-----------------------|------------------------|-----------------------|-----------------------|--------------|---------------------|--------------|

| Device<br>power- | Read non-<br>volatile | Clear<br>configuration | Bitstream<br>sync and | Load<br>configuration | CRC<br>check | Startup<br>sequence | User<br>mode |

| up               | memories              | memory                 | device ID             | bits                  |              |                     |              |

The configuration power for Achronix HD1000 device is set at 0.676 W

#### 3.1.2.5 Hard IP

This section lists the power consumed by the hard IPs used in the design. They are split into the following protocols accordingly.

Memory Protocols: This section includes the power consumed by the DDR controller Hard IP

**SerDes Protocols:** This section includes the power consumed by the other Hard IPs like 10G/40G/100G Ethernet, Interlaken and PCI Express

A more detailed review of the Hard IPs will be addressed in the Hard IP worksheet later in this document. Fig 3-2 shows the Power Usage section in the Power Central worksheet

| Static Power:  |            |                  |            |

|----------------|------------|------------------|------------|

| Static Power.  | 11.206     | ]                |            |

| Programmable F | Resources: | System Reso      | ources:    |

| LUT            | 0.187      | PLL              | 0.007      |

| BRAM           | 0.000      | Clock            | 0.007      |

| LRAM           | 0.000      | Configuration    | 0.676      |

| BMAC           | 0.000      |                  |            |

| Interface Res  | ources:    | Hard I           | <b>•</b> : |

| IO             | 0.003      | Memory Protocols | 0.000      |

| SerDes         | 0.607      | SerDes Protocols | 1.655      |

Fig 3-2 Power Usage section

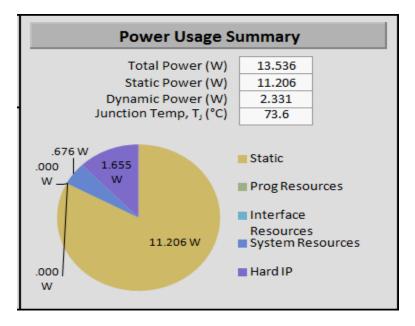

#### 3.1.3 Power Usage Summary

This section provides a summary of all the power dissipation components like the Total Power (W), Static Power (W) and Dynamic Power (W). It also provides a pie diagram of the different power components. Fig 3-3 shows a list of power components and the associated pie diagram.

Fig. 3-3 Power Usage Summary

#### 3.1.4 Current by Power Supply

This section lists the various Supply voltages and the associated current in the fabric. Fig 3-4 shows the current by power supply section in the Power Central worksheet and Table 3-2 describes the various voltage supplies used in power calculation

|                                          | Cu        | irrent by F | Power Supply               |           |             |

|------------------------------------------|-----------|-------------|----------------------------|-----------|-------------|

| Supply                                   | Level (V) | Current (A) | Supply                     | Level (V) | Current (A) |

| V <sub>DDO (1.2)</sub>                   | 1.2       | 0.000       | V <sub>DDL</sub>           | 1.0       | 4.370       |

| V <sub>DDO (1.5)</sub>                   | 1.5       | 0.000       | V <sub>DD_CFG</sub>        | 1.0       | 1.609       |

| V <sub>DDO (1.8)</sub>                   | 1.8       | 0.000       | V <sub>DD_CFGWL</sub>      | 1.0       | 0.122       |

| V <sub>DDO_CB (1.2)</sub>                | 1.2       | 0.000       | V <sub>cc</sub>            | 1.0       | 2.775       |

| V <sub>DDO_CB</sub> (1.5)                | 1.5       | 0.000       | V <sub>DD_BRAM</sub>       | 1.0       | 3.855       |

| V <sub>DDO_CB (1.8)</sub>                | 1.8       | 0.000       |                            |           |             |

| V <sub>DDO_JCFG</sub>                    | 1.8       | 0.030       | PA_V <sub>DD2</sub>        | 1.8       | 0.025       |

|                                          |           |             | PA_V <sub>DD1</sub>        | 0.95      | 0.047       |

| V <sub>DDA_NOM</sub>                     | 1.0       | 0.045       | PA_V <sub>REG_CMN</sub>    | 0.95      | 0.000       |

| V <sub>CCRAM_EFUSE[3:1]</sub> -1.0V/1.1V | 1.0       | 0.260       | PA_V <sub>REG_RX</sub>     | 0.95      | 0.000       |

| V <sub>CCFHV_EFUSE[3:1]</sub> -1.0V/1.1V | 1.0       | 0.312       | PA_V <sub>REG_SYNTHX</sub> | 0.95      | 0.000       |

| V <sub>CCFHV_EFUSE[3:1]-2.2V</sub>       | 2.2       | 0.000       | AV <sub>DD_PLL</sub>       | 1.7       | 0.026       |

|                                          |           |             |                            |           |             |

| Fig. | 3-4 | Current | bv | Power | supply |

|------|-----|---------|----|-------|--------|

| B'   | • • |         | ~, |       | Sepp-J |

#### Table 3-2 Voltage Supplies Used In Power Calculation

| Parameter      | Description                                                                                                                             |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| VDDL           | Power supply for FPGA core                                                                                                              |

| VDD_CFG        | Supply voltage for the configuration memory SRAM cells in the FPGA fabric                                                               |

| VDD_CFGWL      | Power Supply for the word lines of the configuration memory SRAM cells in the FPGA fabric                                               |

| VCC            | Digital Power Supply for FPGA circuitry in the I/O ring, including the Hard IP                                                          |

| VDD_BRAM       | Power Supply for Block RAMS in Fabric including BRAM internal circuitry like write/read timers, address decoders, sense amplifiers etc. |

| PA_VDD2        | SerDes Analog High Power Supply                                                                                                         |

| PA_VDD1        | SerDes Analog Low Power Supply                                                                                                          |

| PA_VREG_CMN    | SerDes Regulator Power Supply                                                                                                           |

| PA_VREG_RX     | SerDes Regulator Power Supply                                                                                                           |

| PA_VREG_SYNTHX | SerDes Regulator Power Supply                                                                                                           |

| AVDD_PLL       | Analog power supply for the PLLs feeding the FPGA core fabric.                                                                          |

| VDDO           | Bank I/O supply voltage                                                                                                                 |

| VDDO_CB        | Power Clock bank I/O supply voltage                                                                                                     |

| VDDO_JCFG      | Supply voltage powering the I/O buffers for the IEEE 1149.1 JTAG interface                                                              |

| VDDA_NOM       | Analog Power Supply for FPGA circuitry in the I/O ring                                                                                  |

| VCCRAM_EFUSE   | Efuse Power Supply normal / read operations                                                                                             |

| VCCFHV_EFUSE   | Efuse Power Supply for Fuse Program / Erase operations                                                                                  |

More details on these power supplies can be found in <u>http://www.achronix.com/wp-content/uploads/docs/Speedster22i\_PinConnections\_PowerSequencing\_User\_Guide\_UG042.pdf</u>

## 3.2 LUT Worksheet

The LUT power worksheet summarizes the percentage of the total available LUT utilization and dynamic power estimation for the total LUTs used in the design

It also contains a section to enter the values of the following parameters on the LUT usage in the design

- Function

- LUT count

- FF count

- Clock (MHz)

- Toggle rate

- Fanout

- Power (W)

#### LUT Power

| Device Utilization:   |         |    | Dynamic Powe        | er Summary |

|-----------------------|---------|----|---------------------|------------|

| Device:               | HD1000  |    | LUT Power (W):      | 0.000      |

| Available LUTs / FFs: | 700,000 |    | % of Total Dynamic: | 0.00%      |

| Used LUTs:            | 0       | 0% |                     |            |

| Used FFs:             | 0       | 0% |                     |            |

| Function | LUT Count | FF Count | Clock<br>(MHz) | Toggle Rate | Fanout | Power (W) |

|----------|-----------|----------|----------------|-------------|--------|-----------|

|          | 0         | 0        | 100            | 12.5%       | Medium | 0.000     |

|          |           |          |                | 12.5%       | Medium | 0.000     |

|          |           |          |                | 12.5%       | Medium | 0.000     |

|          |           |          |                | 12.5%       | Medium | 0.000     |

|          |           |          |                | 12.5%       | Medium | 0.000     |

|          |           |          |                | 12.5%       | Medium | 0.000     |

|          |           |          |                | 12.5%       | Medium | 0.000     |

Fig 3-5 LUT Worksheet

| Input parameter | Description                                                                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function        | Description about the functionality/module associated with the LUT. This entry is optional                                                                                                  |

| LUT count       | The number of LUT used in the function/module of the design                                                                                                                                 |

| FF count        | The total flipflop count used with the LUTs                                                                                                                                                 |

| Clock (MHz)     | The maximum clock frequency that is driving the logic                                                                                                                                       |

| Toggle rate     | The percentage at which the logic toggles on each clock cycle                                                                                                                               |

| Fanout          | The average number of blocks that will be driven by the LUTs and flipflops.<br>The value ranges from very low, low, medium to high and very high.                                           |

| Power (W)       | This column calculates the total power use by the LUTs and flipflops and its contribution towards the total dynamic power percentage which will be reflected in the Power Central worksheet |

#### Table 3-3 Input Parameters on LUT Power worksheet

## 3.3 BRAM worksheet

The BRAM Power worksheet summarizes the total BRAM percentage used versus the available BRAMs and the total dynamic power dissipation percentage depending on the values entered on the following input parameters. It also displays the voltage supply and current flow as a result of BRAM utilization.

VDDL supply is used to power some of the peripheral circuitry used to help interface BRAM with surrounding circuitry and routing

VDD\_BRAM supply is used to power BRAM internal circuitry like write/read timers, address decoders, sense amplifiers etc.

#### **BRAM Power**

| Device:         HD1000         BRAM Power (W):         0.000           Available BRAMs:         1,026         % of Total Dynamic:         0.00% | Device Utilization: |        | _  | Dynamic Powe        | r Summary | 1 |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------|----|---------------------|-----------|---|

|                                                                                                                                                 | Device:             | HD1000 |    | BRAM Power (W):     | 0.000     |   |

| Used BRAMs: 0 0%                                                                                                                                | Available BRAMs:    | 1,026  |    | % of Total Dynamic: | 0.00%     |   |

|                                                                                                                                                 | Used BRAMs:         | 0      | 0% |                     |           |   |

| Function BRAM<br>Count |      |                  | Port A         |                | Port B   |                |                |              |       |

|------------------------|------|------------------|----------------|----------------|----------|----------------|----------------|--------------|-------|

|                        | Mode | Data Org         | Clock<br>(MHz) | Toggle<br>Rate | Data Org | Clock<br>(MHz) | Toggle<br>Rate | Power<br>(W) |       |

|                        | 0    | Simple Dual Port | x40            |                | 25.0%    | x40            |                | 25.0%        | 0.000 |

|                        |      | Simple Dual Port | x40            |                | 25.0%    | x40            |                | 25.0%        | 0.000 |

|                        |      | Simple Dual Port | x40            |                | 25.0%    | x40            |                | 25.0%        | 0.000 |

|                        |      | Simple Dual Port | x40            |                | 25.0%    | x40            |                | 25.0%        | 0.000 |

|                        |      | Simple Dual Port | x40            |                | 25.0%    | x40            |                | 25.0%        | 0.000 |

|                        |      | Simple Dual Port | x40            |                | 25.0%    | x40            |                | 25.0%        | 0.000 |

|                        |      | Simple Dual Port | x40            |                | 25.0%    | x40            |                | 25.0%        | 0.000 |

#### Fig 3-6 BRAM Worksheet

#### Table 3-4 Input Parameters on BRAM Power worksheet

| Input parameter | Description                                                                                                                                                                                                                                                                                                                               |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function        | Description about the functionality/module associated with the BRAM. This entry is optional                                                                                                                                                                                                                                               |

| BRAM count      | The number of BRAM used in the function/module of the design                                                                                                                                                                                                                                                                              |

| Mode            | BRAM mode of operation: ROM/Single port/Simple dual port/True dual port<br>A single-port RAM has one port with a read and write control signal. A simple<br>dual-port RAM has one read port and one write port. A true dual-port RAM has<br>two ports, each with a read and write control signal. ROMs are read-only single-<br>port RAMs |

| Data Org        | The data width of BRAMs for Port A and Port B. The values range from x1 to x40                                                                                                                                                                                                                                                            |

| Clock (MHz)     | The maximum clock frequency that is driving the BRAMs at Port A and Port B.<br>Port B is ignored in case of single port or ROM based BRAMs                                                                                                                                                                                                |

| Toggle rate     | The percentage at which the logic toggles on each clock cycle on Port A and Port B.                                                                                                                                                                                                                                                       |

| Power (W)       | This column calculates the total power use by the BRAMs and its contribution<br>towards the total dynamic power percentage which will be reflected in the<br>Power Central worksheet                                                                                                                                                      |

## 3.4 LRAM worksheet

The LRAM Power worksheet summarizes the total LRAM percentage used versus the available LRAMs and the total dynamic power dissipation percentage depending on the values entered on the following input parameters

| LRAM Power |       |                     |                                                                                                       |  |

|------------|-------|---------------------|-------------------------------------------------------------------------------------------------------|--|

|            |       | Dynamic Power Su    | immary                                                                                                |  |

| HD1000     |       | LRAM Power (W):     | 0.000                                                                                                 |  |

| 6,156      |       | % of Total Dynamic: | 0.00%                                                                                                 |  |

| 0          | 0%    |                     |                                                                                                       |  |

|            | 6,156 | HD1000<br>6,156     | Dynamic Power Su           HD1000         LRAM Power (W):           6,156         % of Total Dynamic: |  |

| Function | LRAM Count | Clock<br>(MHz) | Toggle Rate | Power (W) |

|----------|------------|----------------|-------------|-----------|

|          |            |                | 25.0%       | 0.000     |

|          |            |                | 25.0%       | 0.000     |

|          |            |                | 25.0%       | 0.000     |

|          |            |                | 25.0%       | 0.000     |

|          |            |                | 25.0%       | 0.000     |

|          |            |                | 25.0%       | 0.000     |

|          |            |                | 25.0%       | 0.000     |

|          |            |                | 25.0%       | 0.000     |

#### Fig 3-7 LRAM Worksheet

#### Table 3-5 Input Parameters on LRAM Power worksheet

| Input parameter | Description                                                                                                                                                                          |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function        | Description about the functionality/module associated with the LRAM. This entry is optional                                                                                          |

| LRAM count      | The number of LRAM used in the function/module of the design                                                                                                                         |

| Clock (MHz)     | The maximum clock frequency that is driving the LRAMs                                                                                                                                |

| Toggle rate     | The percentage at which the logic toggles on each clock cycle                                                                                                                        |

| Power (W)       | This column calculates the total power use by the BRAMs and its contribution<br>towards the total dynamic power percentage which will be reflected in the<br>Power Central worksheet |

## 3.5 BMAC worksheet

The BMAC Power worksheet summarizes the total BMAC percentage used versus the available BMACs and the total dynamic power dissipation percentage depending on the values entered on the following input parameters

| Device Utilization: |        |    | Dynamic Power Su    | ımmary |

|---------------------|--------|----|---------------------|--------|

| Device:             | HD1000 |    | BMAC Power (W):     | 0.000  |

| Available BMACs:    | 756    |    | % of Total Dynamic: | 0.00%  |

| Used BMACs:         | 0      | 0% |                     |        |

| Function | BMAC Count | Clock<br>(MHz) | Toggle Rate | Power (W) |

|----------|------------|----------------|-------------|-----------|

|          |            |                | 12.5%       | 0.000     |

|          |            |                | 12.5%       | 0.000     |

|          |            |                | 12.5%       | 0.000     |

|          |            |                | 12.5%       | 0.000     |

|          |            |                | 12.5%       | 0.000     |

|          |            |                | 12.5%       | 0.000     |

#### Fig 3-8 BMAC Worksheet

#### Table 3-6 Input Parameters on BMAC Power worksheet

| Input parameter | Description                                                                                                                                                                          |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function        | Description about the functionality/module associated with the BMAC. This entry is optional                                                                                          |

| BMAC count      | The number of BMAC used in the function/module of the design                                                                                                                         |

| Clock (MHz)     | The maximum clock frequency that is driving the BMACs                                                                                                                                |

| Toggle rate     | The percentage at which the logic toggles on each clock cycle                                                                                                                        |

| Power (W)       | This column calculates the total power use by the BMACs and its contribution<br>towards the total dynamic power percentage which will be reflected in the<br>Power Central worksheet |

## **BMAC** Power

## 3.6 I/O worksheet

The I/O Power worksheet summarizes the total I/O percentage used versus the available I/Os and the total dynamic power dissipation percentage depending on the values entered on the following input parameters. It also displays the voltage supply and current flow as a result of I/O utilization.

#### **IO** Power **Device Utilization: Dynamic Power Summary** Supply Level (V) Current (A) Power (W) Supply Level (V) Current (A) Power (W) HD1000 GPIO Power (W): 0.000 Vcc 1.0 0.000 0.000 V<sub>DDA\_NOM</sub> V<sub>DDO\_CB (1.2)</sub> 1.0 0.000 0.000 % of Total Dynamic: 0.000 52.5x52.5mm 0.000 0.000 0.000 0.000 1.2 1.5 0.000 0.000 0.000 0.000 Package: V<sub>DDO (1.2)</sub> 1.2 1.5 VDD0 (1.5) VDD0 C8 (1.5) GPIOs Clock IOs V<sub>DDO (1.8)</sub> 1.8 0.000 0.000 VDDO\_C8 (1.8) 1.8 0.000 0.000 Available: 936 24 Used: 0 0 0% 0% Bidi Data Clock Load Input Output Input Output Toggle Function IO Standard Ю Туре OE Rate Term Pins Pins Pins Rate (MHz) Rate (pf) Term On Off On 12.5% 100.0% Off 12.5% 100.0% Off Off 100.0% 12.5% Off Off Off 12.5% 100.0% Off 12.5% 100.0%

#### Table 3-7 Input Parameters on I/O Power worksheet

| Input Parameter    | Description                                                                     |

|--------------------|---------------------------------------------------------------------------------|

| Function           | Description about the functionality/module associated with the I/Os. This entry |

|                    | is optional                                                                     |

| I/O standard       | Selection of industry standard I/O used for the I/Os. The dynamic power varies  |

|                    | with the selection of I/O standard                                              |

| I/O type           | Type of I/O used: GPI/O/Clock I/O                                               |

| Input termination  | Option to select if input termination is used or not                            |

| Output termination | Option to select if output termination is used or not                           |

| Input pins         | Total number of I/Os used as input pins                                         |

| Output pins        | Total number of I/Os used as output pins                                        |

| Bidirectional pins | Total number of I/Os used as bidirectional pins                                 |

| Data rate          | Option to choose between Single Data rate or Double Data Rate                   |

| Clock (MHz)        | The maximum clock frequency at which the I/Os are toggling                      |

| Toggle rate        | The percentage at which the I/Os toggle on each clock cycle                     |

| OE rate   | The percentage of time for which the output I/O pins is enabled and bidirectional I/O pins are output pins and enabled. |

|-----------|-------------------------------------------------------------------------------------------------------------------------|

|           | The time for which OE is disabled, the bidirectional I/Os are inputs and output I/O pins are tristated                  |

| Load (pF) | The value of I/O pin capacitance loading                                                                                |

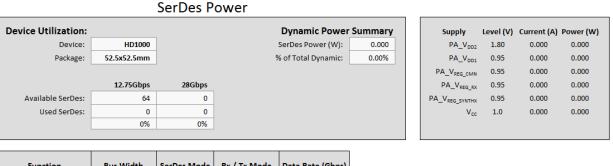

## 3.7 SerDes worksheet

The SerDes Power worksheet summarizes the total SerDes percentage used I/Os and the total dynamic power dissipation percentage depending on the values entered on the following input parameters. It also displays the voltage supply and current flow as a result of SerDes utilization.

$PA_V_{DD1}$ ,  $PA_V_{DD2}$ ,  $PA_V_{REG_{CMIN}}$ ,  $PA_V_{REG_{RX}}$  and  $PA_V_{REG_{SYNTHX}}$  are used to power the PMA and  $V_{CC}$  power supply is used to power PCS of SerDes.

| Function | Bus Width | SerDes Mode | Rx / Tx Mode | Data Rate (Gbps) |

|----------|-----------|-------------|--------------|------------------|

|          |           |             | Tx and Rx    |                  |

|          |           |             | Tx and Rx    |                  |

|          |           |             | Tx and Rx    |                  |

|          |           |             | Tx and Rx    |                  |

|          |           |             | Tx and Rx    |                  |

#### Fig 3-10 SerDes Worksheet

#### **Table 3-8 Input Parameters on SerDes Power worksheet**

| Input Parameter | Description                                                                                                             |

|-----------------|-------------------------------------------------------------------------------------------------------------------------|

| Function        | Description about the functionality/module associated with the SerDes. This entry is optional                           |

| Bus Width       | Defines the number of data bits used by the SerDes interface                                                            |

| SerDes mode     | SerDes operation mode: 12.75 Gbps/28 Gbps<br>Note: 28 Gbps SerDes will no longer be supported in Speedster22i HD family |

| Rx/Tx mode       | Defines whether the Serdes would be used in Tx mode or Rx mode or both Tx and Rx                             |

|------------------|--------------------------------------------------------------------------------------------------------------|

| Data Rate (Gbps) | Desired transmit and receive data rates for SerDes. The data rate must be between 1.0625 Gbps and 12.75 Gbps |

## 3.8 PLL Worksheet

The PLL Power worksheet summarizes the total PLL percentage used of the 16 available PLLs and the total dynamic power dissipation percentage depending on the values entered on the following input parameters.

## **PLL Power**

| Device Utilization: |        | Dynamic Pov | wer Summary         |       |

|---------------------|--------|-------------|---------------------|-------|

| Device:             | HD1000 | ]           | PLL Power (W):      | 0.000 |

| Available PLLs:     | 16     |             | % of Total Dynamic: | 0.00% |

| Used PLLs:          | 0      | 0%          |                     |       |

|                     |        |             |                     |       |

| Function | PLL Count | VCO Freq<br>(MHz) | Power (W) |

|----------|-----------|-------------------|-----------|

|          |           |                   | 0.000     |

|          |           |                   | 0.000     |

|          |           |                   | 0.000     |

|          |           |                   | 0.000     |

#### Fig 3-11 PLL Worksheet

#### Table 3-9 Input Parameters on PLL Power worksheet

| Input Parameter     | Description                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------|

| Function            | Description about the functionality/module associated with the PLLs. This entry is optional |

| PLL count           | Total PLL count used                                                                        |

| VCO Frequency (MHz) | VCO output frequency. Allowed range is between 1250 MHz and 2500 MHz                        |

## 3.9 Clock Worksheet

The Clock Power worksheet summarizes the total dynamic power dissipation percentage depending on the values entered on the following input parameters.

# Device Utilization: Dynamic Power Summary Device: HD1000 Clock Power (W): 0.000 % of Total Dynamic: 0.00%

| Function | Clock Type | Clock<br>(MHz) | Fanout | Enable | Power (W) |

|----------|------------|----------------|--------|--------|-----------|

|          |            |                |        | 100.0% | 0.000     |

|          |            |                |        | 100.0% | 0.000     |

|          |            |                |        | 100.0% | 0.000     |

|          |            |                |        | 100.0% | 0.000     |

|          |            |                |        | 100.0% | 0.000     |

|          |            |                |        | 100.0% | 0.000     |

#### Fig 3-12 Clock Worksheet

#### Table 3-10 Input Parameters on Clock Power worksheet

| Input Parameter | Description                                                                                              |

|-----------------|----------------------------------------------------------------------------------------------------------|

| Function        | Description about the functionality/module associated with the clocks. This entry is optional            |

| Clock type      | Defines whether the clock used is a direct or global clock                                               |

| Clock (MHz)     | Clock output frequency                                                                                   |

| Fanout          | The total fanout from the output of clock network to all registers including LUTs, BRAMs, LRAMs and MACs |

| Enable          | The percentage of time for which the clock tree is enabled                                               |

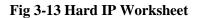

## 3.10 Hard IP Worksheet

The Hard IP Power worksheet summarizes the total hard IP percentage used of the available IPs and the total dynamic power dissipation percentage depending on the values entered on the following input parameters.

| Hard IP Power                             |              |              |               |            |             |                |                     |       |

|-------------------------------------------|--------------|--------------|---------------|------------|-------------|----------------|---------------------|-------|

| Device Utilization: Dynamic Power Summary |              |              |               |            |             |                |                     |       |

| Device:                                   | HD1000       |              |               |            |             |                | Hard IP Power (W):  | 0.000 |

| Package:                                  | 52.5x52.5mm  |              |               |            |             | 9              | % of Total Dynamic: | 0.00% |

|                                           |              |              |               |            |             |                |                     |       |

|                                           | 10G Ethernet | 40G Ethernet | 100G Ethernet | Interlaken | PCI Express | DDR Controller | _                   |       |

| Available:                                | 24           | 6            | 2             | 2          | 2           | 6              |                     |       |

| Used:                                     | 0            | 0            | 0             | 0          | 0           | 0              |                     |       |

|                                           | 0%           | 0%           | 0%            | 0%         | 0%          | 0%             |                     |       |

|                                           |              |              |               |            |             |                | _                   |       |

| Power (W):                                | 0.000        | 0.000        | 0.000         | 0.000      | 0.000       | 0.000          |                     |       |

|                                           |              |              |               |            |             |                |                     |       |

| Function | IP | Instance<br>Count | Lanes | Mode /<br>Frequency | Power (W) |

|----------|----|-------------------|-------|---------------------|-----------|

|          |    |                   |       |                     | 0.000     |

|          |    |                   |       |                     | 0.000     |

|          |    |                   |       |                     | 0.000     |

|          |    |                   |       |                     | 0.000     |

| <b>Table 3-11 Input Parameters on</b> | Hard IP Power worksheet |

|---------------------------------------|-------------------------|

|---------------------------------------|-------------------------|

| Input Parameter | Description                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------|

| Function        | Description about the functionality/module associated with the hard IP. This entry is optional       |

| IP              | Defines the IP used : 10G/40G/100G Ethernet/Interlaken/PCI Express/<br>DDR Controller                |

| Instance count  | The total number of instances for each IP                                                            |

| Lanes           | The total number of lanes for each IP. The allowed number of lanes vary with the selection of the IP |

| Mode/Frequency  | The mode/frequency at which the Hard IP operates                                                     |

## 4 Release History

| Date      | DateVersionComments |                          |

|-----------|---------------------|--------------------------|

| 7/28/2015 | 1.0                 | Initial Achronix release |