# Speedcore Component Library User Guide (UG065)

Speedcore eFPGA

# Copyrights, Trademarks and Disclaimers

Copyright © 2023 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedster and VectorPath are registered trademarks, and Speedcore and Speedchip are trademarks of Achronix Semiconductor Corporation. All other trademarks are the property of their prospective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

### **Achronix Semiconductor Corporation**

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail : info@achronix.com

# **Table of Contents**

| Chapter - 1: Introduction                           | 10 |

|-----------------------------------------------------|----|

| ACX_ Prefix                                         | 10 |

| Chapter - 2: Fabric Architecture                    | 11 |

| Introduction                                        | 11 |

| RLB6 for Gen4 Speedcore eFPGAs                      | 12 |

| Routing Between RLB6s                               |    |

| RLB6 Detail                                         | 16 |

| RLB6 for Gen5 Speedcore eFPGAs                      |    |

| Routing Between RLB6s                               |    |

| Lookup Table (LUT) Functions                        |    |

| Six-Input Lookup Table (ACX_LUT6)                   |    |

| Speedcore Registers                                 |    |

| Naming Convention                                   |    |

| Register Primitives                                 | 29 |

| Register Macros                                     | 60 |

| Boundary Pin Cells                                  |    |

| IPIN (Input Data Pin)<br>ACX_OPIN (Output Data Pin) |    |

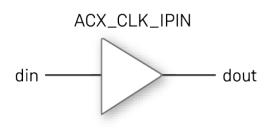

| ACX_CLK_IPIN (Input Clock Pin)                      |    |

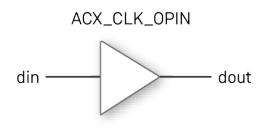

| ACX_CLK_OPIN (Output Clock Pin)                     |    |

| Chapter - 3: Logic Functions                        | 84 |

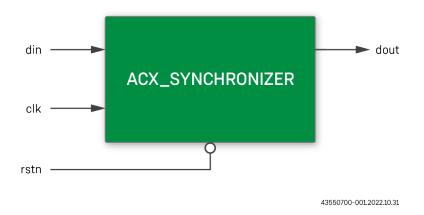

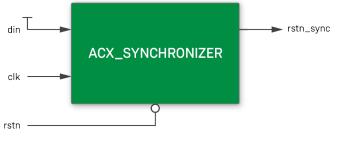

| ACX_SYNCHRONIZER, ACX_SYNCHRONIZER_N                |    |

| Using ACX_SYNCHRONIZER to Synchronize Reset         |    |

| Instantiation Templates                             | 86 |

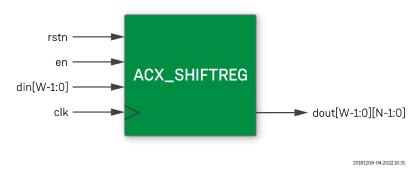

| ACX_SHIFTREG                                        |    |

| Instantiation Templates                             |    |

| Chapter - 4: Clock Functions                        |    |

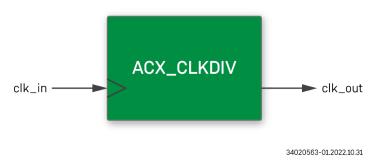

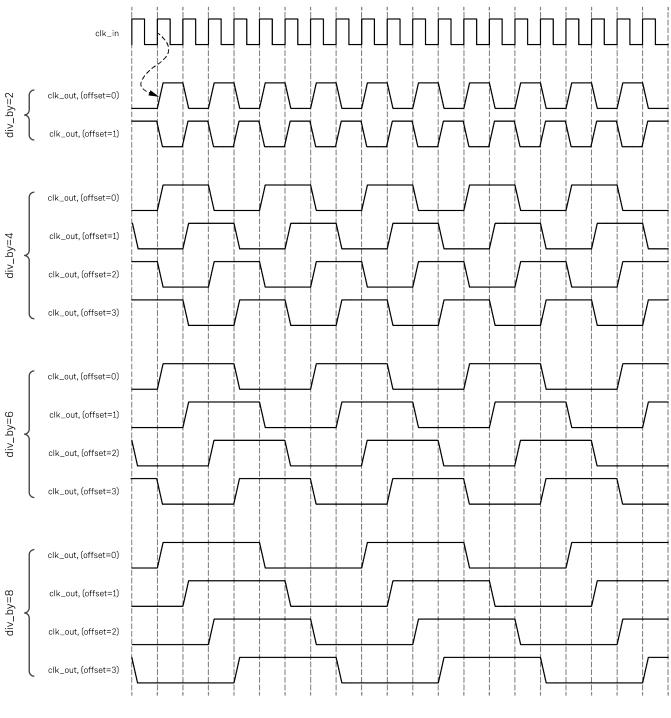

| ACX_CLKDIV (Clock Divider)                          |    |

| Instantiation Templates                             |    |

|                                                     |    |

| ACX_CLKGATE (Clock Gate)                                                                          |     |

|---------------------------------------------------------------------------------------------------|-----|

| ACX_CLKSWITCH (Clock Switch)<br>Constraints<br>Instantiation Templates                            | 98  |

| Chapter - 5: Arithmetic and DSP Functions                                                         |     |

| ACX_ALU8<br>Description                                                                           | 99  |

| Parameters Ports                                                                                  | 100 |

| Functions                                                                                         |     |

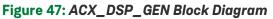

| ACX_DSP_GEN                                                                                       | 102 |

| Parameters                                                                                        |     |

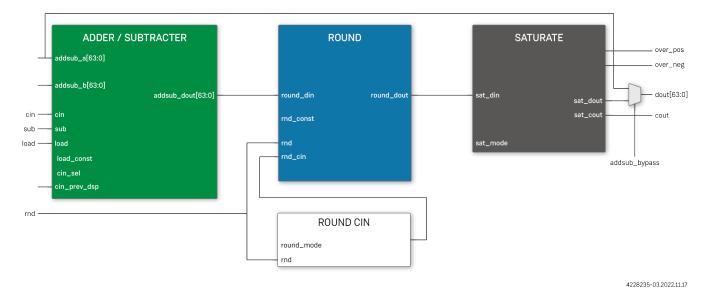

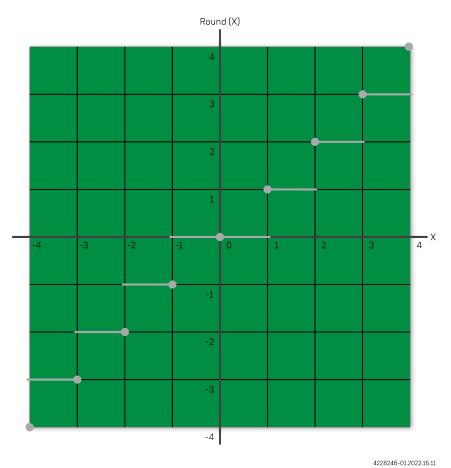

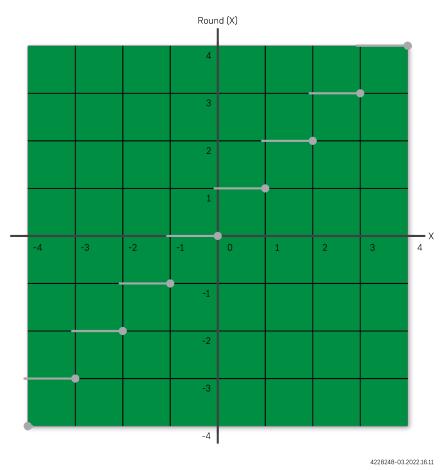

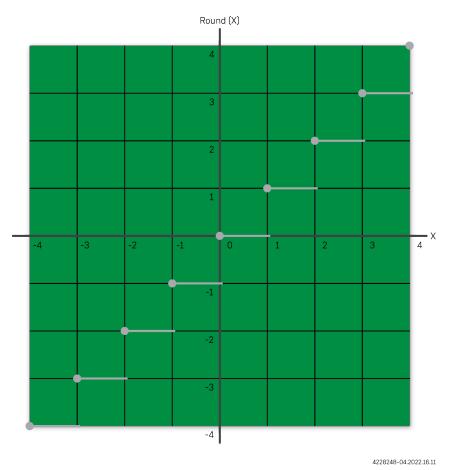

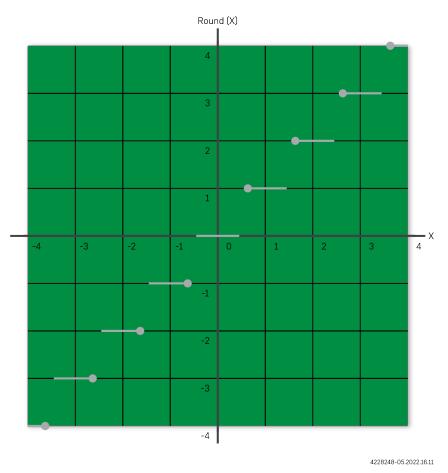

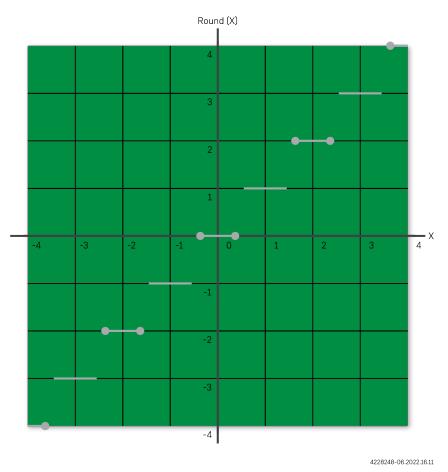

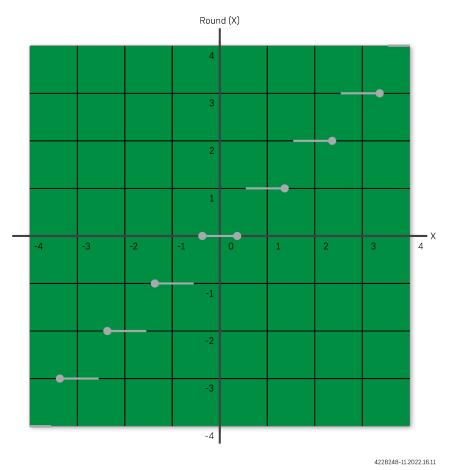

| ACX_DSP_GEN RoundingACX_DSP_GEN Verilog Instantiation Template                                    | 136 |

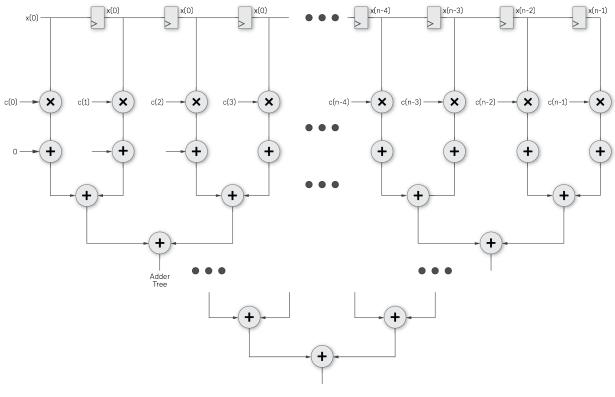

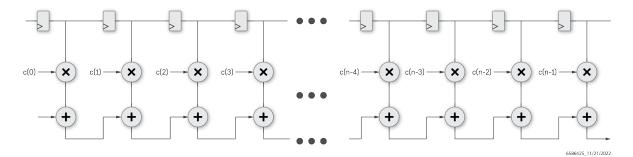

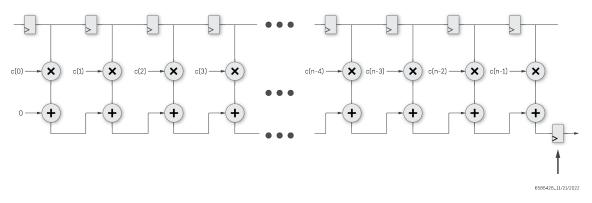

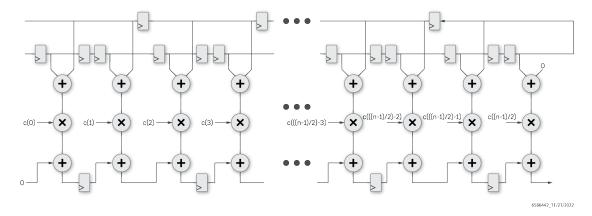

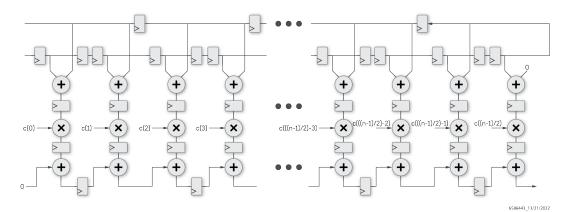

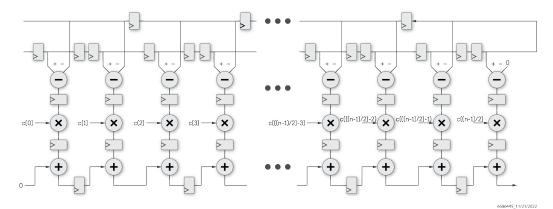

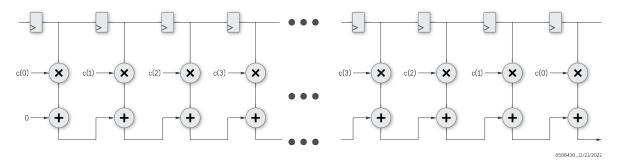

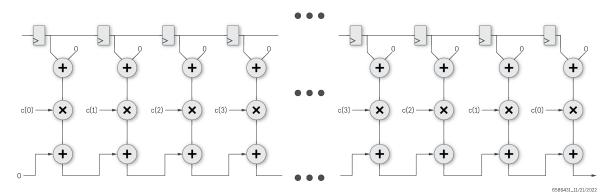

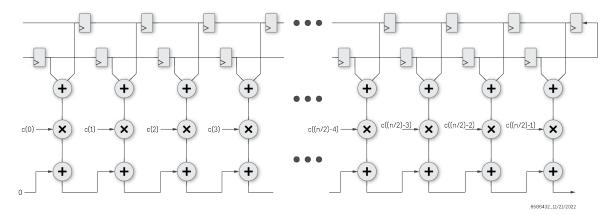

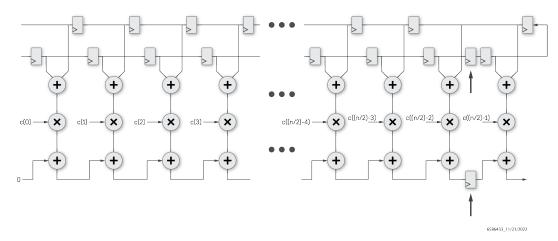

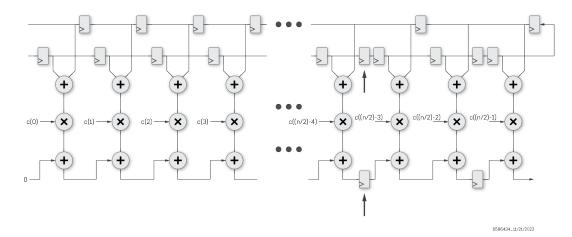

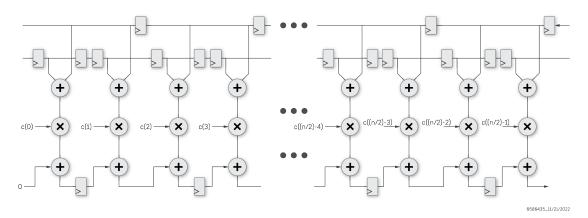

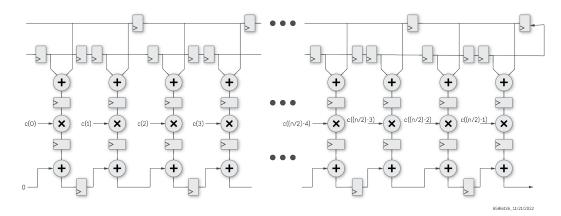

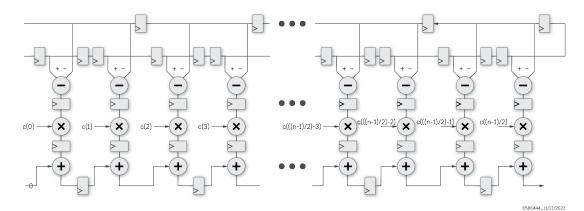

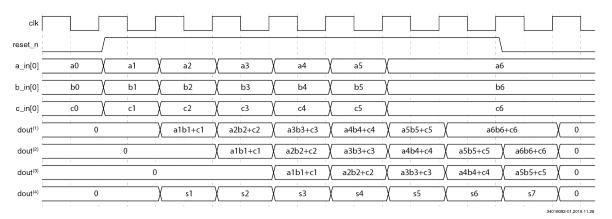

| ACX_DSP_GEN Verilog Inference Template         Implementing Finite Impulse Response (FIR) Filters |     |

| ACX_DSP_MACC_GEN                                                                                  | 151 |

| ACX_DSP_ACCUMULATOR_GEN                                                                           |     |

| ACX_DSP_COUNTER_GEN                                                                               |     |

| ACX_DSP_SUM_SQUARES_GEN<br>Timing                                                                 |     |

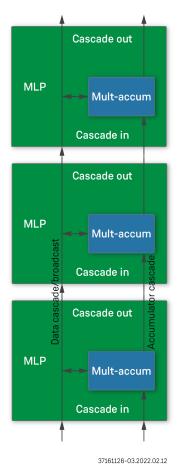

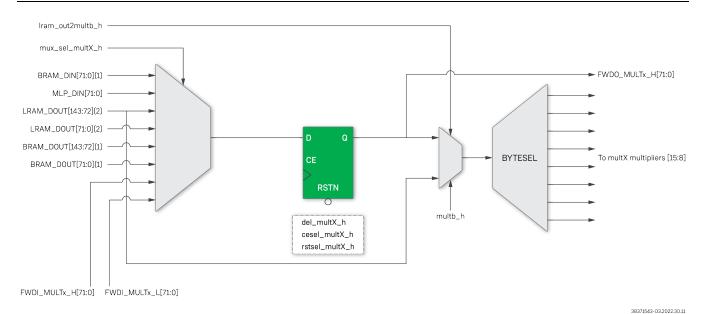

| ACX_MLP72                                                                                         | 162 |

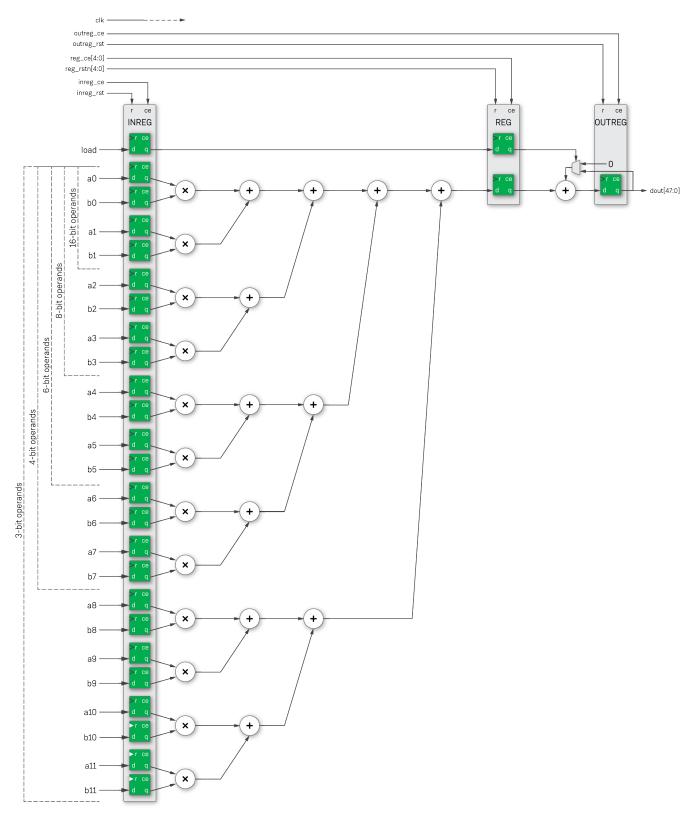

| Parallel Multiplications                                                                          |     |

| Instantiation                                                                                     |     |

| Common Stages                                                                                     |     |

| Integer Modes                                                                                     |     |

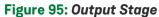

| Integrated LRAM                        | 186 |

|----------------------------------------|-----|

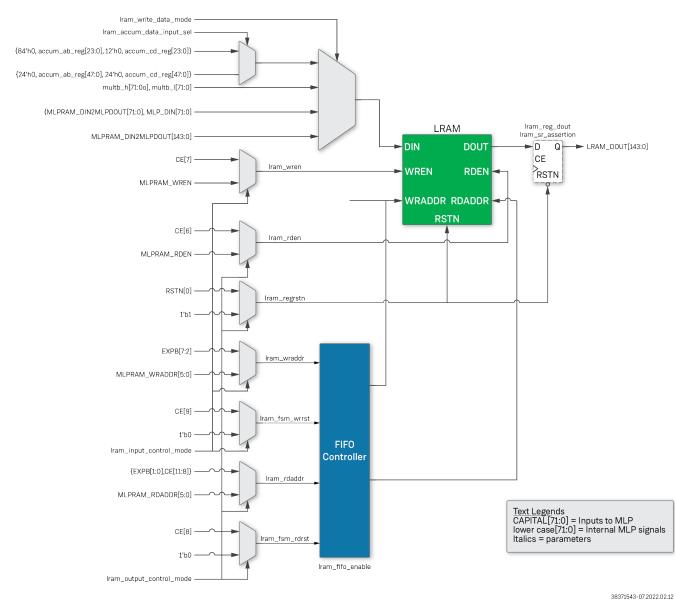

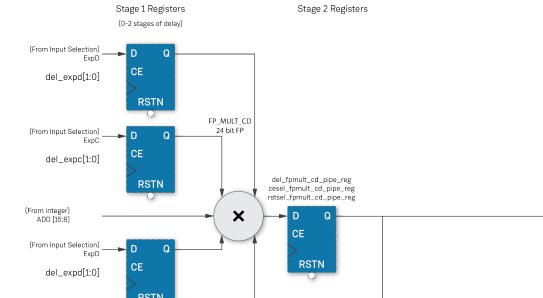

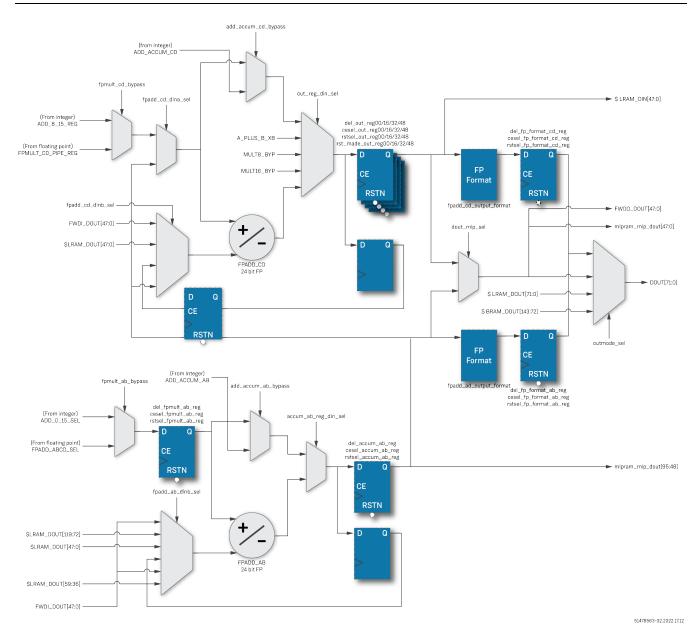

| Block Floating-Point Modes             | 193 |

| Floating-Point Modes                   | 200 |

| Instantiation Template                 | 211 |

| MLP72_INT                              |     |

| Parameters                             | 216 |

| Ports                                  | 217 |

| Input Data Mapping                     | 218 |

| Output Formatting and Error Conditions | 220 |

| Asynchronous Reset Rules               | 220 |

| Inference                              | 220 |

| Instantiation Template                 | 221 |

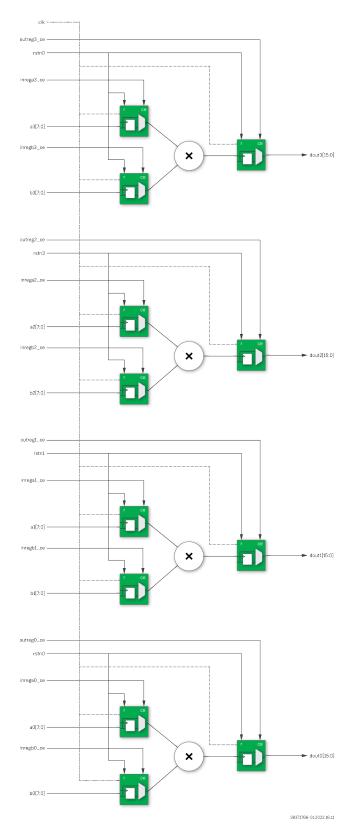

| MLP72_INT8_MULT_4X                     | 222 |

| Parameters                             |     |

| Ports                                  | 225 |

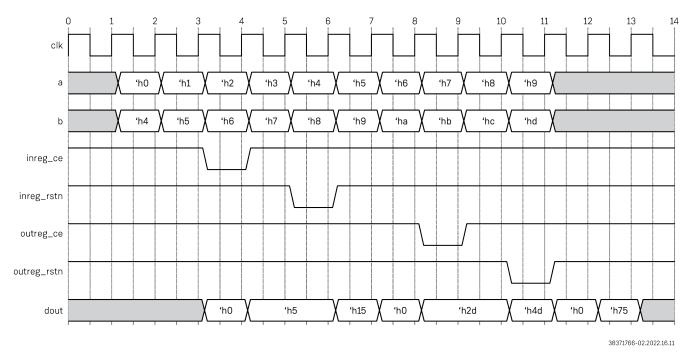

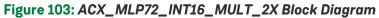

| Timing Diagrams                        | 226 |

| Inference                              | 227 |

| Instantiation Template                 | 229 |

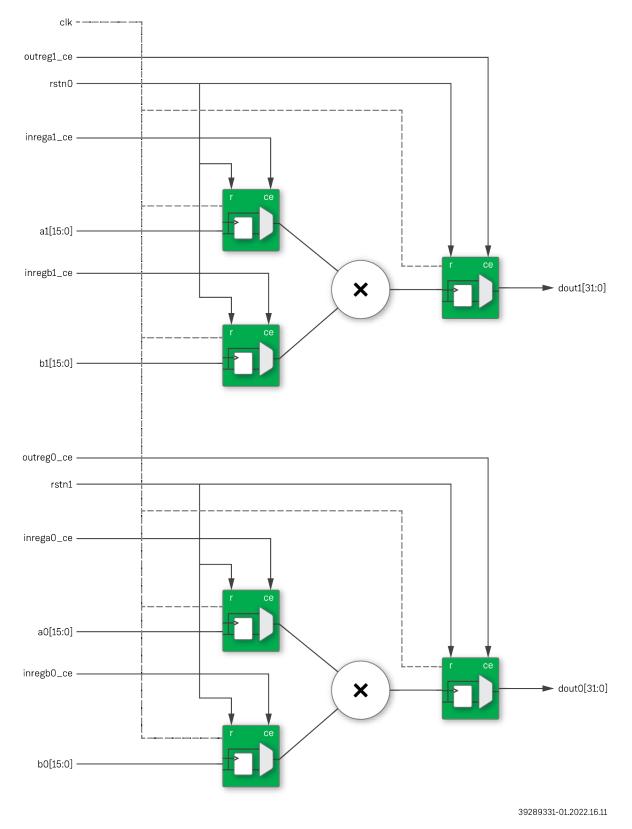

| MLP72_INT16_MULT_2X                    |     |

| Parameters                             | 232 |

| Ports                                  | 234 |

| Timing Diagrams                        |     |

| Inference                              | 236 |

| Instantiation Template                 | 238 |

| Integer Library                        |     |

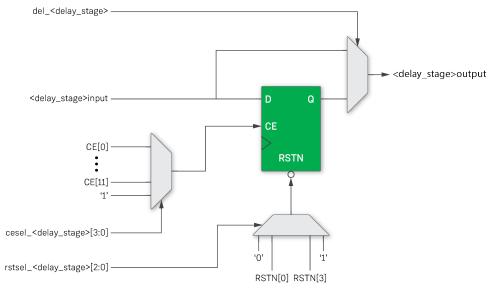

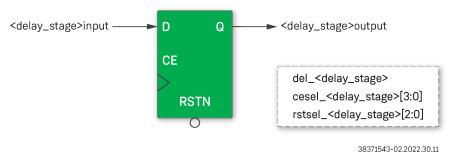

| MLP Registers                          | 239 |

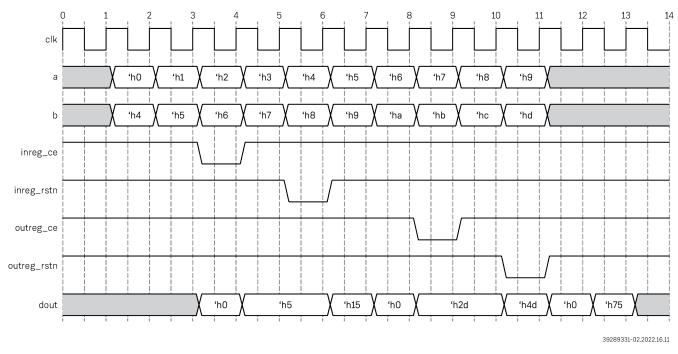

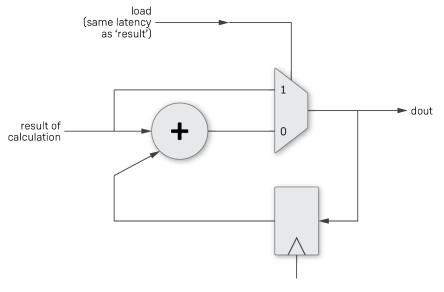

| Accumulation                           | 240 |

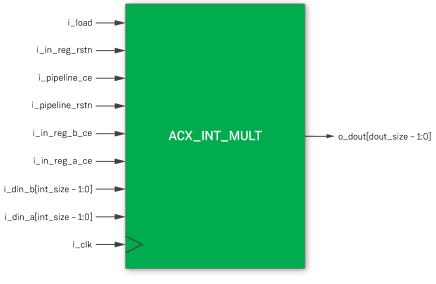

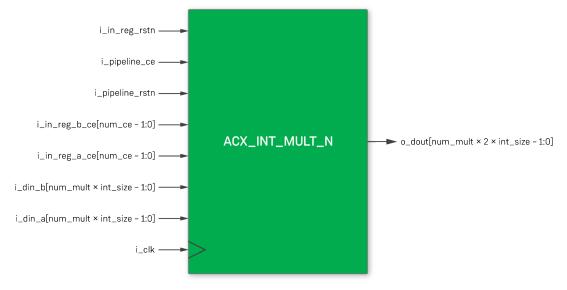

| ACX_INT_MULT                           | 241 |

| ACX_INT_MULT_N                         | 247 |

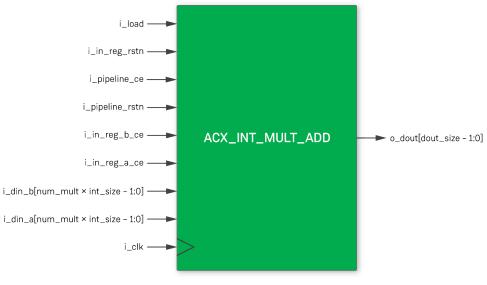

| ACX_INT_MULT_ADD                       | 253 |

| Floating-Point Library                 |     |

| Introduction                           |     |

| MLP Registers                          | 259 |

| Accumulation                           |     |

| Floating-Point Format                  | 260 |

| Output Status                          | 261 |

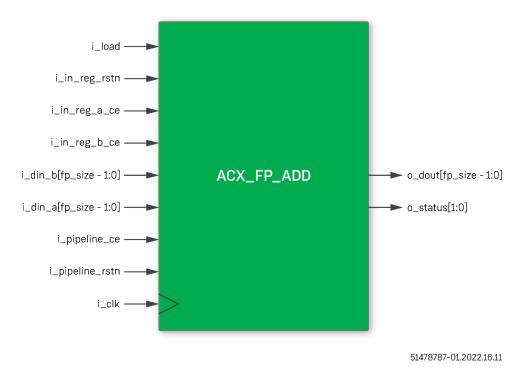

| ACX_FP_ADD                             | 262 |

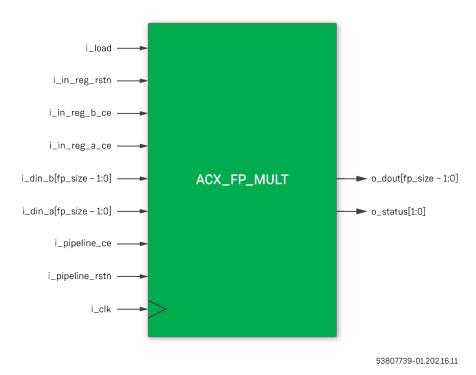

| ACX_FP_MULT                                                           | 267 |

|-----------------------------------------------------------------------|-----|

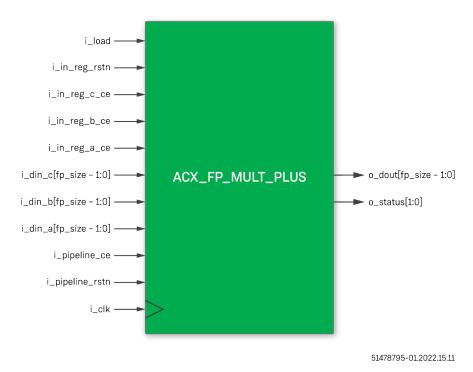

| ACX_FP_MULT_PLUS                                                      | 272 |

| ACX_FP_MULT_2X                                                        | 277 |

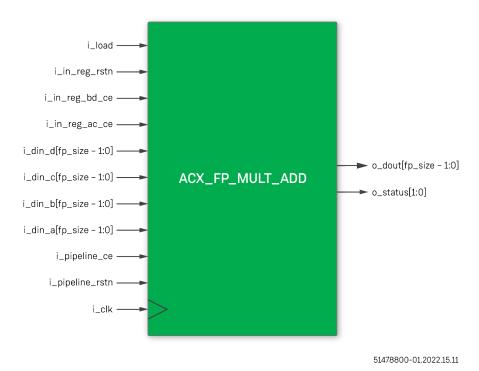

| ACX_FP_MULT_ADD                                                       | 284 |

| Chapter - 6: Memories                                                 | 289 |

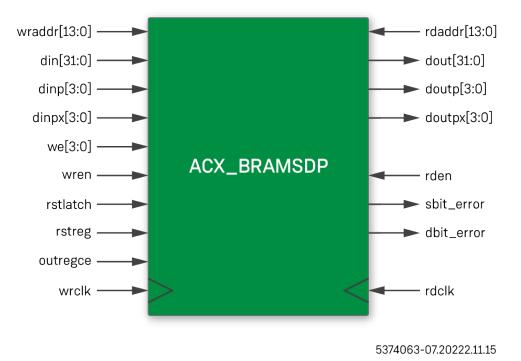

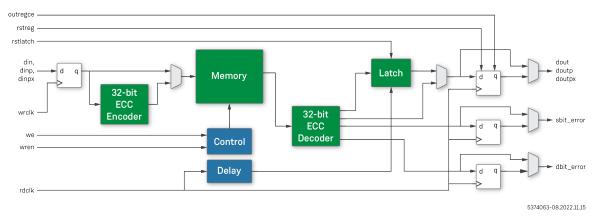

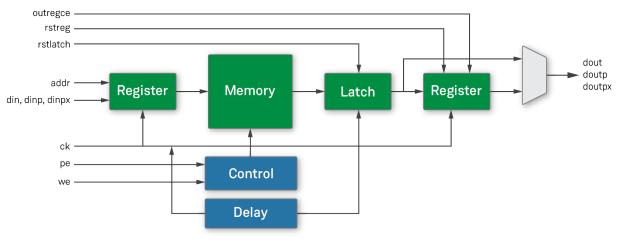

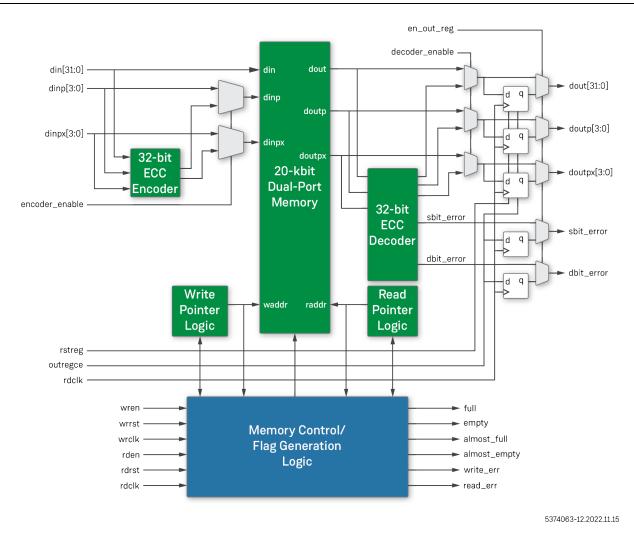

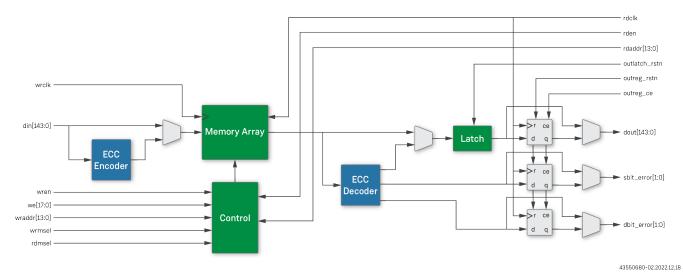

| ACX_BRAMSDP (20-kb Simple Dual-Port Memory with Error Correction)     | 289 |

| Memory Organization and Data Input/Output Pin Assignments             |     |

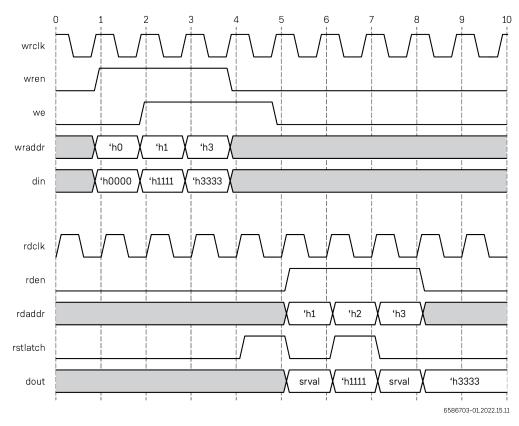

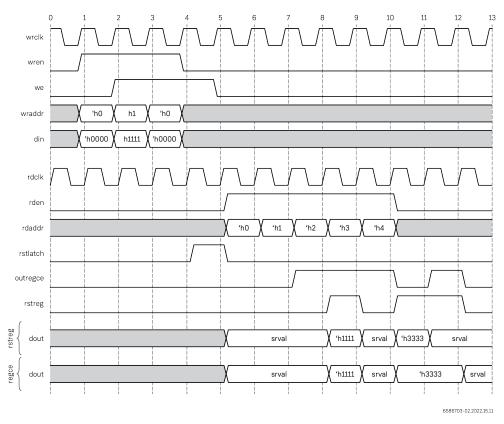

| Read and Write Operations                                             | 298 |

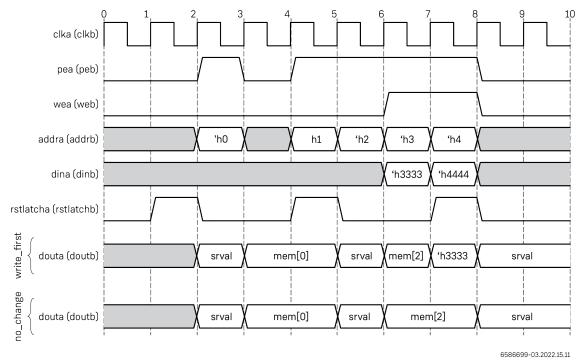

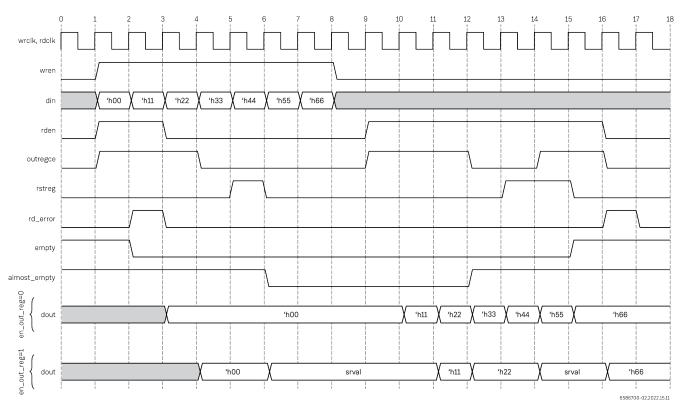

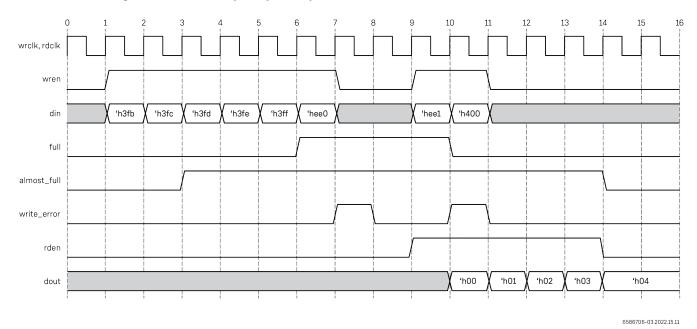

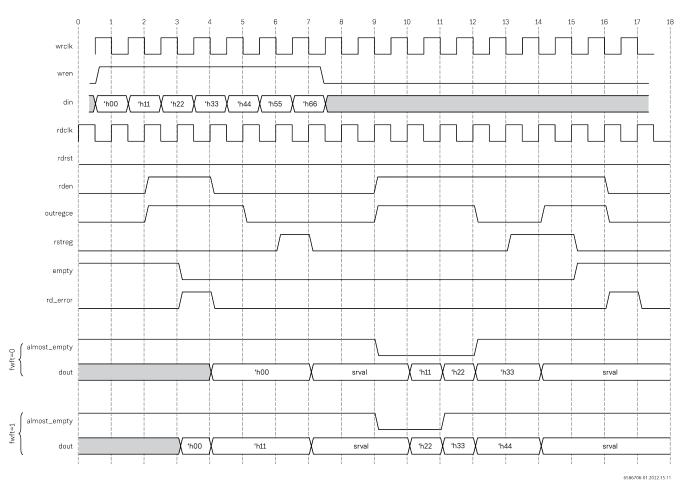

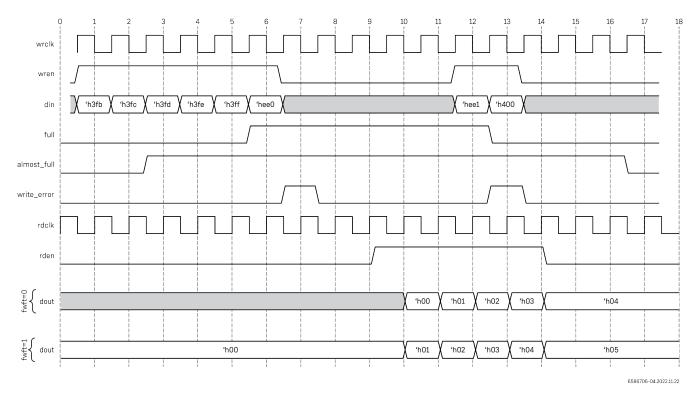

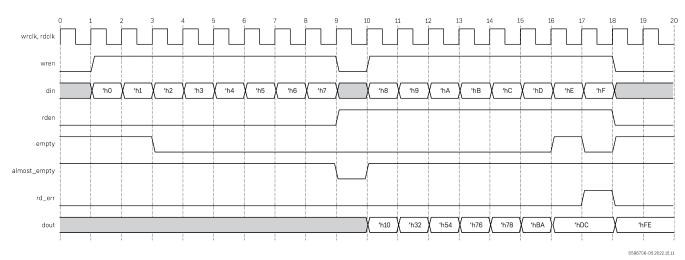

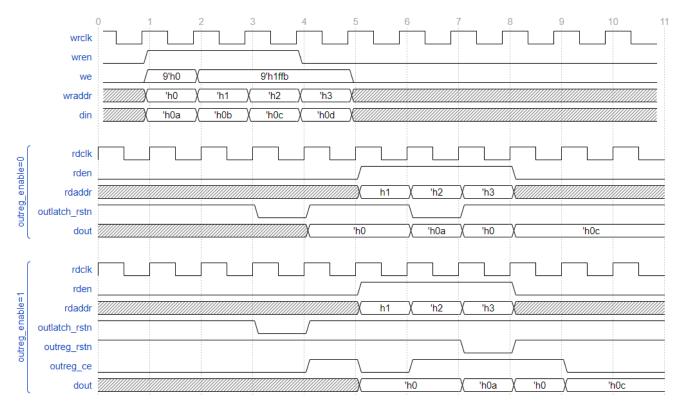

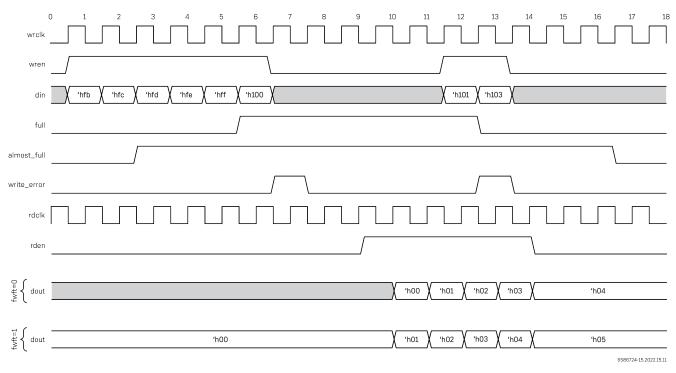

| Timing Diagrams                                                       | 300 |

| Memory Initialization                                                 | 304 |

| ECC Modes of Operation                                                | 307 |

| Using ACX_BRAMSDP as a Read-Only Memory (ROM)                         | 307 |

| Create an Instance                                                    | 308 |

| ACX_BRAMTDP (20-kb True Dual-Port Memory)                             |     |

| Memory Organization and Data I/O Pin Assignments                      |     |

| Read and Write Operations                                             |     |

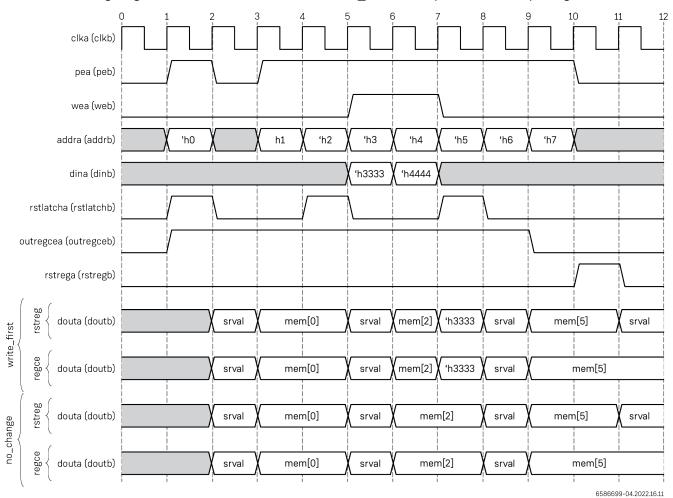

| Timing Diagrams                                                       | 332 |

| Memory Initialization                                                 | 336 |

| Create an Instance                                                    | 338 |

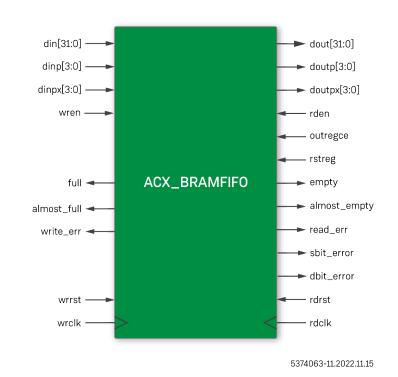

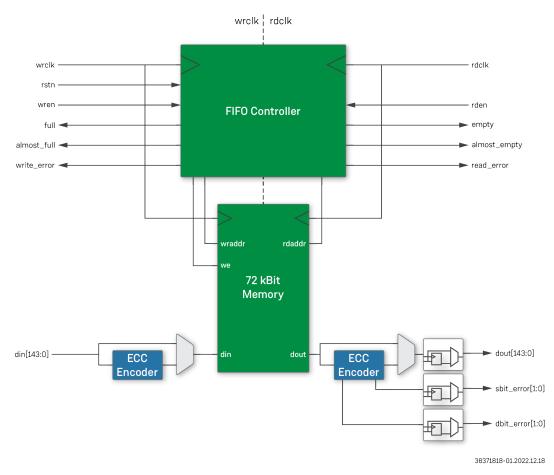

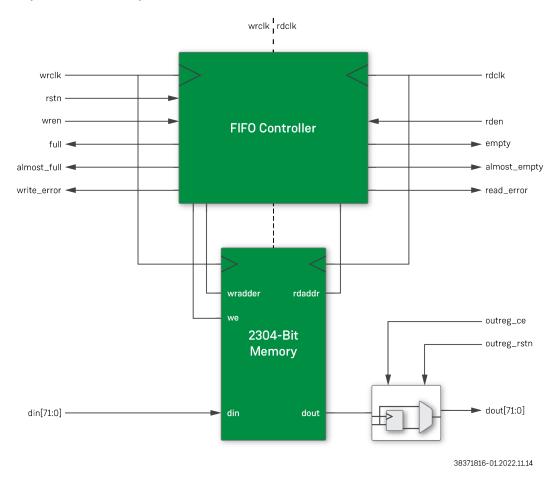

| ACX_BRAMFIFO (20-kb FIFO Memory with Optional Error Correction)       | 350 |

| Memory Organization and Data Pin Assignments                          |     |

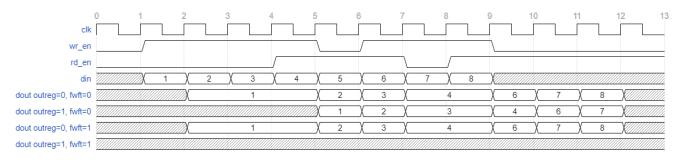

| FIFO Operation                                                        |     |

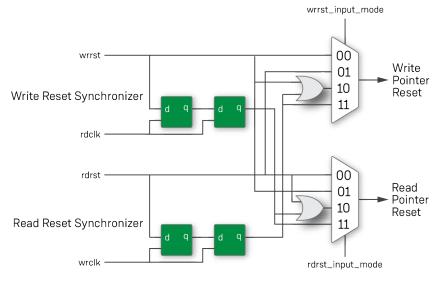

| FIFO Resets                                                           | 380 |

| Error Detection and Correction                                        | 383 |

| Instantiation Template                                                | 385 |

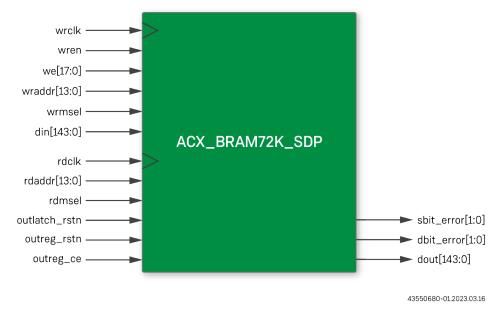

| ACX_BRAM72K_SDP (72-kb Simple Dual-Port Memory with Error Correction) | 387 |

| Parameters                                                            | 389 |

| Ports                                                                 |     |

| Memory Organization and Data Input/Output Pin Assignments             | 393 |

| Read and Write Operations                                             | 396 |

| Timing Diagrams                                                       | 398 |

| Memory Initialization                                                 | 399 |

| ECC Modes of Operation                                                | 401 |

| Using ACX_BRAM72K_SDP as a Read-Only Memory (ROM)                     | 405 |

| Advanced Modes                                                        | 405 |

| Inference                                                             | 407 |

| Instantiation Template                                                | 411 |

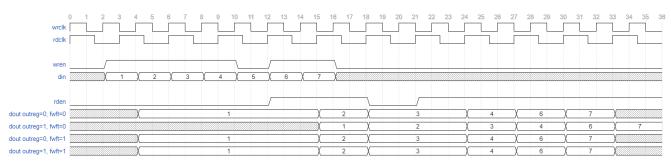

| ACX_BRAM72K_FIFO (72-kb FIFO Memory with Optional Error Correction) |     |

|---------------------------------------------------------------------|-----|

| Parameters                                                          |     |

| Read and Write Operations                                           |     |

| Inference                                                           |     |

| Instantiation Template                                              | 421 |

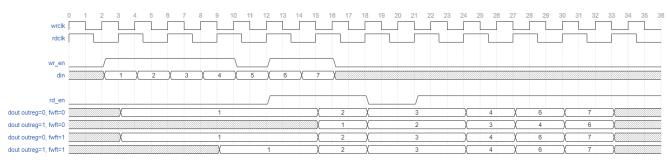

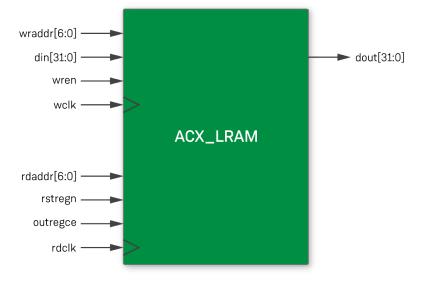

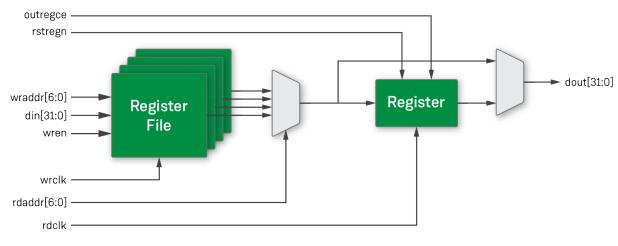

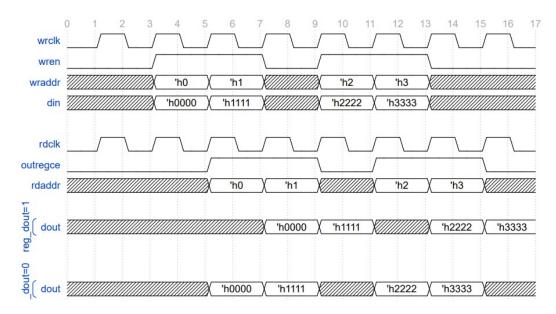

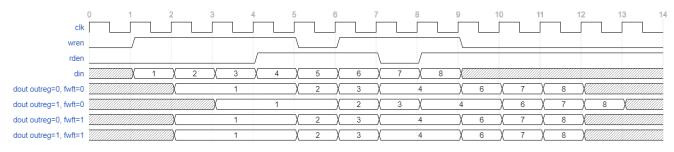

| ACX_LRAM (4096-bit (128x32) Simple-Dual-Port Memory)                | 424 |

| Simultaneous Memory Operations                                      |     |

| Timing Diagram                                                      |     |

| ACX_LRAM Memory Initialization                                      |     |

| Using ACX_LRAM as a Read-Only Memory (ROM)                          |     |

| Create an Instance                                                  |     |

| ACX_LRAMFIFO (LRAM-Based 128-Word FIFO Memory)                      |     |

| Parameters                                                          |     |

|                                                                     |     |

| ACX_LRAM2K_FIFO Parameters                                          |     |

| Ports                                                               |     |

| Read and Write Operations                                           |     |

|                                                                     |     |

| Instantiation Templates                                             |     |

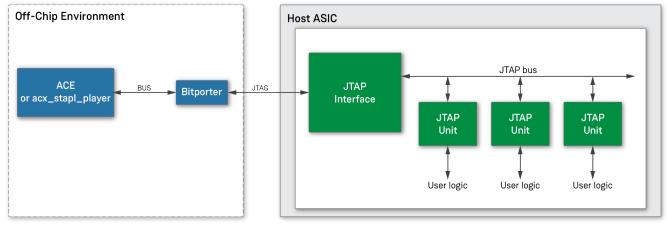

| Chapter - 7: JTAG TAP Controller Functions                          | 457 |

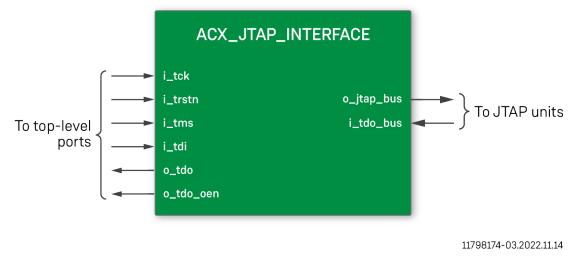

| ACX_JTAP_INTERFACE                                                  |     |

| Ports                                                               |     |

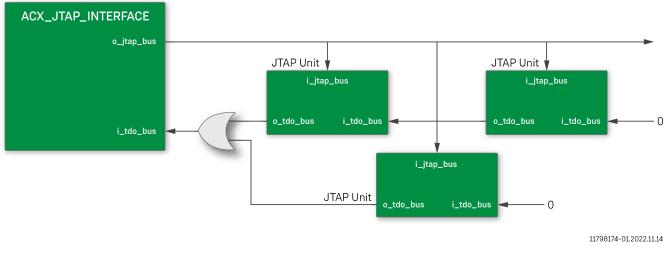

| Connection to the JTAP Bus                                          |     |

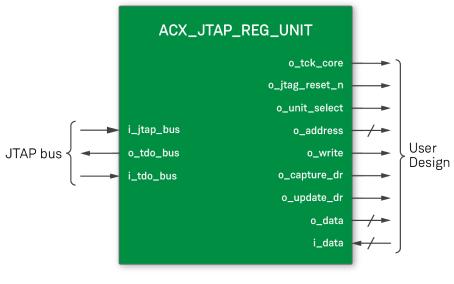

| ACX_JTAP_REG_UNIT                                                   | 462 |

| Parameters                                                          | 462 |

| Ports                                                               | 463 |

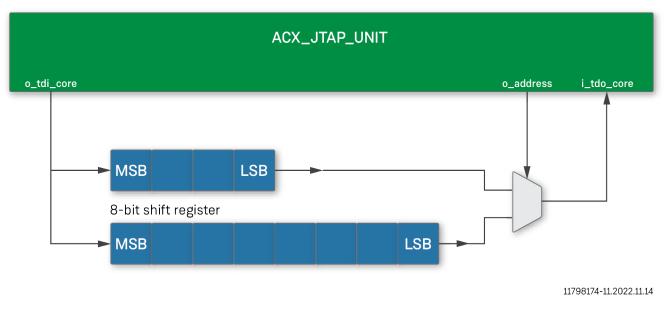

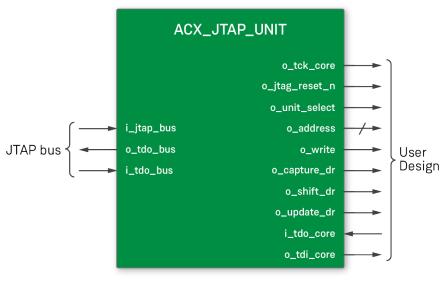

| ACX_JTAP_UNIT                                                       |     |

| Parameters                                                          | 466 |

| Ports                                                               | 467 |

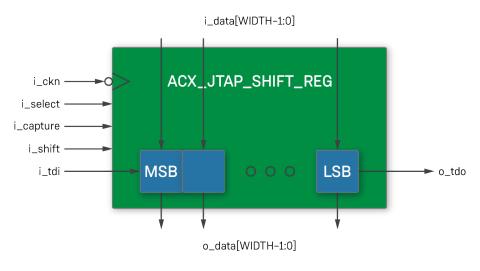

| ACX_JTAP_SHIFT_REG                                                  | 469 |

| Parameters                                                          | 469 |

| Ports                                                               | 470 |

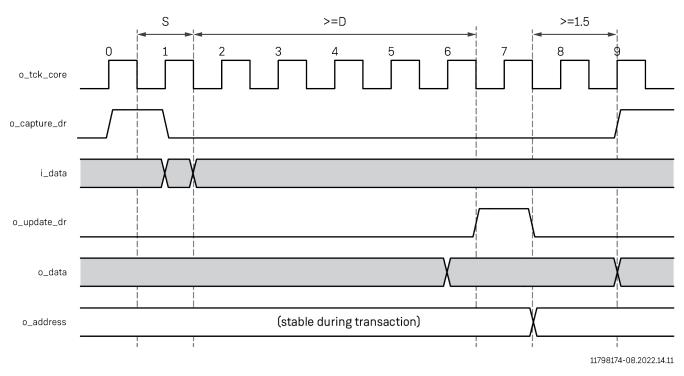

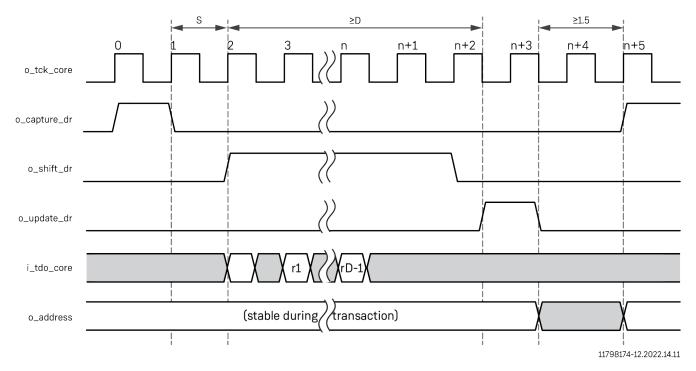

| Communication                                                       |     |

|     | JTAG Reset     | 472 |

|-----|----------------|-----|

|     | Address Action | 472 |

|     | Data Action    | 473 |

| Rev | ision History  | 474 |

# Chapter - 1: Introduction

The Achronix Speedcore component library lists the programmable fabric silicon elements which may be instantiated into a user design. These components provide access to low-level fabric primitives or, in some cases, macros which configure complex elements into advanced functions. Each entry describes the operation of the component as well as any parameters that must be initialized. Verilog and VHDL templates are also provided to aide in the implementation of user designs.

The Speedcore family includes multiple devices which not only have a different quantity of logic for each device but also different components, primarily, but not limited to, memory and arithmetic. To better understand which components a particular Speedcore device has, consult with the Speedcore Device Catalog which lists all available devices and contains tables of available resources for each core.

This guide contains the following sections:

- Speedcore Fabric Architecture (see page 11)

- Speedcore Logic Functions (see page 84)

- Speedcore Clock Functions (see page 90)

- Arithmetic and DSP Functions (see page 99)

- Memories (see page 289)

- JTAG TAP Controller Functions (see page 457)

- Speedcore Component Library User Guide Revision History (see page 474)

# ACX\_ Prefix

All Achronix silicon components start with ACX\_ as their formal name. Therefore, when directly instantiating any component, the ACX\_xxx name must be used. This prefix provides protection against inadvertently instantiating one of the Synplify Pro built-in primitives (primarily DFF and LUT), and distinguishes Achronix silicon components from any other library components. In addition the ACX\_xxx wrapper exposes only the parameters and ports needed/available for a user configuration. It allows for silicon only, or test only, ports and parameters to be masked off, reducing the scope for error when directly instantiating.

When viewing Synplify Pro resource utilization reports, Synplify Pro may list multiple forms of the same component; e.g., ACX\_BRAM72K and BRAM72K. The former indicates a directly instantiated component using the required ACX\_ prefix. The latter indicates an inferred component created by Synplify Pro. Both forms of the component are identical in function; the differences are only in the instantiation level. The total number of silicon components required will be the sum of these instances.

# Chapter - 2: Fabric Architecture

# Introduction

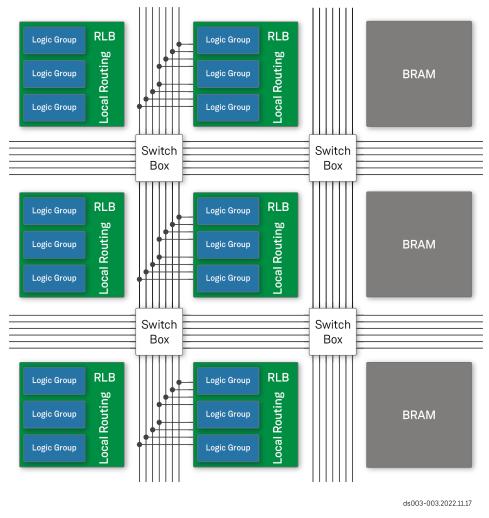

The Speedcore fabric architecture floorplan consists of 6-input LUTs, each with two flops, arranged as logic groups within a reconfigurable logic block (RLB6). The RLB6s are arranged in a grid, interleaved with columns of memory and arithmetic blocks. The block functions are connected by a uniform global interconnect, which enables the routing of signals between core elements. Switch boxes make the connection points between vertical and horizontal routing tracks. Inputs to and outputs from each of the functions connect to the global interconnect.

This floorplan of functional blocks and global interconnects is shown in the following figure.

Figure 1: Speedcore Fabric Floorplan

The fabric logic capabilities and functions are defined by the structure of the RLB6.

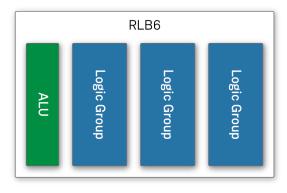

# RLB6 for Gen4 Speedcore eFPGAs

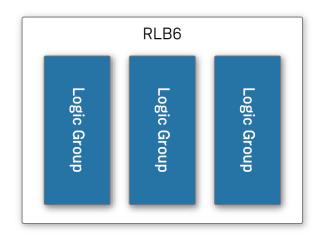

The 6-input LUT-based reconfigurable logic block (RLB6) is composed of three parallel logic groups as shown in the following diagram.

34015316-01.2023.03.16

#### Figure 2: RLB6 Block Diagram

Each logic group in a Gen4 RLB6 contains four 6-input look-up-tables (LUT6), each with two optional registers and an 8-bit fast arithmetic logic unit (ALU8) to implement logic functionality. Each logic group receives a carry-in input from the corresponding logic group in the RLB6 to the north and can propagate a carry-out output to the corresponding logic group in the RLB6 to the south.

The following table provides information on the resource counts inside an RLB6 for Gen4.

#### Table 1: RLB6 Gen4 Resource Counts

| RLB6 Resource | Count |

|---------------|-------|

| Logic Groups  | 3     |

| LUT6          | 12    |

| Registers     | 24    |

| 8-bit ALU8    | 3     |

The following features are available using the resources in the RLB:

- 8-bit ALU for adders, counters, and comparators

- 8-to-1 MUX with single-level delay (can be inferred)

- Support for LUT chaining within the same RLB and between RLBs

- · Dedicated connections for high-efficiency shift registers

- Multiplier LUT (MLUT) mode for efficient multipliers (for Speedster7t devices only)

- · Ability to fan-out a clock enable or reset signal to multiple tiles without using general routing resources

- 6-input LUT configurable to function as two 5-input LUTs using shared inputs and two outputs

- Support for combining two 6-input LUTs with a dynamic select to provide 7-input LUT functionality

The following figure provides a simplified view of the circuitry inside a single logic group.

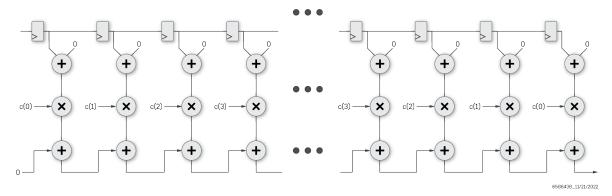

# Routing Between RLB6s

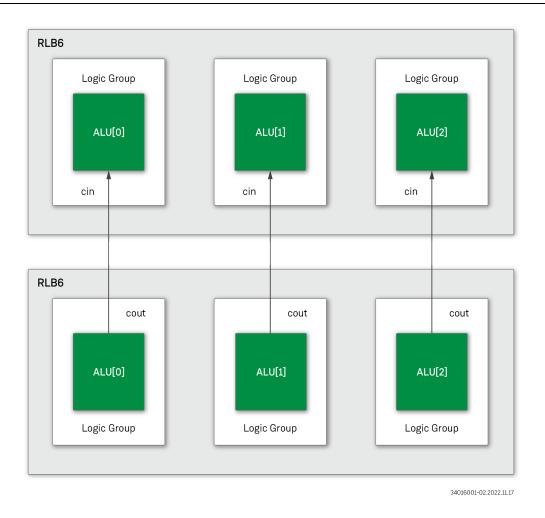

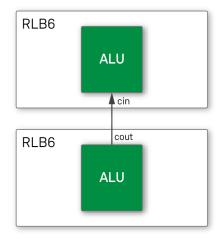

There are special considerations when routing ALU carry chains and shift registers. The Achronix Gen4 fabric has hard-wired connections on the signals <code>carry\_in/carry\_out</code> of each ALU. As previously mentioned, each logic group routes to the corresponding logic group in the RLB6 above or below. In other words, the ALU <code>carry\_in/carry\_out</code> does not route to the next ALU within the same RLB, but rather the same logic group of the next RLB6. The following figure shows the <code>carry\_in/carry\_out</code> routing of an ALU.

# Figure 4: ALU Carry Chain Routing

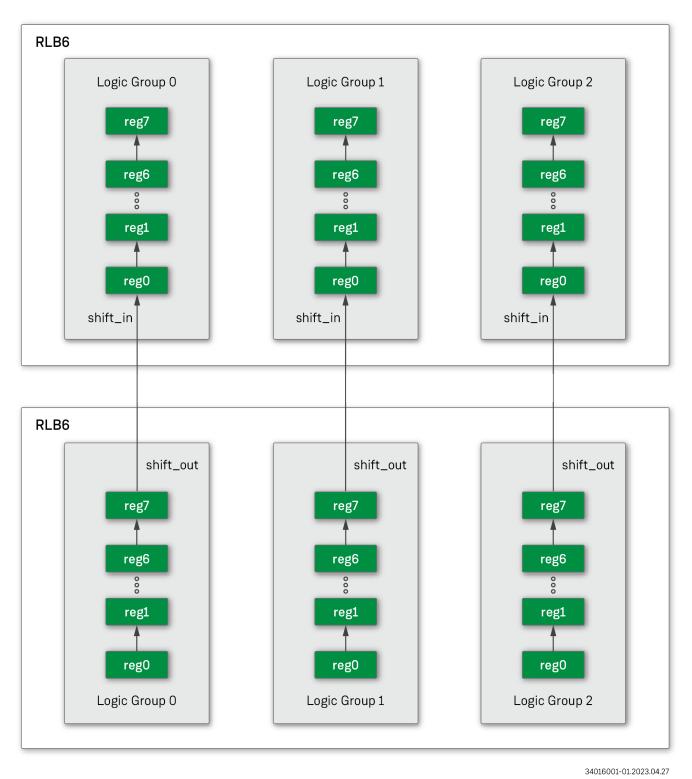

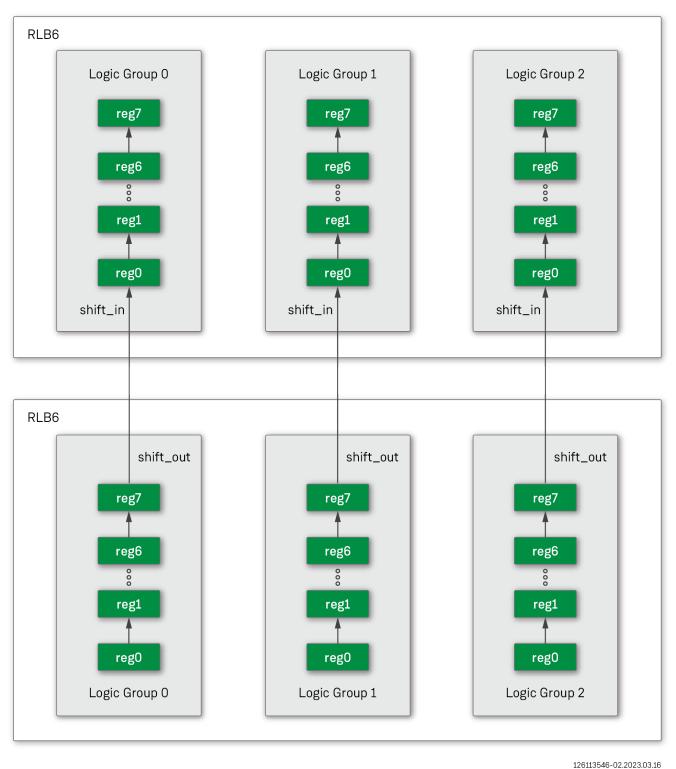

As true for carry\_in/carry\_out, the same is true for the signals <code>shift\_in/shift\_out</code> in the registers of a logic group. When creating a shift register, the registers within a logic group route to each other, but the <code>shift\_in/shift\_out</code> of each logic group routes to the same logic group in the next RLB6.

The following figure shows details of the routing in the Gen4 fabric.

Figure 5: Shift Register Routing

# **RLB6** Detail

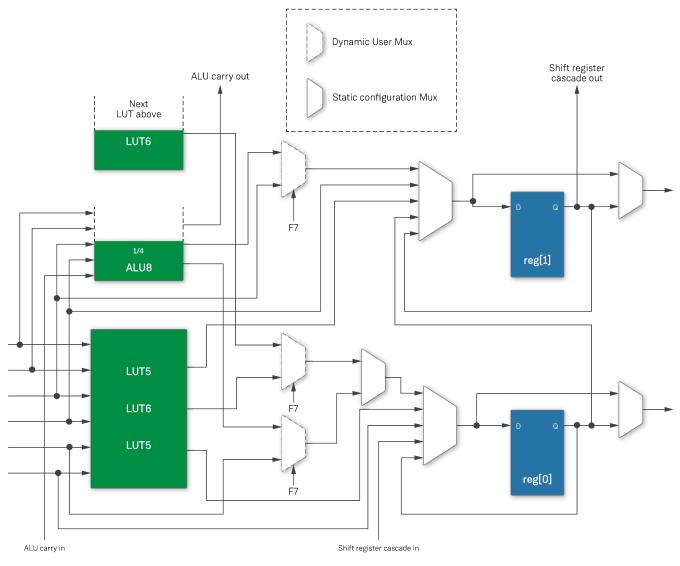

Within each RLB6 are the three logic groups, each containing four 6-input LUTs (LUT6s), one ALU8, and eight registers. The logic group has ALU and flip-flop cascade paths between its associated RLB6 logic groups. The following figure shows the routing detail of one fourth of a logic group (one LUT6 and two registers).

52003566-02.2022.11.17

# Figure 6: One-Fourth of a Logic Group (Connection Detail)

The diagram shows the following:

- Certain LUT6 inputs are shared with ALU8 inputs

- The LUT6 can be operated as dual 5-input LUTs (LUT5s)

- The input to each register can be selected from the following:

- Local LUT6 output, or the LUT6 above

- LUT5 output

- ALU8 output (sum output)

- LUT6 input (load input)

- Register output (feedback path)

- Register cascade from register below (shift register cascade)

- Some of the above inputs are statically configured by the bitstream, and other inputs can be dynamically selected. The dynamic selection is performed by the F7 signal which is an input to the logic group. The F7 allows for dynamic selection of the following:

- Lower register first mux: ALU sum output, or register load input (shared with LUT6 input)

- Lower register second mux: local LUT6 output or LUT6 above output

- Upper register ALU sum output, or register load input (shared with LUT6 input)

# **Mutually Exclusive Operations**

The shared connections result in a number of mutually exclusive operations that can be achieved by a single logic group. When using all the LUT6s, the ALU8 is not available, nor is register load.

When using the ALU8:

- When ALU8 is used for A[7:0]+B[7:0]+Cin, one independent LUT6 is available.

- When ALU8 is used for A[7:0]+B[7:0], one independent LUT6 and one independent LUT2 is available.

- When ALU8 is used for A[7:0]+'Const', two independent LUT6 and one independent LUT4 are available.

- When ALU8 is used for A[3:0]+B[3:0]+Cin, two independent LUT4 are available.

When using dynamic register load, or the ALU8 sum, no LUT6s are available. When using static register load, four independent LUT4 are available.

When using F7 mux function, forming an 8:1 multiplexer (MUX8), no LUT6 or ALU8 are available.

# **Control Signals**

Within a logic group there are eight registers, numbered reg[7:0]. These registers share control signals with each logic group having two clock, clock enable and reset inputs. The control signals are subsequently divided between the registers, with one set for registers[3:0], and the other set for registers[7:4].

#### Note

If or designs with high utilization, ensure that as many registers as possible have common control signal sets to allow for optimum packing of the registers into logic groups.

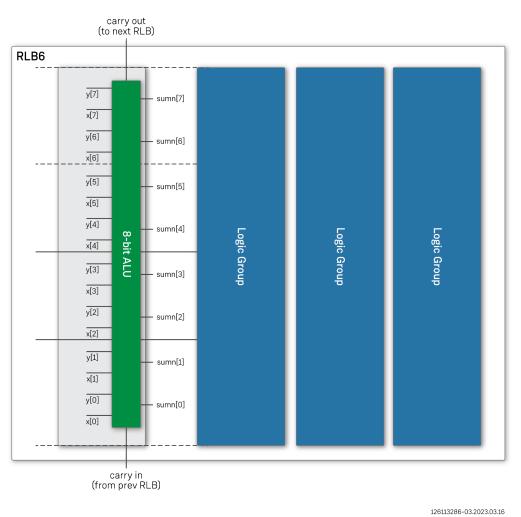

# RLB6 for Gen5 Speedcore eFPGAs

The 6-input LUT-based reconfigurable logic block (RLB6) is composed of three parallel logic groups as shown in the following diagram.

126113286-01.2023.03.16

#### Figure 7: RLB6 Block Diagram

Each logic group in a Gen5 RLB6 contains four 6-input lookup tables (LUT6), each with two optional registers to implement logic functionality. Additionally, each Gen5 RLB6 includes a single 8-bit fast arithmetic logic unit (ALU8). Each ALU8 receives a carry-in input from the corresponding ALU8 in the RLB6 to the north and can propagate a carry-out output to the corresponding ALU8 in the RLB6 to the south.

The following table provides details on the resource counts inside an RLB6 for Gen5.

#### Table 2: RLB6 Gen5 Resource Counts

| RLB6 Resource | Count |

|---------------|-------|

| Logic Groups  | 3     |

| LUT6          | 12    |

| Registers     | 24    |

| 8-bit ALU8    | 1     |

The following features are available using the resources in the RLB:

- · 8-bit ALU for adders, counters, and comparators

- 8-to-1 MUX with single-level delay (can be inferred)

- Support for LUT chaining within the same RLB and between RLBs

- Dedicated connections for high-efficiency shift registers

- Ability to fan-out a clock enable or reset signal to multiple tiles without using general routing resources

- 6-input LUT configurable to function as two 5-input LUTs using shared inputs and two outputs

- Support for combining two 6-input LUTs with a dynamic select to provide 7-input LUT functionality

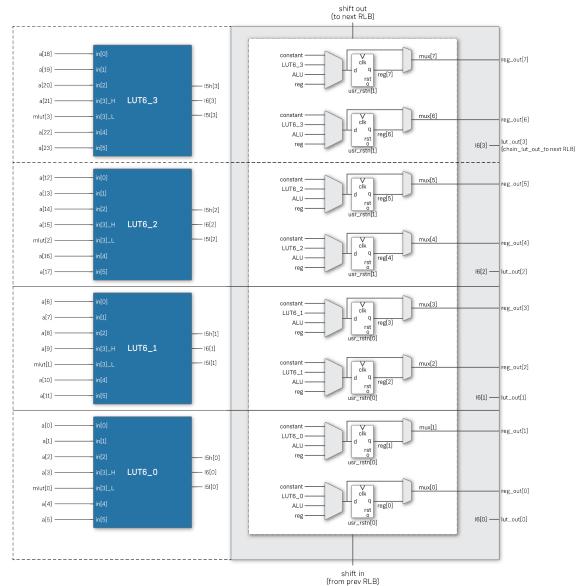

The following figure provides a simplified view of the circuitry inside a single logic group.

(nom previncib

126113286-02.2023.03.16

Figure 8: Logic Group Details

The following figure provides a simplified view of the logic groups with circuitry for the ALU inside the RLB6.

Figure 9: Logic Groups With ALU Details

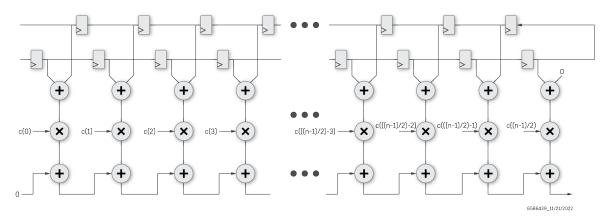

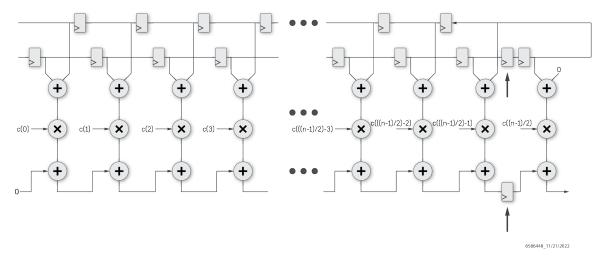

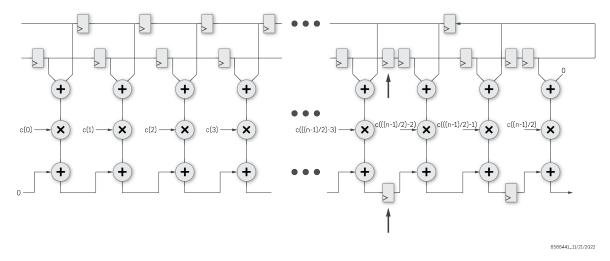

# Routing Between RLB6s

There are special considerations when routing ALU carry chains and shift registers. The Achronix Gen5 fabric has hard-wired connections on the signals <code>carry\_in/carry\_out</code> of each ALU. As previously mentioned, each logic group routes to the corresponding logic group in the RLB6 above or below, and the same is true for the ALUs. In other words, the ALU <code>carry\_in/carry\_out</code> does not route to the next ALU to the east/west of the RLB6, but rather the ALU of the next RLB6 to the north.

The following figure shows the carry\_in/carry\_out routing of an ALU.

126113546-01.2023.03.16

Figure 10: ALU Carry Chain Routing

As for carry\_in/carry\_out, the same is true for the signals <code>shift\_in/shift\_out</code> in the registers of a logic group. When creating a shift register, the registers within a logic group route to each other, but the <code>shift\_in /shift\_out</code> of each logic group routes to the same logic group in the next RLB6.

The following figure shows details of the routing in the Gen5 fabric.

126113546-02.2023.0

Figure 11: Shift Register Routing

# Lookup Table (LUT) Functions

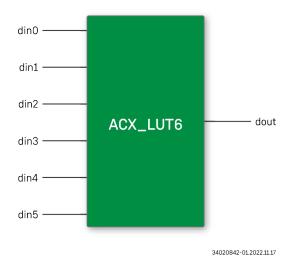

# Six-Input Lookup Table (ACX\_LUT6)

ACX\_LUT6 implements a six-input lookup table with data inputs (din0-din5) and data output (dout), whose function is defined by the 64-bit parameter lut\_function.

Figure 12: Logic Symbol

# Parameters

### **Table 3:** Parameters

| Parameter    | Defined Values           | Default<br>Value | Description                                                                                                                  |

|--------------|--------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------|

| lut_function | 64-bit hexadecimal value | 64′h0            | The lut_function parameter defines the value on the dout output of the LUT6 as detailed in the function table (see page 24). |

# Ports

### **Table 4:** Pin Descriptions

| Name      | Туре   | Description                                                                                                                          |

|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| din0-din5 | Input  | Data inputs.                                                                                                                         |

| dout      | Output | Data output. The value on dout is the part of the lut_function parameter indexed by the inputs {din5, din4, din3, din2, din1, din0}. |

# Function

# Table 5: Function Table

| din5 | din4 | din3 | din2 | din1 | din0 | dout             |

|------|------|------|------|------|------|------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | lut_function[0]  |

| 0    | 0    | 0    | 0    | 0    | 1    | lut_function[1]  |

| 0    | 0    | 0    | 0    | 1    | 0    | lut_function[2]  |

| 0    | 0    | 0    | 0    | 1    | 1    | lut_function[3]  |

| 0    | 0    | 0    | 1    | 0    | 0    | lut_function[4]  |

|      |      |      |      |      |      |                  |

| 1    | 1    | 1    | 1    | 0    | 1    | lut_function[61] |

| 1    | 1    | 1    | 1    | 1    | 0    | lut_function[62] |

| 1    | 1    | 1    | 1    | 1    | 1    | lut_function[63] |

# Instantiation Templates

# Verilog

```

ACX_LUT6

#(

.lut_function

(64'h012345678abcdef)

) instance_name (

.dout

(user_out),

.din0

(user_in0),

.din1

(user_in1),

.din2

(user_in2),

.din3

(user_in3),

.din4

(user_in4),

.din5

(user_in5)

);

```

### VHDL

```

-- VHDL Component template for ACX_LUT6

component ACX_LUT6 is

generic (

lut_function : std_logic_vector( 63 downto 0) := X"0000000000000000"

);

port (

: in std_logic;

din0

din1

: in std_logic;

din2

: in std_logic;

din3

: in std_logic;

: in std_logic;

din4

: in std_logic;

din5

: out std_logic

dout

);

end component ACX_LUT6

-- VHDL Instantiation template for ACX_LUT6

instance_name : ACX_LUT6

generic map (

lut_function => lut_function

)

port map (

din0

=> user_din0,

din1

=> user_din1,

din2

=> user_din2,

din3

=> user_din3,

din4

=> user_din4,

din5

=> user_din5,

dout

=> user_dout

);

```

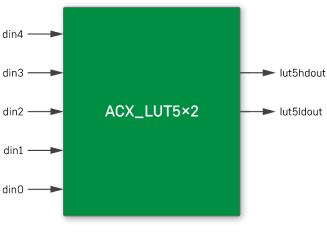

# Dual Five-Input Lookup Table (ACX\_LUT5x2)

ACX\_LUT5x2 implements dual LUT5 lookup tables with data inputs (din0-din5) and data output (lut5ldout and lut5hdout). Each of the outputs is determined by a function which is defined by the 64-bit parameter lut\_function.

34020842-02.2022.11.17

Figure 13: Dual LUT5 Lookup Tables

# Parameters

### Table 6: Parameters

| Parameter    | Defined Values           | Default<br>Value | Description                                                                                                                                         |

|--------------|--------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| lut_function | 64-bit hexadecimal value | 64′h0            | The lut_function parameter defines the value on both the lut5ldout and lut5hdout outputs of the LUT5x2 as detailed in function table (see page 27). |

# Ports

### **Table 7:** Pin Descriptions

| Name      | Туре   | Description                                                                                                                               |  |  |  |  |  |

|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| din0-din4 | Input  | Data inputs.                                                                                                                              |  |  |  |  |  |

| lut5hdout | Output | Data output. The value on lut5hdout is the part of the lut_function parameter indexed by the inputs {1'b1, din4, din3, din2, din1, din0}. |  |  |  |  |  |

| lut5ldout | Output | Data output. The value on lut5ldout is the part of the lut_function parameter indexed by the inputs {1'b0, din4, din3, din2, din1, din0}. |  |  |  |  |  |

# Functions

# Table 8: 1ut51dout Function Table

| 1'b0 | din4 | din3 | din2 | din1 | din0 | dout             |

|------|------|------|------|------|------|------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | lut_function[0]  |

| 0    | 0    | 0    | 0    | 0    | 1    | lut_function[1]  |

| 0    | 0    | 0    | 0    | 1    | 0    | lut_function[2]  |

| 0    | 0    | 0    | 0    | 1    | 1    | lut_function[3]  |

| 0    | 0    | 0    | 1    | 0    | 0    | lut_function[4]  |

|      |      |      |      |      |      |                  |

| 0    | 1    | 1    | 1    | 0    | 1    | lut_function[29] |

| 0    | 1    | 1    | 1    | 1    | 0    | lut_function[30] |

| 0    | 1    | 1    | 1    | 1    | 1    | lut_function[31] |

# Table 9: 1ut5hdout Function Table

| 1'b1 | din4 | din3 | din2 | din1 | din0 | dout             |

|------|------|------|------|------|------|------------------|

| 1    | 0    | 0    | 0    | 0    | 0    | lut_function[32] |

| 1    | 0    | 0    | 0    | 0    | 1    | lut_function[33] |

| 1    | 0    | 0    | 0    | 1    | 0    | lut_function[34] |

| 1    | 0    | 0    | 0    | 1    | 1    | lut_function[35] |

| 1    | 0    | 0    | 1    | 0    | 0    | lut_function[36] |

|      |      |      |      |      |      |                  |

| 1    | 1    | 1    | 1    | 0    | 1    | lut_function[61] |

| 1    | 1    | 1    | 1    | 1    | 0    | lut_function[62] |

| 1    | 1    | 1    | 1    | 1    | 1    | lut_function[63] |

# **Instantiation Templates**

#### Verilog

```

// Verilog template for ACX_LUT5x2

ACX_LUT5x2 #(

(lut_function)

.lut_function

) instance_name (

.din0

(user_din0),

.din1

(user_din1),

.din2

(user_din2),

.din3

(user_din3),

.din4

(user_din4),

.lut5ldout

(user_lut5ldout),

.lut5hdout

(user_lut5hdout)

);

```

#### VHDL

```

-- VHDL Component template for ACX_LUT5x2

component ACX_LUT5x2 is

generic (

lut_function : std_logic_vector(63 downto 0) := X"00000000000000000"

);

port (

: in std logic;

din0

: in std_logic;

dinl

din2

: in std_logic;

: in std_logic;

din3

: in std_logic;

din4

: out std_logic;

lut5ldout

: out std_logic

lut5hdout

);

end component ACX_LUT5x2

-- VHDL Instantiation template for ACX_LUT5x2

instance_name : ACX_LUT5x2

generic map (

=> lut_function

lut_function

)

port map (

din0

=> user_din0,

dinl

=> user_din1,

din2

=> user_din2,

din3

=> user_din3,

din4

=> user_din4,

=> user_lut5ldout,

lut5ldout

lut5hdout

=> user_lut5hdout

);

```

# Speedcore Registers

# Naming Convention

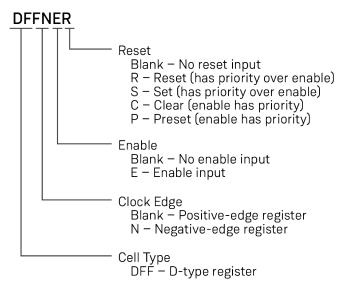

These macros are named based upon their characteristics and behavior. In each case, the name begins with DFF for D-type flip-flop. In addition to DFF, each has one or more modifiers which indicate its unique properties.

4227813-01.2022.17.11

Figure 14: Register Naming Convention

# **Register Primitives**

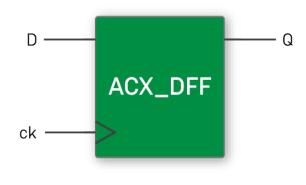

# ACX\_DFF (Positive Clock Edge D-Type Register)

5374051-01.2022.11.17

#### Figure 15: Positive Clock Edge D-Type Register

ACX\_DFF is a single D-type register with data input (d) and clock (ck) inputs and data (q) output. The data output is set to the value on the data input upon the next rising edge of the clock.

#### Table 10: Parameters

| Parameter | Defined<br>Values | Default<br>Value | Description                                                                                                                                                             |

|-----------|-------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| init      | 1'b0,1'b1         | 1'b0             | The init parameter defines the initial value of the output of the DFF register. This is the value the register takes upon the initial application of power to the FPGA. |

## Table 11: Pin Descriptions

| Name | Туре   | Description                                                                                                                |  |  |  |  |  |

|------|--------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| d    | Input  | Data input.                                                                                                                |  |  |  |  |  |

| ck   | Input  | Positive-edge clock input.                                                                                                 |  |  |  |  |  |

| đ    | Output | Data output. The value present on the data input is transferred to the ${\bf q}$ output upon the rising edge of the clock. |  |  |  |  |  |

### Table 12: Function Table

| Inp | outs | Output |

|-----|------|--------|

| d   | ck   | P      |

| 0   | 1    | 0      |

| 1 ↑ |      | 1      |

### Instantiation Templates

### Verilog

```

ACX_DFF #(

.init (1'b0)

) instance_name (

.q (user_out),

.d (user_din),

.ck (user_clock)

);

```

### VHDL

```

----- ACHRONIX LIBRARY ------

library speedster7t;

use speedster7t.core.all;

----- DONE ACHRONIX LIBRARY -----

-- Component Instantiation

instance_name : ACX_DFF

generic map (

init => '0'

)

port map (

=> user_out,

=> user_din,

q

d

=> user_clock

ck

);

```

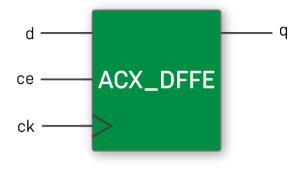

# ACX\_DFFE (Positive Clock Edge D-Type Register With Clock Enable)

5374051-02.2022.11.17

### Figure 16: Positive Clock Edge D-Type Register With Clock Enable

ACX\_DFFE is a single D-type register with data input (d), clock enable (ce), and clock (ck) inputs and data (q) output. The data output is set to the value on the data input upon the next rising edge of the clock if the active-high clock enable input is asserted.

#### Table 13: Parameters

| Parame | ter Defined Values | Description |                                                                                                                                                                          |  |  |

|--------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| init   | 1'b0,1'b1          | 1'b0        | The init parameter defines the initial value of the output of the DFFE register. This is the value the register takes upon the initial application of power to the FPGA. |  |  |

#### Table 14: Pin Descriptions

| Name | Туре   | Description                                                                                                                                                     |  |  |  |  |  |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| d    | Input  | Data input.                                                                                                                                                     |  |  |  |  |  |

| се   | Input  | Active-high clock enable input.                                                                                                                                 |  |  |  |  |  |

| ck   | Input  | Positive-edge clock input.                                                                                                                                      |  |  |  |  |  |

| đ    | Output | Data output. The value present on the data input is transferred to the $\mathbf{q}$ output upon the rising edge of the clock if the clock enable input is high. |  |  |  |  |  |

#### **Table 15:** Function Table

| I  | nput | Output |      |

|----|------|--------|------|

| ce | d    | ck     | P    |

| 0  | Х    | х      | Hold |

| 1  | 0    | 1      | 0    |

| 1  | 1 1  |        | 1    |

#### Instantiation Templates

#### Verilog

```

ACX_DFFE #(

.init (1'b0)

) instance_name (

.q (user_out),

.d (user_din),

.ce (user_clock_enable),

.ck (user_clock)

);

```

## VHDL

```

----- ACHRONIX LIBRARY ------

library speedster7t;

use speedster7t.core.all;

----- DONE ACHRONIX LIBRARY ------

-- Component Instantiation

instance_name : ACX_DFFE

generic map (

init => '0'

)

port map (

=> user_out,

q

d

=> user_din,

ce

=> user_clock_enable,

ck

=> user_clock

);

```

# ACX\_DFFER (Positive Clock Edge D-Type Register With Clock Enable and Asynchronous/Synchronous Reset)

5374051-05.2022.11.17

#### Figure 17: Positive Clock Edge D-Type Register With Clock Enable and Asynchronous/Synchronous Reset

ACX\_DFFER is a single D-type register with data input (d), clock enable (ce), clock (ck), and active-low reset (rn ) inputs and data (q) output. The active-low reset input overrides all other inputs when it is asserted low and sets the data output low. The response of the q output in response to the asserted reset depends on the value of the sr\_assertion parameter and is detailed in See ACX\_DFFER Function Table with sr\_assertion = "unclocked" (see page 35) and See ACX\_DFFER Function Table with sr\_assertion = "clocked" (see page 35). If the reset input is not asserted, the data output is set to the value on the data input upon the next rising edge of the clock if the active-high clock enable input is asserted.

### Table 16: Parameters

| Parameter    | Defined<br>Values         | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------|---------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| init         | 1'b0,1'b1                 | 1'b0             | The init parameter defines the initial value of the output of the DFFER register. This is the value the register takes upon the initial application of power to the FPGA.                                                                                                                                                                                                                                                                                                                                                                         |  |

| sr_assertion | "unclocked",<br>"clocked" | "unclocked"      | The sr_assertion parameter defines the behavior of the output when the rn reset input is asserted. Assigning the sr_assertion to "unclocked" results in an asynchronous assertion of the reset signal, where the q output is set to zero upon assertion of the active-low reset signal. Assigning the sr_assertion to "clocked" results in a synchronous assertion of the reset signal, where the q output is set to zero assertion to "clocked" results in a synchronous assertion of the reset signal, where the next rising edge of the clock. |  |

# Table 17: Pin Descriptions

| Name | Туре   | Description                                                                                                                                                                                                                                                                                        |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d    | Input  | Data input.                                                                                                                                                                                                                                                                                        |

| rn   | Input  | Active-low asynchronous/synchronous reset input. A low on rn sets the q output low independent of the other inputs if the sr_assertion parameter is set to "unclocked". If the sr_assertion parameter is set to "clocked", a low on rn sets the q output low at the next rising edge of the clock. |

| се   | Input  | Active-high clock enable input.                                                                                                                                                                                                                                                                    |

| ck   | Input  | Positive-edge clock input.                                                                                                                                                                                                                                                                         |

| đ    | Output | Data output. The value present on the data input is transferred to the $\mathbf{q}$ output upon the rising edge of the clock if the clock enable input is high and the reset input is high.                                                                                                        |

# Table 18: ACX\_DFFER Function Table With sr\_assertion = "unclocked"

|    | Output |   |    |      |

|----|--------|---|----|------|

| rn | ce     | d | ck | P    |

| 0  | х      | Х | х  | 0    |

| 1  | 0      | х | х  | Hold |

| 1  | 1      | 0 | Î  | 0    |

| 1  | 1      | 1 | Î  | 1    |

### Table 19: ACX\_DFFER Function Table With sr\_assertion = "clocked"

| Inputs |    |   |    | Output |

|--------|----|---|----|--------|

| rn     | ce | d | ck | P      |

| 0      | х  | Х | 1  | 0      |

| 1      | 0  | Х | Х  | Hold   |

| 1      | 1  | 0 | ↑  | 0      |

| 1      | 1  | 1 | 1  | 1      |

### Instantiation Templates

#### Verilog

```

ACX_DFFER #(

.init

(1'b0),

.sr_assertion ("unclocked")

) instance_name (

(user_out),

.q

.d

(user_din),

.rn

(user_reset),

.ce

(user_clock_enable),

.ck

(user_clock)

);

```

#### VHDL

```

----- ACHRONIX LIBRARY ------

library speedster7t;

use speedster7t.core.all;

----- DONE ACHRONIX LIBRARY ------

-- Component Instantiation

instance_name : ACX_DFFER

generic map (

init

=> '0',

sr_assertion => "unclocked")

port map (

=> user_out,

q

d

=> user_din,

=> user_reset,

rn

ce

=> user_clock_enable,

ck

=> user_clock

);

```

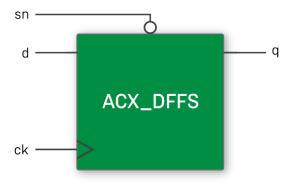

# ACX\_DFFES (Positive Clock Edge D-Type Register With Clock Enable and Asynchronous/Synchronous Set)

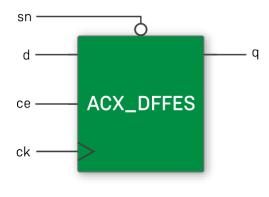

5374051-06.2022.11.17

### Figure 18: Positive Clock Edge D-Type Register With Clock Enable and Asynchronous/Synchronous Set

ACX\_DFFES is a single D-type register with data input (d), clock enable (ce), clock (ck), and active-low set (sn) inputs and data (q) output. The active-low set input overrides all other inputs when it is asserted low and sets the data output high. The response of the q output in response to the asserted set depends on the value of the sr\_assertion parameter and is detailed in Table: ACX\_DFFES Function Table with sr\_assertion = "unclocked" (see page 35) and Table: ACX\_DFFES Function Table with sr\_assertion = "clocked" (see page 35). If the set input is not asserted, the data output is set to the value on the data input upon the next rising edge of the clock if the active-high clock enable input is asserted.

# Table 20: Parameters

| Parameter    | Defined<br>Values         | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|---------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| init         | 1'b0,1'b1                 | 1'b1             | The init parameter defines the initial value of the output of the DFFES register. This is the value the register takes upon the initial application of power to the FPGA.                                                                                                                                                                                                                                                                                  |

| sr_assertion | "unclocked",<br>"clocked" | "unclocked"      | The sr_assertion parameter defines the behavior of the output when the sn set input is asserted. Assigning the sr_assertion to "unclocked" results in an asychronous assertion of the reset signal, where the q output is set to one upon assertion of the active-low reset signal. Assigning the sr_assertion to "clocked" results in a synchronous assertion of the reset signal, where the q output is set to one at the next rising edge of the clock. |

# Table 21: Pin Descriptions

| Name | Туре   | Description                                                                                                                                                                                                                                                                                        |  |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| d    | Input  | Data input.                                                                                                                                                                                                                                                                                        |  |

| sn   | Input  | Active-low asynchronous/synchronous set input. A low on sn sets the q output high independent of the other inputs if the sr_assertion parameter is set to "unclocked". If the sr_assertion parameter is set to "clocked", a low on rn sets the q output high at the next rising edge of the clock. |  |

| се   | Input  | Active-high clock enable input.                                                                                                                                                                                                                                                                    |  |

| ck   | Input  | Positive-edge clock input.                                                                                                                                                                                                                                                                         |  |

| q    | Output | Data output. The value present on the data input is transferred to the ${\bf q}$ output upon the rising edge of the clock if the clock enable input is high and the reset input is high.                                                                                                           |  |

# Table 22: ACX\_DFFES Function Table With sr\_assertion = "unclocked"

|    | Output |   |    |      |

|----|--------|---|----|------|

| sn | ce     | d | ck | P    |

| 0  | х      | Х | х  | 1    |

| 1  | 0      | х | х  | Hold |

| 1  | 1      | 0 | Î  | 0    |

| 1  | 1      | 1 | 1  | 1    |

# Table 23: ACX\_DFFES Function Table With sr\_assertion = "clocked"

|    | Output |   |          |      |

|----|--------|---|----------|------|

| sn | ce     | d | ck       | q    |

| 0  | х      | х | 1        | 1    |

| 1  | 0      | Х | х        | Hold |

| 1  | 1      | 0 | Î        | 0    |

| 1  | 1      | 1 | <b>↑</b> | 1    |

#### Verilog

```

ACX_DFFES #(

(1'b1),

.init

.sr_assertion ("unclocked")

) instance_name (

(user_out),

.q

.d

(user_din),

.sn

(user_set),

.ce

(user_clock_enable),

.ck

(user_clock)

);

```

```

----- ACHRONIX LIBRARY ------

library speedster7t;

use speedster7t.core.all;

----- DONE ACHRONIX LIBRARY -----

-- Component Instantiation

instance_name : ACX_DFFES

generic map (

init

=> '1',

sr_assertion => "unclocked"

)

port map (

=> user_out,

q

=> user_din,

d

sn

=> user_set,

ce

=> user_clock_enable,

ck

=> user_clock

);

```

# d \_\_\_\_\_ q ACX\_DFFN ckn\_\_\_O

# ACX\_DFFN (Negative Clock Edge D-Type Register)

# Figure 19: Negative Clock Edge D-Type Register

ACX\_DFFN is a single D-type register with data input (d) and clock (ckn) inputs and data (q) output. The data output is set to the value on the data input upon the next falling edge of the clock.

### Table 24: Parameters

| Para | meter | Defined<br>Values | Default<br>Value | Description                                                                                                                                                              |

|------|-------|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| init |       | 1'b0,1'b1         | 1'b0             | The init parameter defines the initial value of the output of the DFFN register. This is the value the register takes upon the initial application of power to the FPGA. |

# **Table 25:** Pin Descriptions

| Name | Туре   | Description                                                                                                                 |  |  |  |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| d    | Input  | Data input.                                                                                                                 |  |  |  |

| ckn  | Input  | legative-edge clock input.                                                                                                  |  |  |  |

| đ    | Output | Data output. The value present on the data input is transferred to the ${\bf q}$ output upon the falling edge of the clock. |  |  |  |

# Table 26: Function Table

| Inp  | outs         | Output |

|------|--------------|--------|

| d ck |              | đ      |

| 0    | ↓            | 0      |

| 1    | $\downarrow$ | 1      |

### Verilog

```

ACX_DFFN #(

.init (1'b0)

) instance_name (

.q (user_out),

.d (user_din),

.ckn (user_clock)

);

```

```

----- ACHRONIX LIBRARY ------

library speedster7t;

use speedster7t.core.all;

------- DONE ACHRONIX LIBRARY ------

-- Component Instantiation

instance_name : ACX_DFFN

generic map (

init => '0'

)

port map (

q => user_out,

d => user_out,

d => user_clock

);

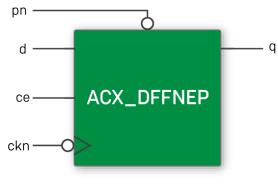

```

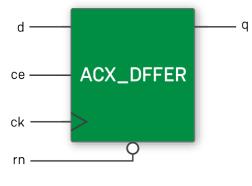

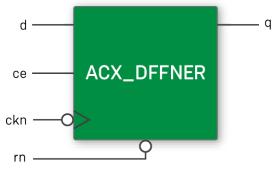

# ACX\_DFFNER (Negative Clock Edge D-Type Register With Clock Enable and Asynchronous/Synchronous Reset)

5374051-10.2022.11.17

# Figure 20: Negative Clock Edge D-Type Register With Clock Enable and Asynchronous/Synchronous Reset

ACX\_DFFNER is a single D-type register with data input (d), clock enable (ce), clock (ckn), and active-low reset (rn) inputs and data (q) output. The active-low reset input overrides all other inputs when it is asserted low and sets the data output low. The response of the q output in response to the asserted reset depends on the value of the sr\_assertion parameter and is detailed in Table: ACX\_DFFNER Function Table with sr\_assertion = "unclocked" (see page 38) and Table: ACX\_DFFNER Function Table with sr\_assertion = "clocked" (see page 38). If the reset input is not asserted, the data output is set to the value on the data input upon the next falling edge of the clock if the active-high clock enable input is asserted.

# Table 27: Parameters

| Parameter    | Defined<br>Values         | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|---------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| init         | 1'b0,1'b1                 | 1'b0             | The init parameter defines the initial value of the output of the DFFNER register. This is the value the register takes upon the initial application of power to the FPGA.                                                                                                                                                                                                                                                                                                                                                                        |

| sr_assertion | "unclocked",<br>"clocked" | "unclocked"      | The sr_assertion parameter defines the behavior of the output when the rn reset input is asserted. Assigning the sr_assertion to "unclocked" results in an asychronous assertion of the reset signal, where the q output is set to zero upon assertion of the active-low reset signal. Assigning the sr_assertion to "clocked" results in a synchronous assertion of the reset signal, where the q output is set to zero assertion to "clocked" results in a synchronous assertion of the reset signal, where the next falling edge of the clock. |

# Table 28: Pin Descriptions

| Name | Туре   | Description                                                                                                                                                                                                                                                                                                 |  |  |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| d    | Input  | Data input.                                                                                                                                                                                                                                                                                                 |  |  |

| rn   | Input  | Active-low asynchronous/synchronous reset input. A low on rn sets the q output low independent<br>of the other inputs if the sr_assertion parameter is set to "unclocked". If the sr_assertion<br>parameter is set to "clocked", a low on rn sets the q output low at the next falling edge of the<br>lock. |  |  |

| се   | Input  | Active-high clock enable input.                                                                                                                                                                                                                                                                             |  |  |

| ckn  | Input  | Negative-edge clock input.                                                                                                                                                                                                                                                                                  |  |  |

| đ    | Output | Data output. The value present on the data input is transferred to the ${}_{\rm T}$ output upon the falling edge of the clock if the clock enable input is high and the reset input is high.                                                                                                                |  |  |

# Table 29: ACX\_DFFNER Function Table With sr\_assertion = "unclocked"

|    | Output |   |     |      |

|----|--------|---|-----|------|

| rn | се     | d | ckn | q    |

| 0  | х      | х | х   | 0    |

| 1  | 0      | х | х   | Hold |

| 1  | 1      | 0 | Ļ   | 0    |

| 1  | 1      | 1 | Ļ   | 1    |

# Table 30: ACX\_DFFNER Function Table With sr\_assertion = "clocked"

|    | Output |   |     |      |

|----|--------|---|-----|------|

| rn | ce     | d | ckn | q    |

| 0  | х      | х | Ļ   | 0    |

| 1  | 0      | Х | х   | Hold |

| 1  | 1      | 0 | Ļ   | 0    |

| 1  | 1      | 1 | Ļ   | 1    |

#### Verilog

```

ACX_DFFNER #(

(1'b0),

.init

.sr_assertion ("unclocked")

) instance_name (

(user_out),

.q

.d

(user_din),

(user_reset),

.rn

.ce

(user_clock_enable),

.ckn

(user_clock)

);

```

```

----- ACHRONIX LIBRARY ------

library speedster7t;

use speedster7t.core.all;

----- DONE ACHRONIX LIBRARY ------

-- Component Instantiation

instance_name : ACX_DFFNER

generic map (

init

=> '0',

sr_assertion => "unclocked"

)

port map (

=> user_out,

q

=> user_din,

d

rn

=> user_reset,

се

=> user_clock_enable,

ckn

=> user_clock

);

```

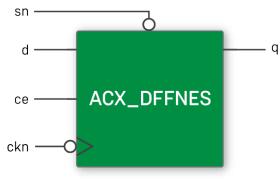

# ACX\_DFFNES (Negative Clock Edge D-Type Register With Clock Enable and Asynchronous/Synchronous Set)

5374051-11.2022.11.17

### Figure 21: Negative Clock Edge D-Type Register With Clock Enable and Asynchronous/Synchronous Set

ACX\_DFFNES is a single D-type register with data input (d), clock enable (ce), clock (ckn), and active-low set ( sn) inputs and data (q) output. The active-low set input overrides all other inputs when it is asserted low and sets the data output high. The response of the q output in response to the asserted set depends on the value of the sr\_assertion parameter and is detailed in Table: ACX\_DFFNES Function Table with sr\_assertion = "unclocked" (see page 42) and Table: ACX\_DFFNES Function Table with sr\_assertion = "clocked" (see page 43). If the set input is not asserted, the data output is set to the value on the data input upon the next falling edge of the clock if the active-high clock enable input is asserted.

# Table 31: Parameters

| Parameter    | Defined<br>Values         | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|---------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| init         | 1'b0,1'b1                 | 1'b1             | The init parameter defines the initial value of the output of the DFFNES register. This is the value the register takes upon the initial application of power to the FPGA.                                                                                                                                                                                                                                                                            |

| sr_assertion | "unclocked",<br>"clocked" | "unclocked"      | The sr_assertion parameter defines the behavior of the output when the sn set input is asserted. Assigning the sr_assertion to "unclocked" results in an asychronous assertion of the set signal, where the q output is set to one upon assertion of the active-low set signal. Assigning the sr_assertion to "clocked" results in a synchronous assertion of the set signal, where the q output is set to one at the next falling edge of the clock. |

# **Table 32:** Pin Descriptions

| Name | Туре   | Description                                                                                                                                                                                                                                                                                         |  |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| d    | Input  | Data input.                                                                                                                                                                                                                                                                                         |  |

| sn   | Input  | Active-low asynchronous/synchronous set input. A low on sn sets the q output high independent of the other inputs if the sr_assertion parameter is set to "unclocked". If the sr_assertion parameter is set to "clocked", a low on sn sets the q output high at the next falling edge of the clock. |  |

| се   | Input  | Active-high clock enable input.                                                                                                                                                                                                                                                                     |  |

| ckn  | Input  | Negative-edge clock input.                                                                                                                                                                                                                                                                          |  |

| đ    | Output | Data output. The value present on the data input is transferred to the ${}_{\rm T}$ output upon the falling edge of the clock if the clock enable input is high and the set input is high.                                                                                                          |  |

# Table 33: ACX\_DFFNES Function Table With sr\_assertion = "unclocked"

|    | Output |   |     |      |

|----|--------|---|-----|------|

| sn | ce     | d | ckn | q    |

| 0  | х      | х | x   | 1    |

| 1  | 0      | х | х   | Hold |

| 1  | 1      | 0 | Ļ   | 0    |

| 1  | 1      | 1 | Ļ   | 1    |

# Table 34: ACX\_DFFNES Function Table With sr\_assertion = "clocked"

|    | Output |   |     |      |

|----|--------|---|-----|------|

| sn | ce     | d | ckn | q    |

| 0  | х      | Х | Ļ   | 1    |

| 1  | 0      | Х | х   | Hold |

| 1  | 1      | 0 | Ļ   | 0    |

| 1  | 1      | 1 | Ļ   | 1    |

#### Verilog

```

ACX_DFFNES #(

(1'b1),

.init

.sr_assertion ("unclocked")

) instance_name (

(user_out),

.q

.d

(user_din),

(user_set),

.sn

.ce

(user_clock_enable),

.ckn

(user_clock)

);

```

```

----- ACHRONIX LIBRARY ------

library speedster7t;

use speedster7t.core.all;

----- DONE ACHRONIX LIBRARY ------

-- Component Instantiation

instance_name : ACX_DFFNES

generic map (

init

=> '1',

sr_assertion => "unclocked"

)

port map (

=> user_out,

q

=> user_din,

d

sn

=> user_set,

се

=> user_clock_enable,

ckn

=> user_clock

);

```

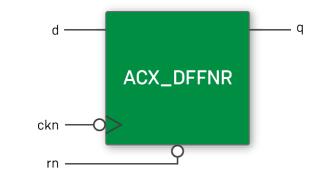

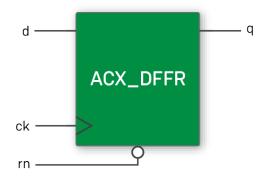

# ACX\_DFFNR (Negative Clock Edge D-Type Register With Asynchronous Reset)

# Figure 22: Negative Clock Edge D-Type Register With Asynchronous Reset

ACX\_DFFNR is a single D-type register with data input (d), clock (ckn), and active-low reset (rn) inputs and data (q) output. The active-low reset input overrides the other inputs when it is asserted low and sets the data output low. The response of the q output in response to the asserted reset is described under the sr\_assertion parameter. If the reset input is not asserted, the data output is set to the value on the data input upon the next falling edge of the clock.

#### Table 35: Parameters

| Parameter    | Defined<br>Values         | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|---------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| init         | 1'b0,1'b1                 | 1'b0             | The init parameter defines the initial value of the output of the DFFNR register. This is the value the register takes upon the initial application of power to the FPGA.                                                                                                                                                                                                                                                                                                 |

| sr_assertion | "unclocked",<br>"clocked" | "unclocked"      | The sr_assertion parameter defines the behavior of the output<br>when the rn reset input is asserted. Assigning the sr_assertion<br>to "unclocked" results in an asychronous assertion of the reset<br>signal, where the q output is set low upon assertion of the active-low<br>reset signal. Assigning the sr_assertion to "clocked" results in a<br>synchronous assertion of the reset signal, where the q output is set<br>low at the next falling edge of the clock. |

# Table 36: Pin Descriptions

| Name | Туре   | Description                                                                                                                                                         |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d    | Input  | Data input.                                                                                                                                                         |

| rn   | Input  | Active-low asynchronous reset input. A low on ${\tt rn}$ sets the ${\tt q}$ output low independent of the other inputs.                                             |

| ckn  | Input  | Negative-edge clock input.                                                                                                                                          |

| đ    | Output | Data output. The value present on the data input is transferred to the ${\bf q}$ output upon the falling edge of the clock if the asynchronous reset input is high. |

# Table 37: Function Table With sr\_assertion = "unclocked"

|    | Input | Output |      |

|----|-------|--------|------|

| rn | d     | ckn    | P    |

| 0  | Х     | х      | 0    |

| 1  | х     | х      | Hold |

| 1  | 0     | Ļ      | 0    |

| 1  | 1     | Ļ      | 1    |

# Table 38: Function Table With sr\_assertion = "clocked"

|    | Output |              |      |

|----|--------|--------------|------|

| rn | d      | ckn          | q    |

| 0  | Х      | $\downarrow$ | 0    |

| 1  | х      | х            | Hold |

| 1  | 0      | $\downarrow$ | 0    |

| 1  | 1      | Ļ            | 1    |

#### Verilog

```

ACX_DFFNR #(

.init (1'b0)

) instance_name (

.q (user_out),

.d (user_din),

.rn (user_reset),

.ckn (user_clock)

);

```

```

----- ACHRONIX LIBRARY ------

library speedster7t;

use speedster7t.core.all;

----- DONE ACHRONIX LIBRARY -----

-- Component Instantiation

instance_name : ACX_DFFNR

generic map (

=> '0'

init

)

port map (

=> user_out,

=> user_din,

=> user_reset,

q

d

rn

ckn => user_clock

);

```

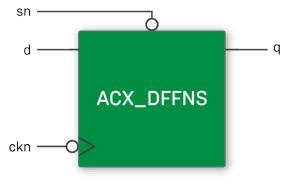

# ACX\_DFFNS (Negative Clock Edge D-Type Register With Asynchronous Set)

5374051-13.2022.11.17

# Figure 23: Negative Clock Edge D-Type Register With Asynchronous Set

ACX\_DFFNS is a single D-type register with data input (d), clock (ckn), and active-low set (sn) inputs and data ( q) output. The active-low set input overrides the other inputs when it is asserted low and sets the data output high. The response of the q output in response to the asserted set is described under the sr\_assertion parameter. If the set input is not asserted, the data output is set to the value on the data input upon the next falling edge of the clock.

#### **Table 39: Parameters**

| Parameter    | Defined<br>Values         | Default<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|---------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

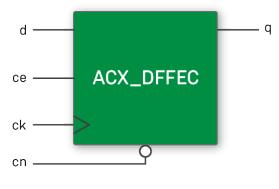

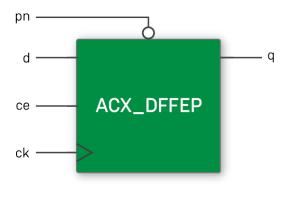

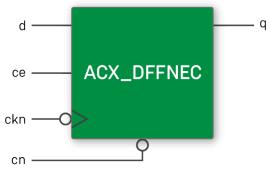

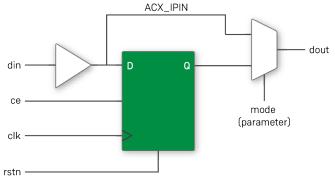

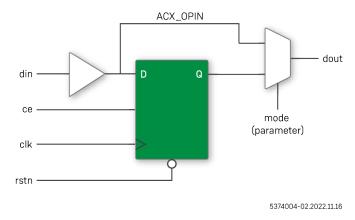

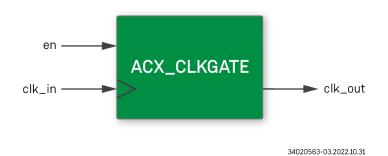

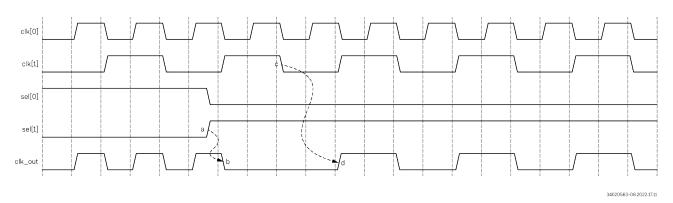

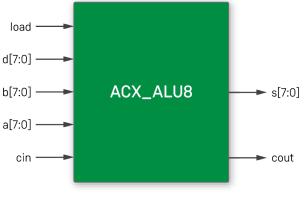

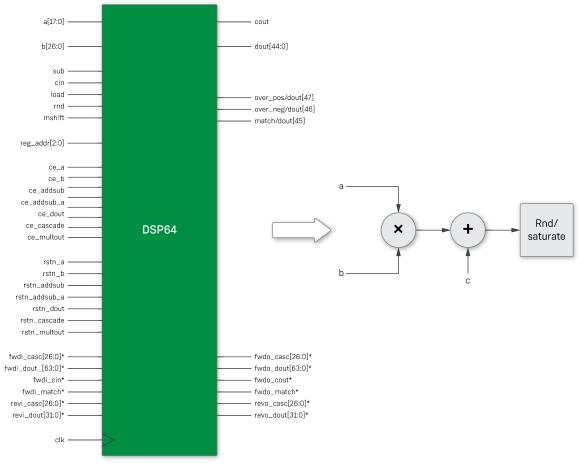

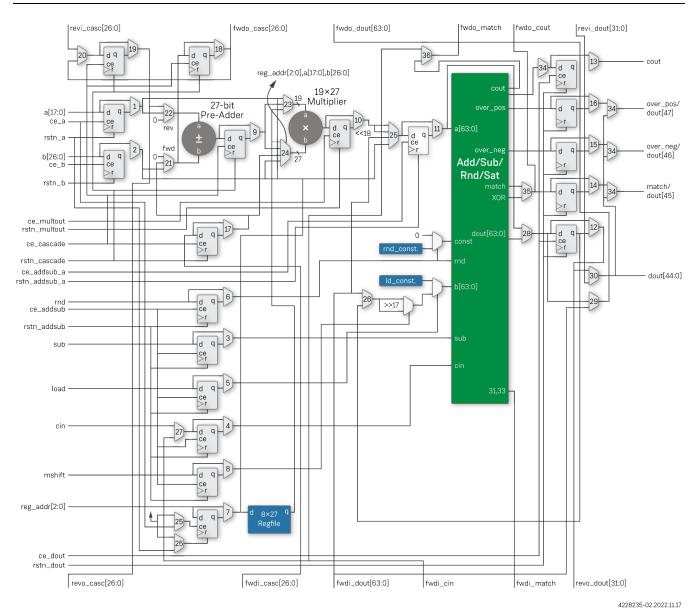

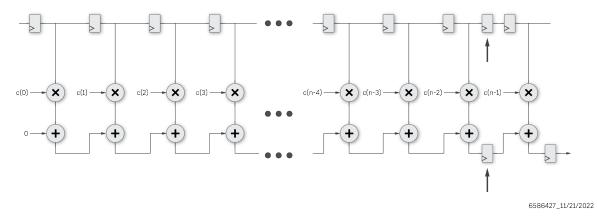

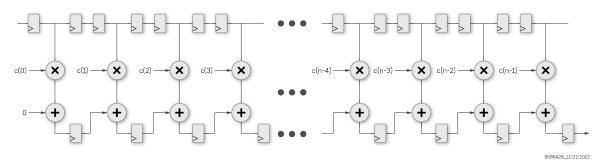

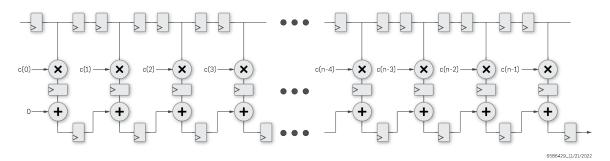

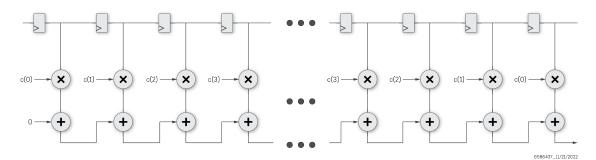

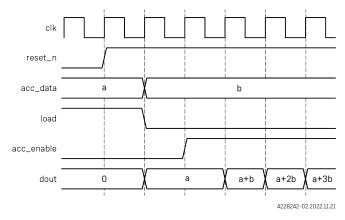

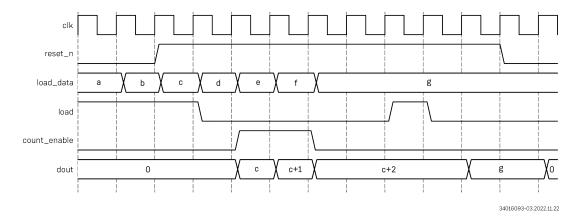

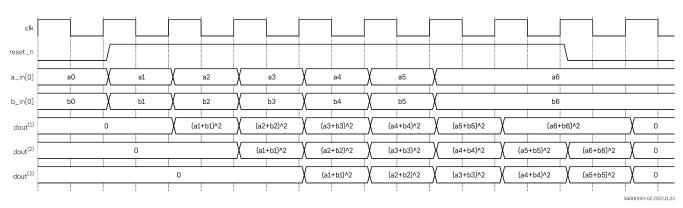

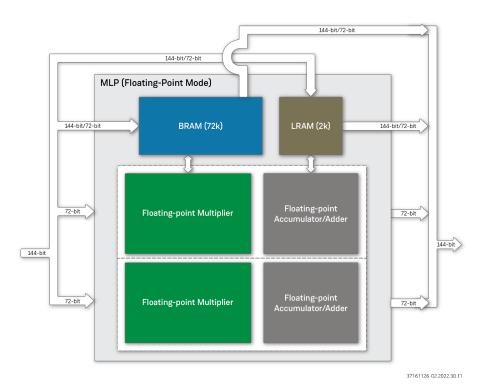

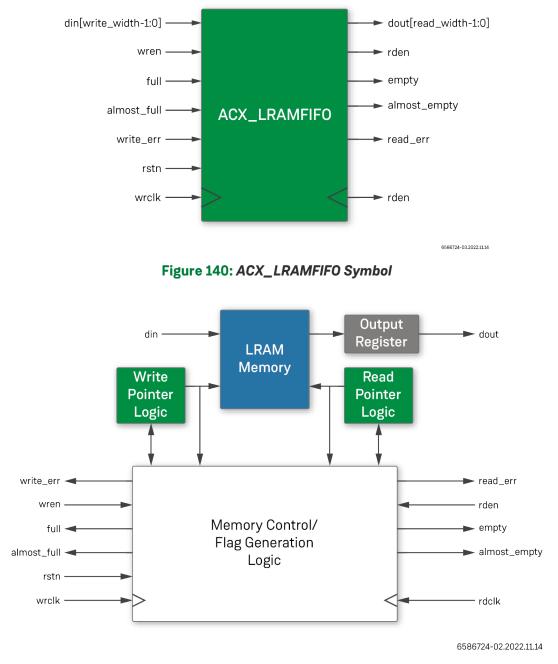

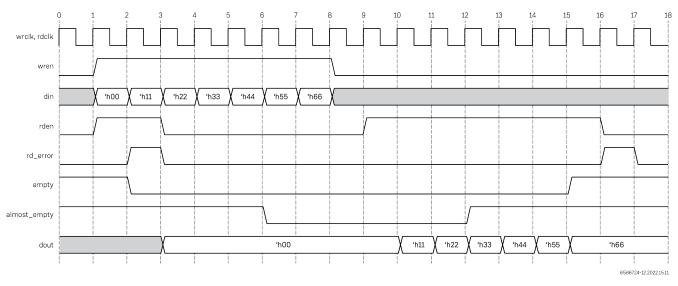

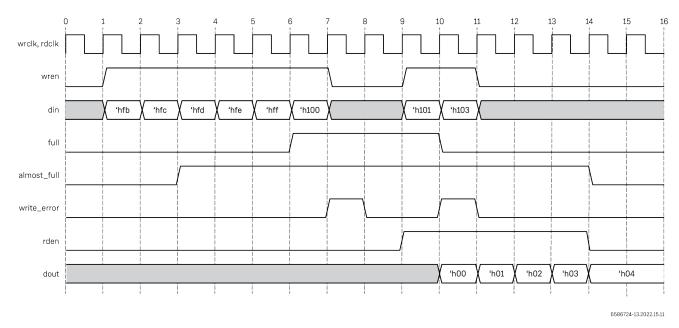

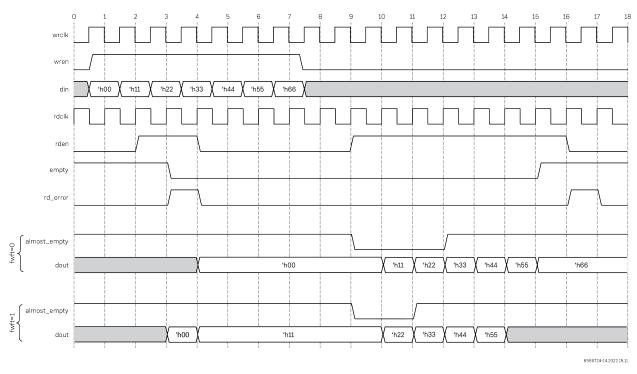

| init         | 1'b0,1'b1                 | 1'b1             | The init parameter defines the initial value of the output of the DFFNS register. This is the value the register takes upon the initial application of power to the FPGA.                                                                                                                                                                                                                                                                             |