# Software Development Kit User Guide (UG107)

**All Achronix Devices**

# Copyrights, Trademarks and Disclaimers

Copyright © 2022 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedster and VectorPath are registered trademarks, and Speedcore and Speedchip are trademarks of Achronix Semiconductor Corporation. All other trademarks are the property of their prospective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

#### **Achronix Semiconductor Corporation**

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail: info@achronix.com

# Table of Contents

| Chapter - 1: Introduction            |    |

|--------------------------------------|----|

| Software Stack                       | 9  |

| Chapter - 2: Installation            |    |

| Prerequisites                        | 10 |

| Achronix SDK installation            | 11 |

| Directory Structure                  | 11 |

| Compiling the Achronix SDK           | 12 |

| Testing the Achronix SDK             | 12 |

| Chapter - 3: Developing Applications | 14 |

| Minimum Requirements                 |    |

| Compilation                          | 14 |

| Runtime                              |    |

| Chapter - 4: Memory Addressing       | 15 |

| FPGA Addressing                      |    |

| Host Addressing                      |    |

| BAR Assignment                       | 16 |

| Device                               |    |

| Software                             |    |

| Recommendations                      |    |

| Address Translation Unit (ATU)       | 18 |

| Bar Match Mode                       | 20 |

| Address Match Mode                   | 20 |

| DMA Transfers                        | 20 |

| 2D NoC Physical Address Calculations | 20 |

| Basic Operation                      | 21 |

| Linked List Mode                     | 22 |

| Design Requirements                  | 24 |

| Achronix_DDR4.cpp                    | 24 |

| Achronix_GDDR6.cpp                   | 24 |

| Achronix_PCI.cpp                     | 24 |

| DMA               | A_example.cpp             | 25 |

|-------------------|---------------------------|----|

| Chap <sup>,</sup> | ter - 5: SDK Functions    | 26 |

| Quic              | ck Reference Table        | 26 |

| util_             | _calc_nap_absolute_addr() | 27 |

|                   | Description               | 27 |

| C                 | Call                      | 27 |

|                   | Arguments                 |    |

| F                 | Return Value              | 27 |

| util_             | _wait_microseconds()      | 28 |

|                   | Description               |    |

|                   | Call                      |    |

|                   | Arguments                 |    |

| F                 | Return Value              | 28 |

|                   | _wait_seconds()           |    |

|                   | Description               |    |

|                   | Call                      |    |

|                   | Arguments                 |    |

|                   | Return Value              |    |

|                   | reg_write_offset()        |    |

|                   | Description               |    |

|                   | Call                      |    |

|                   | Arguments                 |    |

|                   | Return Value              |    |

| •                 | reg_read_offset()         |    |

|                   | Description               |    |

|                   | Call                      |    |

|                   | Arguments                 |    |

|                   |                           |    |

| •                 | reg_set_bits_offset()     |    |

|                   | Description               |    |

|                   | Call                      |    |

|                   | Arguments                 |    |

|                   |                           |    |

| •                 | reg_clear_bits_offset()   |    |

|                   | Description               |    |

| C                 | Call                      | 33 |

|    | Arguments Return Value    |    |

|----|---------------------------|----|

| •  | _read_reg_ctrl_version()  |    |

|    | Call                      | 34 |

|    | Return Value              |    |

| •  | Description Call          | 35 |

|    | Arguments                 | 35 |

| dm | a_build_data_descriptor() | 36 |

|    | Description               |    |

|    | Arguments                 |    |

| dm | a_build_link_descriptor() | 37 |

|    | Description               | 37 |

|    | Arguments                 |    |

|    | a_init()                  |    |

|    | Call     Arguments        |    |

|    | Return Value              | 38 |

|    | a_config()                | 39 |

|    | Arguments Return Value    |    |

|    | a_start() Description     |    |

|    | Call                      |    |

|    | Return Value              |    |

| dma_halt()  Description  Call  Arguments  Return Value | . 41<br>. 41<br>. 41 |

|--------------------------------------------------------|----------------------|

| dma_get_status()                                       | 42                   |

| Description                                            | 42                   |

| Call                                                   |                      |

| Arguments                                              |                      |

| Return Value                                           | 42                   |

| dma_wait()                                             | 43                   |

| Description                                            | 43                   |

| Call                                                   | 43                   |

| Arguments                                              | 43                   |

| Return Value                                           | 43                   |

| atu_get_context()                                      | 44                   |

| Description                                            | 44                   |

| Call                                                   | 44                   |

| Arguments                                              | 44                   |

| Return Value                                           | 44                   |

| atu_find_regions()                                     | 45                   |

| Description                                            | 45                   |

| Call                                                   | 45                   |

| Arguments                                              | 45                   |

| Return Value                                           | 45                   |

| atu_get_region()                                       | 46                   |

| Description                                            | 46                   |

| Call                                                   | 46                   |

| Arguments                                              | 46                   |

| Return Value                                           | 46                   |

| atu_put_region()                                       | 47                   |

| Description                                            |                      |

| Call                                                   | 47                   |

| Arguments                                              | 47                   |

| Return Value                                           | 47                   |

| Chapter - 6: SDK Structures                            | 48                   |

| DmaCommand_t  Description  Definition  Fields            |    |

|----------------------------------------------------------|----|

| DMADataDescriptor                                        | 50 |

| Fields                                                   |    |

| DMALinkDescriptor  Description  Definition               | 51 |

| Fields                                                   |    |

| Chapter - 7: SDK Classes                                 | 52 |

| PCIDevice  Description                                   | 52 |

| Definition                                               |    |

| DMAHostBuffer  Description  Definition  Member Functions | 54 |

| DMADescriptorList  Description  Definition               | 56 |

| Member Functions                                         | 58 |

| ATUContext                                               | 60 |

| Definition                                               |    |

| ATURegion                                                | 61 |

| Member Functions                                         |    |

# Chapter - 1: Introduction

The Achronix Software Development Kit (SDK) is a set of functions and data structures which enable users of the Speedster®7t family of devices to write applications that communicate with and control their designs using the PCIe interface.

The SDK consists of pre-compiled binary (private) libraries, source code for common public libraries, and source code for several example applications showing how common features can be implemented.

#### **Note**

The Achronix SDK is currently only available for the Linux platform with an installed Achronix VectorPath® S7t-VG6 accelerator card. For Microsoft Windows, or non-VectorPath support, please contact support@achronix.com.

### Software Stack

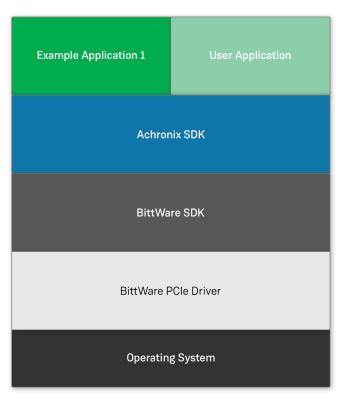

The Achronix SDK is built on top of the BittWare SDK. The BittWare SDK supplies the low-level routines performing PCle device enumeration and recognition, buffer allocation, and memory-mapped reads and writes via the PCle device.

A conceptual diagram of the software stack is shown in the following figure.

113824702-01.2022.27.08

Figure 1: Software Stack

# Chapter - 2: Installation

# Prerequisites

Before compiling code using the Achronix SDK, install the BittWare SDK available from the BittWare VectorPath developer portal at https://developer.bittware.com. See the Support Article for help getting started. Access to the portal and SDK download is available only to verified purchasers of the VectorPath card. Please contact BittWare Support to obtain a developer account.

The default locations for installation of the BittWare SDK are shown below:

```

BittWare SDK FIle Locations

BittWare include files : /usr/share/bittware-sdk/include

BittWare library files : /usr/lib/x86_64-linux-gnu

```

If the BittWare SDK is installed to a different location, the appropriate entries in each of the Achronix makefiles must be updated.

The Linux GCC compiler must also be installed and available in the path. The SDK requires C++ 14 support, available in GCC versions 5.2 and later.

### Achronix SDK installation

# **Directory Structure**

The Achronix SDK has the following directory structure:

#### **Description Directory** <achronix SDK> The root directory where the SDK is installed. /examples Contains source code for various example applications built with the SDK. /ATU example Demonstrates how to read and write configuration settings to the PCle Address Translation Unit. /buffer alloc Demonstrates how to allocate a PCIe buffer. Supports initiating a DMA transaction using JTAG commands instead of a C++ application. /DMA example Full DMA example. Supports GDDR6, DDR4 and fabric NAP as DMA targets. Options to configure buffer sizes and measure performance. Optional descriptor lists. /PCI read write Demonstrates how to perform memory-mapped reads and writes over PCIe. /include Include files to be added to the user makefile. Achronix DDR4.h Header for the functions in Achronix DDR4.cpp. Achronix GDDR6.h Header for the functions in Achronix GDDR6.cpp. Achronix PCI.h Header for the functions in Achronix PCI.cpp. Pre-compiled shared object library files. libacxsdk-priv.so Pre-compiled (private) shared object library to link into the application software binaries. libacxsdk-pub.so Shared object library for the public APIs created by compiling files in the /src directory. Source code for the public SDK APIs. User compiled into a shared library in the /lib directory. Achronix DDR4.cpp Source code for a set of examples for initializing and driving DDR4 transactions. Achronix GDDR6.cpp Source code for a set of examples that monitor GDDR6 initialization. Achronix PCI.cpp Source code for a set of public APIs related to PCIe operation. Makefile Makefile to build lib/libacxsdk-pub.so. 113824702-03.2022.18.10

Figure 2: Achronix SDK Directory Structure

The Achronix SDK may be copied and installed to any location that best suits the user application. When installed, it is necessary to set the LD\_LIBRARY\_PATH environment variable to include the <achronix\_SDK>/lib directory.

# Compiling the Achronix SDK

Compiling the Achronix SDK is optional and only required if the source code has been modified. Pre-compiled versions of the shared libraries and the demo application executables are included with the SDK. Before compiling an application using the Achronix SDK, it is necessary to compile the libsdk-pub.so shared object file as shown below:

```

# To compile the libsdk-pub shared object file

$ cd <achronix_SDK>/src - Change to the source code directory.

$ make clean - Delete all object (.o) and /lib/libacxsdk-pub.so files.

$ make - Compile /lib/libacxsdk-pub.so.

```

The Achronix SDK libraries (libacxsdk-priv.so and libacxsdk-pub.so) comprise all of the functions defined in the header files in the /include directory. These functions are then available to any application by linking the shared object files into any application build.

It is then necessary to compile the supplied example applications. Instructions for compiling the DMA\_example are shown below. These steps can be repeated for the other example applications.

```

# To compile the DMA_example application

$ cd <achronix_SDK>/examples/DMA_example - Change to the application directory.

$ make clean - Delete all object (.o) and any executable files.

$ make - Compile the application.

```

This builds an executable named <achronix\_SDK>/sw/examples/dma\_example that can be used as a model for developing your own applications.

#### Note

When the application is compiled, it might be necessary to set execute permissions on the file. This is achieved with the command: chmod +x < application>.

# Testing the Achronix SDK

To verify that the software and the VectorPath card are installed properly, run the DMA example as follows:

1. Run the following command to see the available command line options:

```

$ <achronix_SDK>/sw/examples/dma_example --help

```

2. Run the following command to perform a small DMA test:

```

$ <achronix_SDK>/sw/examples/dma_example -b 0x400000 -d H2D2H -e DDR4 -f random

```

#### The test does the following:

- Allocates two 4MB buffers on the host server.

- Fills the first buffer with random data.

- Transfers the contents of the buffer from the host to the device (the H2D direction) into the DDR4 memory space.

- Transfers the same data back from device to the host (the D2H direction) into the second memory buffer.

- Compares the two buffers to verify that the data made the round trip without errors.

- Computes the achieved bandwidth in each direction.

# Chapter - 3: Developing Applications

To develop your own applications with the SDK, it is recommended to follow the same format as one of the existing example applications. It is necessary to include the same BittWare and Achronix SDK header files, and to link with the same set of BittWare and Achronix shared library files. Consult the included Makefiles for more detail.

# Minimum Requirements

# Compilation

The following are the minimum requirements necessary to compile the Achronix SDK into user software:

- The environment variable LD\_LIBRARY\_PATH must include <achronix\_SDK>/lib

- Include the Achronix SDK header files in the <achronix\_SDK>/include directory into C/C++ code

- Include the Achronix SDK shared object files in the <achronix\_SDK>/lib directory when linking

### Runtime

• Ensure that the BittWare library files are installed in /usr/lib/x86\_64-linux-gnu

# Chapter - 4: Memory Addressing

In order to determine the correct address for an FPGA memory space, whether within the interface subsystems or the fabric, it is necessary to understand the differences between how the FPGA and the software map the address space.

# FPGA Addressing

The FPGA maps all addresses as a 42-bit linear address space as described in the *Speedster7t Network on Chip User Guide* (UG089). In this linear space, each interface subsystem can be address as a hierarchy of addresses, sub-divided as follows:

- Space major different memory areas such as CSR\_SPACE (interface subsystem registers), NAP\_SPACE (NAPs in the programmable fabric) and DDR4\_SPACE, GDDR6\_SPACE (external memories).

- Target either interface subsystem IP blocks normally within the CSR\_SPACE, e.g., PCIE\_0, PCIE\_1, ETHERNET\_0, etc., or individual external memory controllers, e.g., GDDR6\_0, GDDR6\_1, etc.

- IP ID within an interface subsystem, individual blocks. So, for example, with Ethernet, the CORE registers, then SERDES\_0 and SERDES\_1 register areas.

- Address the memory address.

The overall size within each of these areas varies. However, the two most common to be accessed by external software are CSR\_SPACE and NAP\_SPACE. They have the following addressing:

#### Table 1: CSR\_SPACE Addressing

| Name      | Space        | Target       | IP_ID        | Register Address |

|-----------|--------------|--------------|--------------|------------------|

| CSR_SPACE | Bits [41:34] | Bits [33:28] | Bits [27:24] | Bits [23:0]      |

#### Table 2: NAP\_SPACE Addressing

| Name                         | Space        | NAP Column   | NAP Row      | Register Address |

|------------------------------|--------------|--------------|--------------|------------------|

| NAP_SPACE <sup>(1)</sup> (2) | Bits [41:35] | Bits [34:31] | Bits [30:28] | Bits [27:0]      |

#### **Table Notes**

- 1. The NAPs are numbered from 1 for placement and within the device. However, they are addressed from 0.

- 2. The function util\_calc\_nap\_absolute\_address() returns bits [41:28] of the NAP address when given the NAP column and row locations (numbered from 1).

In summary, the FPGA memory space is a 42-bit linear address space giving access to all registers and external memory locations.

# Host Addressing

PCIe devices such as the VectorPath card are memory-mapped, meaning that they present their capabilities to the host CPU as one or more regions of memory that are mapped into the host memory space. Reads and writes to registers or memories on the FPGA are performed by reading or writing to the appropriate address on the host.

In order to implement this memory-mapping scheme, PCIe uses BARs (Base Address Registers) to specify the mapping from the host machine address space to the PCIe device address space(s). Each BAR defines the size of an address space and the local (device) base address. During PCIe enumeration, the host assigns a memory region of the same size as each BAR, and maps this to the host (usually 64-bit) physical memory space. The local, or device, base address is the start of a memory region of the same size in the FPGA 42-bit address space (as described in FPGA Addressing (see page 15)). When host software reads from, or writes to, a physical address covered by one of the BARs, that transaction is intercepted by the host PCIe controller and routed to the correct location on the FPGA.

The PCIe controller on the Speedster7t FPGA contains six 32-bit (or three 64-bit) BAR registers, each of which supports up to a 64MB address space. It is therefore clear that the 42-bit address space within the device cannot be mapped to the host in its entirety. It is necessary to configure the BARs and their sizes to match the individual user design requirements. The size of, and FPGA base addresses assigned to, each BAR are defined in the PCIe IP configurator. Refer to the *Speedster7t PCIe User Guide* (UG098), available under NDA. The base addresses in the host address space are assigned by the host during PCIe device enumeration. For more information about how to access the BAR registers from the host, refer to the BittWare SDK User Guide.

It is important to understand that BAR register configuration is specific to a design. The capabilities of a user application must match the design BAR register selection. When selecting CSR register spaces, or the NAP to address, the design and user application BAR definitions must be aligned.

#### Warning

The BAR register selection is specific to a design. The user application must match the BAR register selection.

#### Note

DMA accesses do not use BAR registers. DMA transfers use the physical address within the device and host.

# **BAR Assignment**

To understand the alignment between the design and the user application BAR assignment, the combined demonstration design (pcie\_gddr6\_ddr4\_vp\_demo) is used as an example. This design demonstrates PCIe DMA to and from external memory, (DDR4 and GDDR6), and also to a NAP in the fabric, using the DMA\_example application provided within the Achronix SDK.

### Device

The PCIe IP definitions, including the BAR assignments, are specified in the ACE I/O Designer, which is accessed from the IP Configuration Perspective in the ACE GUI. The BAR assignments, along with other PCIe configurations for the above demonstration design, are contained within /src/acxip/pcie\_express\_x16.acxip. The BARs are configured in the I/O Designer as shown in the following table.

**Table 3: Example BAR Mappings**

| BAR                                    | Туре      | Size (Bytes)                    | Address         | FPGA memory space                      |

|----------------------------------------|-----------|---------------------------------|-----------------|----------------------------------------|

| 0                                      | Memory    | 64M                             | 0x042_4000_0000 | NAP located in column 5, row 5.        |

| 1 Memory 1M 0x043_e000_0000 NAP locate |           | NAP located in column 8, row 7. |                 |                                        |

| 2                                      | Interrupt | 1M                              | 0x000_0000_0000 | Used by PCIe core for MSIX interrupts. |

| 3                                      | Memory    | 1M                              | 0x081_9100_0000 | Base of CSR_SPACE PCIE_1 BASE_IP.      |

| 4                                      | Memory    | 1M                              | 0x002_0000_0000 | GDDR controller 0, channel 1.          |

| 5                                      | Memory    | 1M                              | 0x100_0000_0000 | Base of DDR4 memory.                   |

The two mandatory BAR mappings in this design are BAR 0 and BAR 3.

BAR 0 maps to a NAP located in column 5, row 5. Referencing /src/constraints/ace\_placements.pdc, it can be seen that this mapping relates to the fabric-based register control block. This block controls the design, operating the DDR4 training and transactions, and monitoring the GDDR6 training status:

```

Excerpt From ace_placements.pdc

# Register control block NAP placed in 5,5

set_placement -fixed {i:i_reg_control_block.i_axi_master.i_axi_master} {s:x_core.NOC[5][5].logic.

noc.nap_m}

```

BAR 3 is mapped to the Control and Status Register (CSR) space within the PCIe core. This mapping is required so the software can access the registers that configure and control the DMA transfers. Without this mapping, the application would not be able to perform DMA.

#### **Note**

It is strongly recommended that all designs have one BAR mapped to the PCle core register space (address 0x081\_9100\_0000). The number of that BAR must then be used in the application to access any DMA or PCle core functions.

### Software

Referencing the DMA\_example in /demo/sw/examples/DMA\_example.cpp, it can be seen how BAR 0 and BAR 3 are used to access the register control block, and the PCIe core registers:

```

Excerpt From DMA_example.cpp

// Configure mapping for each BAR.

// IMPORTANT - These can change on a per-design basis.

BwpciMs reg_ctrl_bar = BW_MS_BAR0; // Mapped to the register control block in the fabric

BwpciMs csr_bar = BW_MS_BAR3; // Mapped to the Control Status Registers

....

// DDR4 training is controlled and monitored by the reg_ctrl block, which will be

// accessed by one of the BARs

if ( acx::ddr4_run_training( device, reg_ctrl_bar, false) != 0 ) {

....

// Initialize the DMA core. Resets both engines (read and write) and sets arbitration weights.

Only need to do this once.

acx::dma_init( device, csr_bar, part, pcie_core );

```

### Recommendations

To ensure alignment between the device and the software, the following is recommended:

- Assign a BAR to the PCle core registers (0x081\_9100\_0000) and use this BAR for all PCle core

accesses in the software.

- If the design contains a register control block with a NAP, define a BAR with an address that matches the

location defined in the ace\_placements.pdc file. In the software use this BAR for all accesses to the

register control block.

- DMA transfers do not use BARs. To obtain the absolute address of a NAP for DMA access, use acx:: util\_calc\_nap\_absolute\_address(). For GDDR6 or DDR4 absolute addresses use the <target>\_SPACE define from /include/Achronix\_SDK.h, and add in the required memory offset.

- To perform memory-mapped reads and writes to device registers or memories without using DMA (sometimes called BAR reads and writes), define a BAR with a base address and size that covers the region of memory to access. For example, see BAR1, BAR4, and BAR5 defined in the table above.

# Address Translation Unit (ATU)

Mapping between the host 64-bit physical address space, and the device 42-bit NoC address space, is performed by the Address Translation Unit (ATU) part of the PCIe interface subsystem. When a user design accesses an address that has been assigned by the host OS to one of the device BARs, that address is passed to the ATU for translation from host address to device NoC address. If the ATU is unconfigured, the host addresses would be truncated or zero-padded to 42-bits (depending on whether the design uses 64-bit or 32-bit BARs) and then passed directly on into the NoC without translation. This would create an invalid address which would cause NoC access failures. The ATU is configured, using ACE, whenever a PCIe IP is configured and assigned BARs with an address offset and size.

The ATU consists of 100 regions, each of which can be individually configured with a mapping between one contiguous region of host memory addresses, and a corresponding region of addresses (of the same size) on the device.

#### Warning

If ATU regions are defined to be overlapping (either on the device code or the host side), the behavior is undefined.

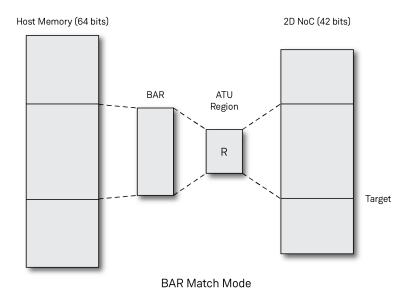

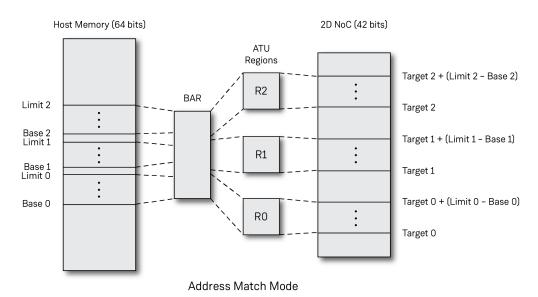

Each ATU region can be in one of two modes, BAR Match Mode or Address Match Mode, as illustrated in the following diagrams.

Figure 3: ATU Region Examples

### Bar Match Mode

The ATU translates all of the addresses covered by one BAR (either 32-bit or 64-bit BARs) into a single block of device memory of the same size. Therefore, since there are only six 32-bit BARs, a maximum of six ATU regions can be configured in Bar Match Mode. In this mode, only the device-side Target address for the BAR must be specified by the user, as the host-side Base and Limit addresses are assigned by the host operating system during enumeration.

#### Address Match Mode

Address match mode supports the full 100 ATU regions. Each region specifies a base address in host memory, a base address in device memory, and a region size. This scheme allows the addresses covered by a single BAR to be split up into a large number of individual slices that each map to any region of device memory. For example, a single BAR could be made to cover 80 different BRAMs, each connected to its own NAP in the Speedster7t FPGA 2D NoC. It is necessary to ensure that the regions are non-overlapping.

#### **Note**

Currently the ACE I/O Designer tool only supports BAR Match Mode. Address Match Mode can only be configured by using the Achronix SDK capabilities described below.

### **DMA Transfers**

Direct Memory Access (DMA) transfers do require the use of BAR registers (other than for configuring the DMA engine itself), and are therefore not limited by the number of BARs or the BAR sizes. The DMA engine built into the PCIe controller can efficiently transfer blocks of data of any size directly between the host *remote* 64-bit address space and the device *local* 42-bit address space. To perform a DMA transfer, the software must allocate a buffer on the host to source or receive the data, then configure DMA controller registers with the source and destination addresses and the number of bytes. When reading or writing the buffer from software the buffer must be referred to using its *virtual* address. However, when programming the DMA controller with the host buffer source or destination address, the buffer *physical* address must be used. The acxsdk::DmaHostBuffer object makes it convenient to obtain both the virtual and physical addresses for the buffer.

# 2D NoC Physical Address Calculations

#### Note

It is not necessary to have a BAR register map the memory location in the device for a DMA transfer.

To obtain the 42-bit NoC device physical address for a DMA transfer, the following methods are available:

- For a NAP in the fabric, call acx::util\_calc\_nap\_absolute\_address() with the NAP row and column index

- For DDR4, use the define DDR4\_SPACE to provide the base address, and add any necessary offset

- For GDDR6, use the define GDDR6\_SPACE to provide the base address and add any necessary offset.

#### **Note**

Each GDDR6 channel (two per controller) is addressed with addr[36:33]. It is therefore necessary to add  $0x2\_0000\_0000$  for each GDDR6 channel selected.

The following DMA example shows the use of these functions and defines for determining the device physical (local) address for a DMA transfer:

```

DMA Example

// Calculate the DMA target address in the device

uint64_t device_phys_base_addr = 0x0;

if (options.endpoint == acx::DDR4) {

// Leave room for descriptor lists at the base of DDR4. The DDR4 space starts from offset

0x0.

device_phys_base_addr = DDR4_SPACE + (uint64_t)0x10000;

} else if (options.endpoint == acx::GDDR6) {

device_phys_base_addr = GDDR6_SPACE;

} else if (options.endpoint == acx::NAP) {

// AXI BRAM responder NAP location is set in project pdc file

device_phys_base_addr = util_calc_nap_absolute_addr(part, axi_bram_resp_col,

axi_bram_resp_row);

}

```

### **Basic Operation**

In order to perform a DMA transfer, the software must first open the PCIe device and obtain a handle to it. With the Achronix SDK, this is achieved using the underlying BittWare SDK functions. Alternately, this handle can be obtained directly by using low-level OS system calls (out of the scope of this document). The Achronix SDK provides a C++ class named acxsdk::PCIDevice. The device is opened by calling the class constructor with the PCIe device\_id. By default, device\_id equals zero if there is only a single VectorPath card installed. In the event that multiple VectorPath cards are installed, the BittWare bw\_card\_list utility is used to determine the appropriate device\_id. After the device is opened, the PCIDevice class is used as the device handle. The device is automatically closed in the class destructor when it goes out of scope or the application exits.

For DMA, the software is required to allocate a host buffer and, if performing host-to-device DMA, copy the host data to the host buffer. The Achronix SDK utilizes the BittWare SDK functions to allocate that buffer providing a C++ class named acxsdk::DMAHostBuffer. Again, if necessary, it is possible to use direct low-level operating system calls. Using acxsdk::DMAHostBuffer, the buffer is created by calling the class constructor with a pointer to the PCIDevice and the size of the buffer in bytes. The buffer is automatically deallocated when the DMAHostBuffer object goes out of scope, or when the application exits.

#### Note

Maximum buffer size is currently limited to 4MB.

#### Warning

It is not possible to allocate the buffer with a simple malloc() call. The reason is that the DMAHostBuffer::get\_phys\_addr() function is required to obtain the buffer physical (not virtual) address.

The example below illustrates using the PCIDevice and DMAHostBuffer constructors. The function buffer. fill\_random() is used to fill the buffer with random data. The source for fill\_random() is contained within /src/Achronix\_PCI.cpp. This function may be edited to fill the buffer with application-specific data using the buffer virtual address. The source code for PCIDevice and DMAHostBuffer are also both available in /src/Achronix\_PCI.cpp; They can be customized if required.

```

acxsdk::PCIDevice device(options.device_id);

acxsdk::DMAHostBuffer buffer(&device, buffer_size_in_bytes);

buffer.fill_random();

```

Having opened the PCIe device and writing the required data into the DMAHostBuffer, the software must call acxsdk::dma\_init() to initialize the DMA controller. This initialization only needs to be called once at the start of the application as long as only a single process is using the DMA engine. The function requires the following:

- BwpciDevice pointer obtained by calling acxsdk::DMAHostBuffer::qet device()

- BwpciMs object for a BAR that maps to the CSR space in the FPGA

- Defines for the desired Achronix part name and PCle controller number.

```

acxsdk::dma_init(device.get_device(), csr_bar, acxsdk::AC7t1500ES0, acxsdk::PCIE_1);

```

Next, for each individual DMA transaction, an instance of a acxsdk:DmaCommand struct must be populated with parameters that describe the transaction. The most important parameters are:

- 1. The transfer direction.

- 2. The 42-bit device\_address (calculated in the code example above).

- 3. The 64-bit host\_address, obtained by calling DMAHostBuffer::get\_phys\_addr().

- 4. The buffer size in bytes, obtained from the DMAHostBuffer class.

```

acxsdk::DmaCommand myDmaCommand;

myDmaCommand.csr_bar = csr_bar;

myDmaCommand.pcie_core = acxsdk::PCIE_1;

myDmaCommand.dma_direction = acxsdk::HOST_TO_DEVICE;

myDmaCommand.dma_channel = options.channel;

myDmaCommand.device_address = device_phys_base_addr;

myDmaCommand.host_address = buffer->get_phys_addr();

myDmaCommand.size_in_bytes = buffer->get_size_in_bytes();

myDmaCommand.descriptor_list_address = 0x0;

```

Finally, for each transfer, the DMA engine is configured with acxdsk::dma\_config(), then the transfer started with acxsdk::dma\_start().

To wait for a DMA to complete, call the function <code>acxsdk::dma\_wait()</code>. This function returns after the DMA has completed. In the event that the DMA transaction does not complete correctly, or times-out, the function <code>acxsdk::dma\_halt()</code> must be called to abort the transaction before starting a new DMA transfer.

```

acxsdk::dma_config( device.get_device(), myDmaCommand );

acxsdk::dma_start(device.get_device(), myDmaCommand);

acxsdk::DmaStatus status = acxsdk::dma_wait(device.get_device(), myDmaCommand, /*timeout_in_second

s*/2);

if (status == acxsdk::DMA_RUNNING) {

acxsdk::dma_halt(device.get_device(), myDmaCommand);

// code to recover and re-issue the command

}

```

#### Linked List Mode

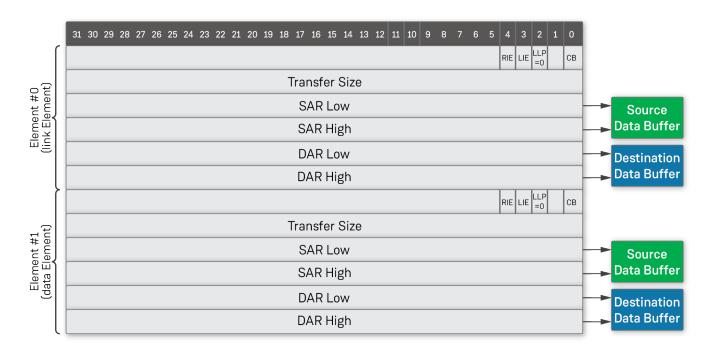

In addition to the basic DMA operation described above, the more advanced linked list mode is available to handle larger DMA transfers or streaming transactions more efficiently. In this mode, the DMA context (source address, target address, buffer size) is loaded into a data structure called a *DMA Descriptor* instead of being passed directly to dma\_config() through the DmaCommand struct. Multiple buffers can be transferred in a single call to dma\_start() by creating a descriptor for each buffer, and then combining the descriptors into a linked list. The descriptor list is then transferred into device memory, and the physical address of the list is passed into the dma\_config() call through the DmaCommand struct. The descriptor list my be placed anywhere in device memory (DDR4, GDDR6, or a BRAM connected to a NAP). The descriptor list may be transferred into device memory using individual BAR writes, or (recommended) a small DMA transaction.

To aid in constructing a DMA descriptor list, the Achronix SDK provides a small class named <code>acxsdk::DMADescriptorList</code>. After creating the <code>DMADescriptorList</code>, the descriptor data is populated by calling the <code>acxsdk::build\_data\_descriptor()</code> function once for each <code>DMAHostBuffer</code>. In the example below, an array of host buffers, all of the same size have been allocated. The source code for the <code>DMADescriptorList</code> class is available in <code>/src/Achronix PCI.cpp</code> and can be customized if required to suit the application.

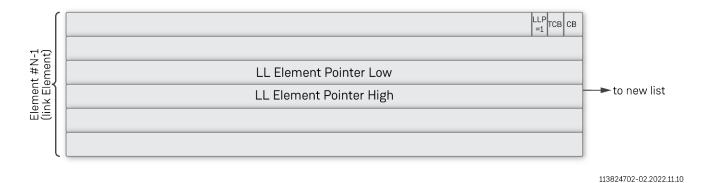

Every block of descriptors in a DMADescriptorList consists of one or more DMADataDescriptors and ends with a single DMALinkDescriptor that might link to another DMADescriptorList. The use of multiple linked DMADescriptorLists is beyond the scope of this document. The DMADescriptorList constructor populates the terminating DMALinkDescriptor with a pointer back to the first DMADataDescriptor in the list, which is the default configuration for a single unlinked descriptor list.

#### **Note**

The function dma\_build\_link\_descriptor() is available to populate the DMALinkDescriptor.

```

acxsdk::DMADescriptorList descriptors(&device, options.num_descriptors, GDDR6_SPACE);

for (uint64_t i = 0; i < options.num_descriptors; i++) {

acxsdk::dma_build_data_descriptor(descriptors[i],

options.buffer_size_in_bytes,

buffer_vec[i]->get_phys_addr(),

device_phys_base_addr + (options.buffer_size_in_bytes * (uint64_t)i));

}

```

After building the DMADescriptorList, the list must be transferred into device memory, which can be performed using the DMA Basic Operation (see page 21) procedure outlined above. For convenience, the DMADescriptorClass makes available the get\_device\_phys\_addr() function which returns an address that is then passed to the class constructor. In the example above, the physical address of token GDDR6\_SPACE is used. This address equates to the lowest of GDDR6 memory addresses in the 42-bit NoC address space. For more information, see the DMA\_example source code.

After the descriptor list is complete, the DmaCommand structure is populated with the DMA transfer parameters. Comparing the linked list mode example below with the Basic Operation (see page 21) example above, it can been seen that the physical address of the descriptor list in device memory is used in place of the device\_address, host\_address, and size\_in\_bytes elements.

```

acxsdk::DmaCommand myDmaCommand;

myDmaCommand.csr_bar = csr_bar;

myDmaCommand.pcie_core = pcie_core;

myDmaCommand.dma_direction = acxsdk::HOST_TO_DEVICE;

myDmaCommand.dma_channel = options.channel;

myDmaCommand.verbosity = options.verbosity;

myDmaCommand.device_address = 0x0;

myDmaCommand.host_address = 0x0;

myDmaCommand.size_in_bytes = 0x0;

myDmaCommand.descriptor_list_address = descriptors->get_device_phys_addr();

```

To initiate, start and wait the the DMA, the same commands, <code>dma\_config()</code>, <code>dma\_start()</code>, and <code>dma\_wait()</code>, are used. The DMA controller performs all of the transfers specified in the descriptor list before returning from the <code>dma\_wait()</code> function.

# Design Requirements

This section documents the minimum requirements for designs that use various components of the SDK. See the referenced demo design for more information and an example of the following.

# Achronix\_DDR4.cpp

The DDR4 functions manage training of the DDR4 controller (using the ddr4\_training\_polling\_block in the fabric) and, in addition, control sending and reception of data along with performance monitoring of the throughput to and from the DDR4 (using the axi\_pkt\_gen, axi\_pkt\_chk and axi\_performance\_monitor blocks in the fabric). In order to use these functions, the fabric must contain the preceding instances. The header file /include/Achronix\_DDR4.h specifies the register control block addresses for the various DDR4 control blocks. These addresses should be modified to match the fabric design.

# Achronix\_GDDR6.cpp

The GDDR6 functions read the status of the Achronix Device Manager (ADM) that is configured to perform GDDR6 training. In order to use these functions, the fabric must contain an instance of the ADM configured to train at least one GDDR6 controller. The header file /include/Achronix\_GDDR6.h specifies the register control block addresses for the ADM. These addresses should be modified to match the fabric design.

# Achronix\_PCI.cpp

The PCIe functions require at least one PCIe core to be enabled and configured within the device. Normally (on a VectorPath card) this is PCIE\_1 which connects to the primarily PCIe connector. In addition, the functions require one BAR that maps to the PCIe core registers. If DMA transfers are required to GDDR6 or DDR4, the appropriate training blocks for these interfaces must be instantiated within the fabric and suitable control must be available to ensure that the interfaces are correctly initialized and ready for read and write operations before any DMA or PCIe BAR access is made. See the functions above for control and monitoring of these external memories.

If DMA descriptors are required to be stored in a BRAM attached to a NAP, for internal fast storage, an axi bram responder instance is required in the fabric.

# DMA\_example.cpp

The DMA example code has the same requirements as Achronix\_PCI.cpp in that a single core must be present and configured, and that any external memory interfaces have been correctly initialized before use.

# Chapter - 5: SDK Functions

The SDK library includes the following functions. Function prototypes are defined in <achronix\_SDK>/include /Achronix\_PCI.h.

### Quick Reference Table

A list of all current functions, with their arguments is shown below.

```

// General utility functions

uint64_t util_calc_nap_absolute_addr (PartName part, int col, int row );

void

util wait microseconds

(int num microseconds);

(int num_seconds);

void

util_wait_seconds

// PCIe CSR register access functions

(BwpciDevice *device, BwpciMs csr_bar, uint32_t addr_offset,

pci_reg_write_offset

uint32_t value );

uint32_t pci_reg_read_offset

(BwpciDevice *device, BwpciMs csr_bar, uint32_t addr_offset

);

(BwpciDevice *device, BwpciMs csr_bar, uint32_t addr_offset,

int

pci_reg_set_bits_offset

int start_bit, int stop_bit );

pci_reg_clear_bits_offset

(BwpciDevice *device, BwpciMs csr_bar, uint32_t addr_offset,

int start_bit, int stop_bit );

// PCI specific functions

void

pci_read_reg_ctrl_version

(BwpciDevice *device, BwpciMs reg_ctrl_bar);

bool

(BwpciDevice *device);

pci_link_is_up

// DMA specific functions

dma_build_data_descriptor (DMADataDescriptor *desc, uint32_t size, uint64_t sar,

void

uint64_t dar);

dma_build_link_descriptor (DMALinkDescriptor *desc, uint64_t ptr_phys_addr);

void

int

dma_init

(BwpciDevice *device, BwpciMs csr_bar, PartName part,

PCIeCoreNum core);

void

dma config

(BwpciDevice *device, DmaCommand t &p dma inst);

(BwpciDevice *device, DmaCommand_t &p_dma_inst);

void

dma_start

(BwpciDevice *device, DmaCommand_t &p_dma_inst);

void

dma halt

(BwpciDevice *device, DmaCommand_t &p_dma_inst);

DmaStatus dma_get_status

DmaStatus dma_wait

(BwpciDevice *device, DmaCommand_t &command, int

timeout_in_seconds);

// ATU specific functions

atu_get_context

(BwpciDevice *device, BwpciMs csr_bar, PCIeCoreNum

pcie_core, ATUContext &context);

(BwpciDevice *device, BwpciMs csr_bar, PCIeCoreNum

atu_find_regions

pcie_core, int bar_num, std::vector<ATURegion> &regions);

(BwpciDevice *device, BwpciMs csr_bar, PCIeCoreNum

atu_get_region

pcie_core, int region_num, ATURegion &region);

atu_put_region

(BwpciDevice *device, BwpciMs csr_bar, PCIeCoreNum

pcie_core, ATURegion &region);

```

# util\_calc\_nap\_absolute\_addr()

# Description

Calculate the absolute 42-bit address of a NAP, placed in the NoC, given the row and column coordinates. This function is primarily intended for use when a DMA transfer is required between a NAP and a host using absolute addresses. The source code for this function is available in /src/Achronix\_PCI.cpp.

#### Call

uint64\_t util\_calc\_nap\_absolute\_addr (PartName part, int col, int row );

# **Arguments**

| Туре     | Argument | Description                                         |

|----------|----------|-----------------------------------------------------|

| Partname | part     | Device partname. Supported values are AC7t1500ES0.  |

| int      | col      | Column address. Column values start from 1 (not 0). |

| int      | row      | Row address. Row values start from 1 (not 0).       |

# Return Value

The function returns the absolute NoC 42-bit address of the NAP.

# util\_wait\_microseconds()

# Description

Non-blocking function to sleep for a defined number of microseconds, ( $\mu$ S). The source code for this function is available in /src/Achronix\_PCI.cpp.

### Call

void util\_wait\_microseconds (int num\_microseconds);

# Arguments

| Туре | Argument         | Description                      |

|------|------------------|----------------------------------|

| int  | num_microseconds | Number of microseconds to sleep. |

### Return Value

The function has no return value.

# util\_wait\_seconds()

# Description

Non-blocking function to sleep for a defined number of seconds. The source code for this function is available in /src/Achronix\_PCI.cpp.

### Call

void util\_wait\_seconds (int num\_seconds);

# Arguments

| Туре | Argument    | Description                 |

|------|-------------|-----------------------------|

| int  | num_seconds | Number of seconds to sleep. |

### Return Value

The function returns the absolute NoC 42-bit address of the NAP.

# pci\_reg\_write\_offset()

# Description

Write to a register in the device, using a 32-bit offset to the required PCIe BAR region

#### Call

int pci\_reg\_write\_offset (BwpciDevice \*device, BwpciMs csr\_bar, uint32\_t

addr\_offset, uint32\_t value );

# **Arguments**

| Туре         | Argument        | Description                                                                                                                           |

|--------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| BwpciDevice* | device          | Pointer to the PCIe device.                                                                                                           |

| BwpciMs      | csr_bar         | PCIe BAR that references the register location. This must be the BAR set to the Configuration Status Registers in the PCIe DBI space. |

| uint32_t     | addr_offset (1) | 32-bit offset to the BAR base address.                                                                                                |

| uint32_t     | value           | Value to be written to the register.                                                                                                  |

#### **Table Notes**

1. Currently there is a restriction with the PCIe BAR size to 64MB. Therefore, addr\_offset is limited to a maximum value of 0x03ff\_ffff.

### Return Value

The function returns a positive value indicating the number of 32-bit writes (1) if it completed successfully. Returns a negative value if unsuccessful.

# pci\_reg\_read\_offset()

# Description

Write to a register in the device, using a 32-bit offset to the required PCIe BAR region.

### Call

uint32\_t pci\_reg\_read\_offset (PCIDevice &device, BwpciMs csr\_bar, uint32\_t

addr\_offset);

# **Arguments**

| Туре         | Argument    | Description                                                                                                                           |  |

|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| BwpciDevice* | device      | Pointer to the PCIe device.                                                                                                           |  |

| BwpciMs      | csr_bar     | PCIe BAR that references the register location. This must be the BAR set to the Configuration Status Registers in the PCIe DBI space. |  |

| uint32_t     | addr_offset | 32-bit offset to the BAR base address.                                                                                                |  |

#### **Table Notes**

1. Currently there is a restriction with the PCIe BAR size to 64MB. Therefore, addr\_offset is limited to a maximum value of 0x03ff\_ffff.

### Return Value

The function returns the 32-bit value of the register.

# pci\_reg\_set\_bits\_offset()

# Description

Set a range of bits in a register in the device to 1 'b1, using a 32-bit offset to the required PCle BAR region. The function performs a read-modify-write sequence on the register.

### Call

int pci\_reg\_set\_bits\_offset (BwpciDevice \*device, BwpciMs csr\_bar, uint32\_t

addr\_offset, int start\_bit, int stop\_bit);

# **Arguments**

| Туре         | Argument        | Description                                                                                                                           |  |

|--------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| BWpciDevice* | device          | Pointer to the PCIe device.                                                                                                           |  |

| BwpciMs      | csr_bar         | PCIe BAR that references the register location. This must be the BAR set to the Configuration Status Registers in the PCIe DBI space. |  |

| uint32_t     | addr_offset (1) | 32-bit offset to the BAR base address.                                                                                                |  |

| int          | start_bit       | Highest bit to be set. Must be in the range 0–31. Must be >= stop_bit.                                                                |  |

| int          | stop_bit        | Lowest bit to be set. Must be in the range 0–31. Must be <= stop_bit.                                                                 |  |

#### **Table Notes**

1. Currently there is a restriction with the PCle BAR size to 64MB. Therefore, addr\_offset is limited to a maximum value of 0x03ff\_ffff.

### Return Value

The function returns a positive value indicating the number of 32-bit writes (1) if it completed successfully. Returns a negative value if unsuccessful.

# pci\_reg\_clear\_bits\_offset()

# Description

Clear a range of bits in a register in the device to 1 'b0, using a 32-bit offset to the required PCle BAR region. The function performs a read-modify-write sequence on the register.

### Call

int pci\_reg\_clear\_bits\_offset (BwpciDevice \*device, BwpciMs csr\_bar, uint32\_t

addr\_offset, int start\_bit, int stop\_bit);

# **Arguments**

| Туре         | Argument        | Description                                                                                                                           |  |

|--------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| BwpciDevice* | device          | Pointer to the PCIe device.                                                                                                           |  |

| BwpciMs      | csr_bar         | PCIe BAR that references the register location. This must be the BAR set to the Configuration Status Registers in the PCIe DBI space. |  |

| uint32_t     | addr_offset (1) | 32-bit offset to the BAR base address.                                                                                                |  |

| int          | start_bit       | Highest bit to be cleared. Must be in the range 0–31. Must be >= stop_bit.                                                            |  |

| int          | stop_bit        | Lowest bit to be cleared. Must be in the range 0-31. Must be <= stop_bit.                                                             |  |

#### **Table Notes**

1. Currently there is a restriction with the PCle BAR size to 64MB. Therefore, addr\_offset is limited to a maximum value of 0x03ff\_ffff.

### Return Value

The function returns a positive value indicating the number of 32-bit writes (1) if it completed successfully. Returns a negative value if unsuccessful.

# pci\_read\_reg\_ctrl\_version()

# Description

Utility function to display the values of the version registers within a register control block.

### Call

void pci\_read\_reg\_ctrl\_version (BwpciDevice \*device, BwpciMs reg\_ctrl\_bar);

# Arguments

| Туре         | Argument     | Description                                          |

|--------------|--------------|------------------------------------------------------|

| BwpciDevice* | device       | Pointer to the PCIe device.                          |

| BwpciMs      | reg_ctrl_bar | PCIe BAR that references the register control block. |

### Return Value

The function returns 0.

# pci\_link\_is\_up()

# Description

Utility function to indicate if the PCIe device is correctly enumerated and available for access. The function confirms that the Vendor ID register returns the expected value.

### Call

bool pci\_link\_is\_up (BwpciDevice \*device);

# Arguments

| Туре         | Argument | Description                 |  |

|--------------|----------|-----------------------------|--|

| BwpciDevice* | device   | Pointer to the PCIe device. |  |

### Return Value

The function returns true if the PCIe core responds correctly, or false if an error is detected.

# dma\_build\_data\_descriptor()

# Description

Populates a DMA data descriptor in a DMADescriptorList. Used for linked-list-mode DMA operation. The source code for this function is available in <achronix\_SDK>/src/Achronix\_PCI.cpp.

#### Call

void dma\_build\_data\_descriptor (DMADataDescriptor \*desc, uint32\_t size, uint64\_t

sar, uint64\_t dar);

# Arguments

| Туре                     | Argument | Description                                         |

|--------------------------|----------|-----------------------------------------------------|

| DMADataDescriptor*(1)(2) | desc     | Pointer to the descriptor.                          |

| uint32_t                 | size     | Size of the transfer in bytes.                      |

| uint64_t                 | sar      | Source address (can be either host or device).      |

| uint64_t                 | dar      | Destination address (can be either host or device). |

#### **Table Notes**

- 1. The descriptor must have already been defined, normally as part of a DMADescriptorList.

- 2. The direction of the DMA transfer is not defined in the descriptor. The direction is set by dma\_config(). It is therefore important that sar and dar are set correctly in every descriptor with respect to host and device addresses to be consistent with the subsequent direction set by dma\_config().

### Return Value

The function does not have a return value.

## dma\_build\_link\_descriptor()

### Description

Populates the DMA link descriptor that terminates each <code>DMADescriptorList</code>. Used for linked-list DMA operation. The <code>DMALinkDescriptor</code> that terminates each <code>DMADescriptorList</code> is filled in by the <code>DMADescriptorList</code> constructor to point back to the first descriptor in list list. This function is only needed when building multiple linked sets of <code>DMADescriptorLists</code>. The source code for this function is available in <code>/src/Achronix\_PCI.cpp</code>.

#### Call

void dma\_build\_link\_descriptor (DMALinkDescriptor \*desc, uint64\_t ptr\_phys\_addr);

### Arguments

| Туре                      | Argument      | Description                                                                                                                                                                                                                                                                                    |

|---------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMALinkDescriptor* (1)(2) | desc          | Pointer to the descriptor.                                                                                                                                                                                                                                                                     |

| uint64_t                  | ptr_phys_addr | Start address of the next block of link-list descriptors.  If the start of the current block of descriptors is used, this address acts as an end-of-list for the current linked list. Causes DMA to complete.  Defined as device absolute physical address within the 42-bit NoC memory space. |

#### **Table Notes**

- 1. The descriptor must have already been defined, normally as part of a DMADescriptorList.

- 2. The direction of the DMA transfer is not defined in the descriptor. The direction is set by dma\_config(). It is therefore important that sar and dar are set correctly in every descriptor with respect to host and device addresses to be consistent with the subsequent direction set by dma\_config().

#### Return Value

## dma\_init()

## Description

Initializes the PCIe DMA engine. Sets the arbitration weights for each of the four DMA channels to the same value. Must be called at least once before any DMA transactions are initiated.

#### Warning

Normally, this function should only be called once during program execution. Calling this during DMA operation could cause the core to enter an unknown state.

#### Call

int dma\_init (BwpciDevice \*device, BwpciMs csr\_bar, PartName part, PCIeCoreNum

core);

### Arguments

| Туре         | Argument | Description                                                                   |

|--------------|----------|-------------------------------------------------------------------------------|

| BwpciDevice* | device   | Pointer to the PCIe device.                                                   |

| BwpciMs      | csr_bar  | BAR that references the Configuration Status Registers in the PCIe DBI space. |

| PartName     | part     | Device partname. Currently the only supported option is AC7t1500ES0.          |

| PCIeCoreNum  | core     | Selects the appropriate PCle core. Options are PCIE_0 and PCIE_1.             |

### Return Value

The function returns 0.

## dma\_config()

## Description

Configure the PCIe DMA for a transfer. The DmaCommand structure passed to this function contains the source and destination addresses, the size of the transfer and the direction. Alternately, if link-lists are being used, the structure includes the address of the start of the linked list in the device 42-bit NoC address space.

#### Note

This function does not start a DMA transfer.

#### Call

void dma\_config (BwpciDevice \*device, DmaCommand &dma\_command);

## Arguments

| Туре         | Argument    | Description                        |

|--------------|-------------|------------------------------------|

| BwpciDevice* | device      | Pointer to the PCIe device.        |

| DmaCommand&  | dma_command | Reference to a DMA command struct. |

### Return Value

# dma\_start()

## Description

Starts a DMA transfer previously configured with dma\_config().

#### Call

void dma\_start (BwpciDevice \*device, DmaCommand &dma\_command);

## Arguments

| Туре         | Argument    | Description                                                                                                   |

|--------------|-------------|---------------------------------------------------------------------------------------------------------------|

| BwpciDevice* | device      | Pointer to the PCIe device.                                                                                   |

| DmaCommand&  | dma_command | Reference to the DMA command struct. This command struct must have been previously processed by dma_config(). |

### Return Value

## dma\_halt()

## Description

Halts the currently running PCIe DMA transfers defined by the DMA command instance. Use this only if the DMA transaction has timed out and needs to be aborted.

### Call

void dma\_halt (BwpciDevice \*device, DmaCommand &dma\_command);

## Arguments

| Туре         | Argument    | Description                 |

|--------------|-------------|-----------------------------|

| BwpciDevice* | device      | Pointer to the PCIe device. |

| DmaCommand&  | dma_command | Reference to a DMA command. |

### Return Value

# dma\_get\_status()

## Description

Get the status of the currently running PCIe DMA defined by the DMA command structure.

#### Call

DmaStatus dma\_get\_status (BwpciDevice \*device, DmaCommand &dma\_command);

## **Arguments**

| Туре         | Argument    | Description                        |

|--------------|-------------|------------------------------------|

| BwpciDevice* | device      | Pointer to the PCIe device.        |

| DmaCommand&  | dma_command | Reference to a DMA command struct. |

### Return Value

The function returns one of the values for DMA status defined in the DmaStatus enum.

## dma\_wait()

### Description

Begins polling the status of a currently running DMA transfer, initiatied with <code>dma\_start()</code>, at a set interval, and return to the caller when the transfer is complete.

#### Note

This function is multi-threaded and non-blocking.

#### Call

DmaStatus dma\_wait (BwpciDevice \*device, DmaCommand &dma\_command, int timeout\_in\_seconds);

### **Arguments**

| Туре         | Argument           | Description                                                                                                                                           |

|--------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| BwpciDevice* | device             | Pointer to the PCIe device.                                                                                                                           |

| DmaCommand&  | command            | Reference to a DMA command struct.                                                                                                                    |

| int          | timeout_in_seconds | Maximum time to wait for DMA to complete. If timeout_in_seconds is exceeded, the function returns to the calling function with an error return value. |

### Return Value

The function returns one of the predefined values for DmaStatus as defined in Acxronix\_PCI.h. If the status is not  $acxsdk::DMA\_COMPLETE$ , then the transaction did not complete successfully. Call  $dma\_halt()$  to force the currently running transaction to end correctly.

## atu\_get\_context()

## Description

Returns the complete context (configuration register values) of the Address Translation Unit. Results are returned in the ATUContext class, which is a vector of 100 ATURegion classes. This function can be used to view the current ATU configuration, and then modify it with the atu\_put\_region() function.

#### Call

atu\_get\_context (BwpciDevice \*device, BwpciMs csr\_bar, PCIeCoreNum core,

ATUContext &context);

## **Arguments**

| Туре         | Argument | Description                                                                                                           |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------|

| BwpciDevice* | device   | Pointer to the PCIe device.                                                                                           |

| BwpciMs      | csr_bar  | BAR that references the Configuration Status Registers in the PCIe DBI space.                                         |

| PCIeCoreNum  | core     | Selects the appropriate PCIe core. Options are PCIE_0 and PCIE_1.                                                     |

| ATUContext&  | context  | A reference to an ATUContext class to be filled in with the current values of all of the ATU configuration registers. |

#### Return Value

# atu\_find\_regions()

## Description

Finds all regions that cover a given BAR and returns their context in a vector of ATURegion classes.

#### Call

atu\_find\_region (BwpciDevice \*device, BwpciMs csr\_bar, PCIeCoreNum core, int bar\_num, std::vector<ATURegion> &regions);

### Arguments

| Туре                                         | Argument | Description                                                                   |

|----------------------------------------------|----------|-------------------------------------------------------------------------------|

| BwpciDevice*                                 | device   | Pointer to the PCIe device.                                                   |

| BwpciMs                                      | csr_bar  | BAR that references the Configuration Status Registers in the PCIe DBI space. |

| PCIeCoreNum                                  | core     | Selects the appropriate PCIe core. Options are PCIE_0 and PCIE_1.             |

| int                                          | bar_num  | Integer index (0-5) of the BAR number to be found.                            |

| std::<br>vector <aturegion>&amp;</aturegion> | regions  | A reference to a vector of all ATURegions that cover BAR number bar_num.      |

#### Return Value

# atu\_get\_region()

## Description

Gets a given ATU region, and returns its context in an ATURegion class.

#### Call

atu\_get\_region (BwpciDevice \*device, BwpciMs csr\_bar, PCIeCoreNum pcie\_core, int

region\_num, ATURegion &region);

## Arguments

| Туре         | Argument   | Description                                                                                               |  |

|--------------|------------|-----------------------------------------------------------------------------------------------------------|--|

| BwpciDevice* | device     | Pointer to the PCIe device.                                                                               |  |

| BwpciMs      | csr_bar    | BAR that references the Configuration Status Registers in the PCIe DBI space.                             |  |

| PCIeCoreNum  | pcie_core  | Selects the appropriate PCle core. Options are PCIE_0 and PCIE_1.                                         |  |

| int          | region_num | The index (0-99) of the region to be returned.                                                            |  |

| ATURegion&   | region     | A reference to an ATURegion class to be filled in with the context of the region specified by region_num. |  |

## Return Value

# atu\_put\_region()

## Description

Modifies the ATU configuration registers of a given region using the context specified in a given ATURegion class.

### Call

atu\_put\_region (BwpciDevice \*device, BwpciMs csr\_bar, PCIeCoreNum pcie\_core,

ATURegion &region);;

## **Arguments**

| Туре         | Argument   | Description                                                                                                                                   |  |

|--------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| BwpciDevice* | device     | Pointer to the PCIe device.                                                                                                                   |  |

| BwpciMs      | csr_bar    | BAR that references the Configuration Status Registers in the PCIe DBI space.                                                                 |  |

| PCIeCoreNum  | region_num | The index (0-99) of the region to be configured.                                                                                              |  |

| ATURegion&   | region     | A reference to an ATURegion class. The context of the class is copied into the configuration registers of the region specified by region_num. |  |

### Return Value

## Chapter - 6: SDK Structures

### DmaCommand\_t

## Description

The DmaCommand\_t structure is used to specify the parameters of a DMA transaction when calling dma\_config() and dma\_start(). The structure can be used in two modes: normal and linked-list. In normal mode, all of the parameters are directly specified in the DmaCommand, hence the device\_address, host\_address, and size\_in\_bytes fields are populated and the descriptor\_list\_address is set to NULL. In linked-list mode those three parameters are read from the descriptors, so device\_address, host\_address, and size\_in\_bytes are set to NULL and the descriptor\_list\_address element is populated. See the DMA example source code for more information.

#### Definition

```

struct DmaCommand_t {

BwpciMs

csr_bar;

PCIeCoreNum

pcie_core;

DmaDir

dma_direction;

int

dma_channel;

uint64_t

device_address;

uint64 t

host address;

uint64_t

size_in_bytes;

uint64_t

descriptor_list_address;

bool

verbosity;

};

```

#### **Fields**

| Туре        | Parameter      | Description                                                                                                                      |

|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------|

| BwpciMs     | csr_bar        | A handle to a BAR register mapped to the base of CSR space in the 42-bit NoC address space.                                      |

| PCIeCoreNum | pcie_core      | An enum that specifies which PCIe core is being programmed. Normally, this is PCIE_1 which is the core connected to the host PC. |

| DmaDir      | dma_direction  | An enum describing the transfer direction. Either HOST_TO_DEVICE (a read) or DEVICE_TO_HOST (a write).                           |

| int         | dma_channel    | Specifies which of the DMA channels to program. The Speedster7t FPGA has four independent full-duplex channels (0-3).            |

| uint64_t    | device_address | The 42-bit base address for the transfer on the device side (normal mode only).                                                  |

### Software Development Kit User Guide (UG107)

| Туре     | Parameter               | Description                                                                                                                               |

|----------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| uint64_t | host_address            | The 64-bit address for the transfer on the host side. This must be the physical (not virtual) address of a DMA buffer (normal mode only). |

| uint64_t | size_in_bytes           | The size of the transfer specified as the number of bytes (normal mode only).                                                             |

| uint64_t | descriptor_list_address | The 42-bit base address of a DMA data descriptor (linked-list mode only).                                                                 |

| bool     | verbosity               | Setting this flag to a non-zero value increases the amount of verbose output debug information.                                           |

# DMADataDescriptor

## Description

This struct consists of six 32-bit parameters specifying the meta-parameters for a DMA transaction. The parameters can be allocated in blocks of contiguous descriptors using the <code>DMADescriptorList</code> class described below.

### Definition

```

struct DMADataDescriptor {

uint32_t control;

uint32_t size;

uint32_t sar_low;

uint32_t sar_high;

uint32_t dar_low;

uint32_t dar_high;

};

```

#### **Fields**

| Туре     | Parameter | Description                                                                                                |  |

|----------|-----------|------------------------------------------------------------------------------------------------------------|--|

| uint32_t | control   | A 32-bit control register. Only bits [4:0] are currently in use. See the file Achronix_PCI. cpp for usage. |  |

| uint32_t | size      | The size of the transaction specified as the number of bytes.                                              |  |

| uint32_t | sar_low   | The lower 32 bits of the DMA source address.                                                               |  |

| uint32_t | sar_high  | The upper 32 bits of the DMA source address.                                                               |  |

| uint32_t | dar_low   | The lower 32 bits of the DMA destination address.                                                          |  |

| uint32_t | dar_high  | The upper 32 bits of the DMA destination address.                                                          |  |

## **DMALinkDescriptor**

## Description

This struct consists of six 32-bit parameters used in DMA linked-list mode. When allocating a block of descriptors using a DMADescriptorList class (described below), the last descriptor in a contiguous block must be a link descriptor. The ptr field in a link descriptor points to the first descriptor in a neighboring descriptor list. The last link descriptor list in a linked-list should point back to the beginning of the first data descriptor in the list. The DMALinkDescriptor struct is the same size as the DMADataDescriptor, however three of the 32-bit fields are unused.

#### Definition

```

struct DMALinkDescriptor {

uint32_t control;

uint32_t unused_0;