# Copyrights, Trademarks and Disclaimers

Copyright © 2018 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedcore, Speedster, and ACE are trademarks of Achronix Semiconductor Corporation in the U.S. and/or other countries All other trademarks are the property of their respective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

#### **Achronix Semiconductor Corporation**

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail: info@achronix.com

# Table of Contents

| Chapter - 1: Overview                                                                                 | 6  |

|-------------------------------------------------------------------------------------------------------|----|

| Chapter - 2: Snapshot General Description                                                             | 7  |

| Features                                                                                              | 7  |

| Triggers Trigger Examples                                                                             |    |

| Names.snapshot                                                                                        | 10 |

| Chapter - 3: Snapshot Interface                                                                       |    |

| Snapshot Macros                                                                                       |    |

| JTAG Pins                                                                                             |    |

| Snapshot User Port List                                                                               | 12 |

| Snapshot Parameter List                                                                               | 14 |

| Startup Trigger Parameters                                                                            | 15 |

| Parameter Impact on Core Logic Utilization                                                            | 16 |

| Snapshot Verilog Interface                                                                            | 17 |

| Snapshot VHDL Interface                                                                               | 18 |

| Chapter - 4: Snapshot Example                                                                         | 20 |

| Clock Constraints (SDC File)                                                                          | 21 |

| Example Verilog RTL                                                                                   | 21 |

| Chapter - 5: Probing in a Hierarchical Design                                                         | 25 |

| Overview                                                                                              |    |

| Example                                                                                               | 26 |

| Chapter - 6: Running the Snapshot User Interface                                                      | 31 |

| Accessing the Snapshot Debugger  Open the ACE GUI and Select Your Project  Open the Snapshot Debugger | 32 |

| Configuring the Trigger Pattern  Configuring the Trigger Mode  Configuring Trigger Patterns           | 34 |

| 0000                                                                                                  |    |

|   | Configuring the Monitor Signals                                                                                            |                      |

|---|----------------------------------------------------------------------------------------------------------------------------|----------------------|

|   | Configuring the Test Stimuli  Setting Stimuli Values Using the Table  Setting Multiple Stimuli Values as a Bus             | . 39                 |

|   | Configuring Advanced Options Pre-Store Trigger Pattern Match Behavior User Clock Frequency Configure output file locations | . 41<br>. 42<br>. 42 |

|   | Collecting Samples of the User Design                                                                                      | . 43                 |

|   | Saving/Loading Snapshot Configurations                                                                                     | . 44                 |

|   | Running Snapshot in Batch Mode                                                                                             | . 45                 |

| F | Revision History                                                                                                           | 48                   |

## Chapter - 1: Overview

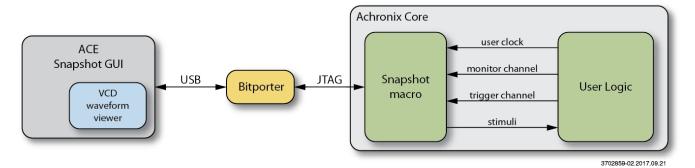

Snapshot is the real-time design debugging tool for Achronix FPGAs and cores. The Snapshot debugger, which is embedded in the ACE software, delivers a practical platform to observe the signals of a user's design in real-time. To use the Snapshot debugger, the Snapshot macro needs to be instantiated inside the user's RTL. After instantiating the macro and programming the device, the user will be able to debug the design through the Snapshot Debugger GUI within ACE, or via the run\_snapshot TCL command API.

The Snapshot macro can be connected to any logic signal mapped to the Achronix core, to monitor and potentially trigger on that signal. Monitored signal data is collected in real time in regular BRAMs, prior to being transferred to the ACE Snapshot GUI. The Snapshot macro has configurable monitor width and depth, as well as other configuration parameters, to allow user control over resource usage. The ACE Snapshot GUI interacts with the hardware via the JTAG interface: interactively specified trigger conditions are transferred to the design, and collected monitor data is transferred back to the GUI, which displays the data using a builtin waveform viewer.

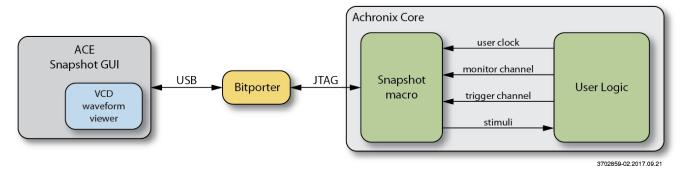

The figure below shows the components involved in a Snapshot debug session.

Figure 1: Snapshot Overview

## Chapter - 2: Snapshot General Description

#### **Features**

The Snapshot macro samples user signals in real time, storing the captured data in one or more BRAMs. The captured data is then communicated through the JTAG interface to the ACE Snapshot GUI.

The implementation supports the following features:

- Monitor channel capture width of 1 to 4064 bits of data.

- Monitor channel capture depth of 512 to 16384 samples of data at the user clock frequency.

- Trigger channel width of 1 to 40 bits.

- Supports up to three separate sequential trigger conditions. Each trigger condition allows for the selection

of a subset of the trigger channel, with AND or OR functionality.

- Bit-wise support for edge- (rise/fall) or level-sensitive triggers.

- The ACE Snapshot GUI allows specification of trigger conditions and circuit stimuli at runtime.

- An optional initial trigger condition, specified in RTL parameters, to allow capture of data immediately after startup, before interaction with the ACE Snapshot GUI.

- A stimuli interface, 0 to 512 bits wide, that allows the user to drive values into the Achronix core logic from Snapshot. Stimuli values are specified with the ACE Snapshot GUI and made available before data capture.

- Optionally, the data capture can include values before the trigger occurred. This "pre-store" amount can be specified in increments of 25% of the depth.

- Captured data is saved in a standard VCD waveform file. The ACE Snapshot GUI includes a waveform viewer for immediate feedback.

- The VCD waveform file includes a timestamp for when the Snapshot was taken.

- ACE automatically extracts the names of the monitored signals from the netlist, for easy interpretation of the waveform.

- A repetitive trigger mode, in which repeated Snapshots are taken and collected in the same VCD file.

- The JTAG interface can be shared with the user design.

- A TCL batch/script mode interface is provided via the run\_snapshot TCL command

## **Triggers**

The Snapshot macro has a trigger channel input with a width from 1 to 40 bits. Any subset of these inputs can be used to trigger a Snapshot. While the set of potential trigger bits is determined at design time, the choice of actual trigger condition is made at runtime using the ACE Snapshot GUI. All monitor and trigger inputs are sampled at the rising edge of user\_clk. Trigger conditions are evaluated based on these sampled values.

A trigger condition specifies one of the following for each of the trigger input bits:

- don't-care ("X") the value of the bit is ignored

- 0 the bit matches if the input is 0

- 1 the bit matches if the input is 1

- rising edge ("R") the bit matches when it changes from 0 to 1 in consecutive samples

- falling edge ("F") the bit matches when it changes from 1 to 0 in consecutive samples

Each bit is evaluated independently to determine whether it is a match or not. The results are then either ANDed (all bits, except don't-cares, must match at the same time) or ORed (the trigger matches if any bit matches).

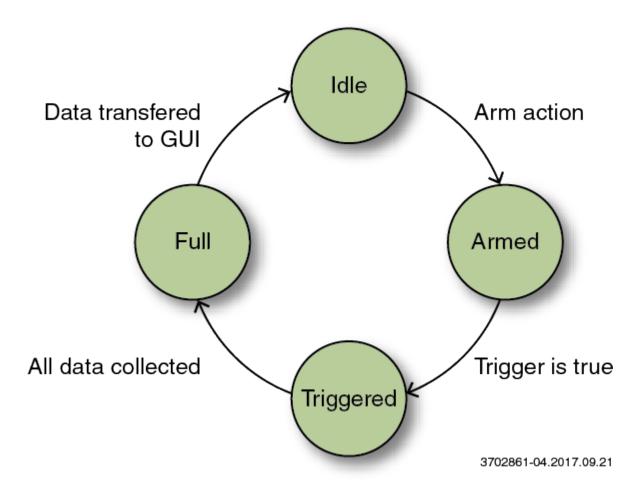

A simple state diagram for Snapshot is shown below. The arm action is initiated from the ACE Snapshot GUI (after specifying the trigger conditions). When armed, Snapshot waits for the trigger condition to become true. Once triggered, monitor data is collected until the internal buffer is filled. The trigger point is always part of the Snapshot waveform, but if requested, a certain amount of pre-store data preceding the trigger point is collected as well. This storage is useful for seeing the events leading up to the trigger occurrence.

Figure 2: State Transitions of Snapshot Macro

Up to three sequential trigger conditions can be specified. Snapshot waits until the first trigger condition evaluates to true. Once that occurs, it waits for the second condition, etc. The earliest time at which the second trigger can be detected is the clock cycle following the occurrence of the first trigger. The occurrence of the last condition is the Snapshot trigger point, at which the state changes to "triggered". The final trigger point is always part of the Snapshot waveform, but whether the earlier triggers are part of the waveform depends on the prestore amount.

# Trigger Examples

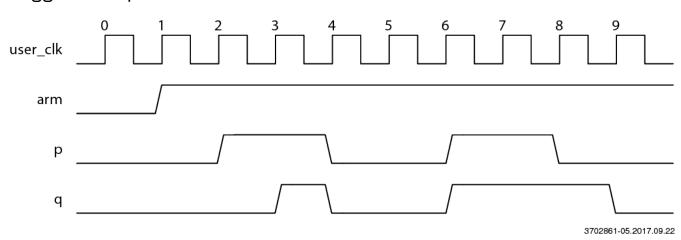

Figure 3: Trigger Example Waveform

The above waveform shows two user signals, p and q. The table below gives several examples of trigger conditions, with the time of the corresponding trigger point. Unless otherwise specified, assume only one trigger condition is specified, and all unmentioned trigger signals are "X". Snapshot is armed at time t= 1.

**Table 1: Trigger Examples**

| Trigger Condition                              | Trigger<br>Point | Explanation                                                                                                                                |

|------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| p=X and q=X                                    | 1                | The trigger condition with all signals X (don't-care) is always true. This condition is equivalent to "immediate mode" in the Snapshot GUI |

| p=0 and q=0                                    | 1                |                                                                                                                                            |

| p=1 and q=1                                    | 3                | Note that the trigger point is the time at which the condition becomes true, not the time at which a flop might sample the condition.      |

| p=R and q=R                                    | 6                | Rising edge triggers. Although p = R occurs at t = 2 and q = R at t = 3, they only occur simultaneously at t = 6.                          |

| p=R and q=0                                    | 2                |                                                                                                                                            |

| p=R and q=1                                    | 6                |                                                                                                                                            |

| p=1 or q=1                                     | 2                |                                                                                                                                            |

| trigger1: p=1 and q=1<br>trigger2: p=0 and q=0 | 4                | Trigger1 occurs at t = 3, then trigger2 occurs at t = 4. The latter is the trigger point.                                                  |

| trigger1: p=1 and q=1<br>trigger2: p=1 and q=1 | 6                | The trigger point is not $t=3$ , because trigger2 must occur after trigger1, nor is $t=4$ because that matches $p=0$ and $q=0$ .           |

| Trigger Condition                              | Trigger<br>Point | Explanation                                                                                        |

|------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------|

| trigger1: p=1 and q=1<br>trigger2: p=X and q=X | 4                | The trigger point is not t = 3, because trigger2, while trivially true, must occur after trigger1. |

## Names.snapshot

The Snapshot macro connects to the user design with buses i\_monitor, i\_trigger, and i\_stimuli. However, it would be cumbersome to debug a design if all signals were referred to as simply i\_monitor[0], i\_monitor[1], etc. Therefore, during the ACE "prepare" flow step, ACE analyzes the netlist to determine the user's signal names. The result is saved in a Snapshot configuration file, names.snapshot. The Snapshot GUI loads this configuration file automatically if there is an active project.

Because the name extraction occurs after RTL synthesis, sometimes names may have been modified by Synplify. It may help to use the syn\_preserve or syn\_keep synthesis attributes to prevent names from being changed. The ACE Snapshot GUI also enables editing of the signal names and has buttons to load and save configuration files.

# Chapter - 3: Snapshot Interface

## **Snapshot Macros**

There are two variants of the Snapshot macro, ACX\_SNAPSHOT and ACX\_SNAPSHOT\_UNIT. Both variants have the same interface to the user design, but differ in the way they connect to the JTAG interface. Most designs will simply use ACX\_SNAPSHOT. However, designs that already use the JTAG TAP Controller Functions for other reasons, should use ACX\_JTAP\_UNIT instead to allow sharing of the JTAG interface between Snapshot and the user design.

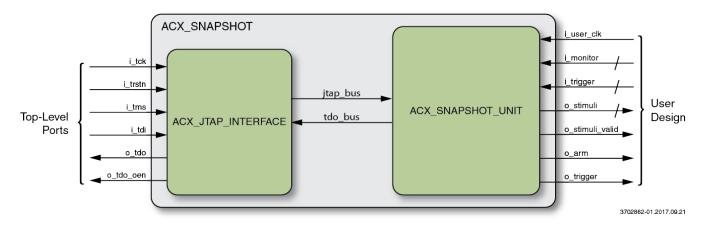

The figure below shows the relation between ACX\_SNAPSHOT and ACX\_SNAPSHOT\_UNIT, as well as the interface ports.

Figure 4: Snapshot Macro Block Diagram

## **JTAG Pins**

The JTAG interface pins of ACX\_SNAPSHOT map directly to hardware pins. In the user design, these must connect to top-level ports of the RTL *without* insertion of IPINs or OPINs (for a Speedcore instance), or pads (for Speedster FPGAs).

| Table 2: JTAG Pin Description for ACX_SNAPSHOT |

|------------------------------------------------|

|------------------------------------------------|

| Pin Name | Туре  | Description                  |

|----------|-------|------------------------------|

| i_tck    | Input | JTAG test clock              |

| i_trstn  | Input | JTAG test reset (active low) |

| i_tdi    | Input | JTAG test data in            |

| i_tms    | Input | JTAG test mode select        |

| Pin Name                 | Туре   | Description                        |

|--------------------------|--------|------------------------------------|

| o_tdo                    | Output | JTAG test data out                 |

| o_tdo_oen <sup>(†)</sup> | Output | Active-low output enable for o_tdo |

#### **Table Note**

† The signal o\_tdo\_oen only exists in Speedcore products to be combined with o\_tdo to drive a tri-state pad. Achronix stand-alone FPGAs already include the tri-state pad as driver of o\_tdo.

ACX\_SNAPSHOT\_UNIT has the same user interface as ACX\_SNAPSHOT, but allows the sharing of the JTAG interface with the user design through the JTAG TAP controller functions. This functionality is described in more detail in the "JTAG TAP Controller Functions" of *Speedcore IP Component Library User Guide* (UG065) or the *Speedster22i Macro Cell Library* (UG021).

Table 3: JTAP Pin Description for ACX\_SNAPSHOT\_UNIT

| Pin<br>Name | Туре   | Description                                                                                                             |

|-------------|--------|-------------------------------------------------------------------------------------------------------------------------|

| i_jtap_bus  | Input  | Input from ACX_JTAP_INTERFACE (of type jtap_bus_tp) shared with other ACX_JTAP_UNIT instances.                          |

| i_tdo_bus   | Input  | Input matching the o_tdo_bus output of an ACX_JTAP_UNIT instance to allow the chaining of units. Tie low when not used. |

| o_tdo_bus   | Output | Output to drive i_tdo_bus of ACX_JTAP_UNIT or ACX_JTAP_INTERFACE.                                                       |

## Snapshot User Port List

The Snapshot user side interface consists of the pins that connect directly to the user design to be monitored. This interface is identical for ACX\_SNAPSHOT and ACX\_SNAPSHOT\_UNIT.

**Table 4: Pin Descriptions of Snapshot Macro**

| Pin Name                     | Туре  | Description                                                                                                                                                                                    |

|------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i_monitor[MONITOR_WIDTH-1:0] | Input | 1–4064 bit monitor channel. These input signals can be any signal present in the user design. They are captured when a trigger occurs and their values stored in the output VCD waveform file. |

| Pin Name                                    | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i_trigger[TRIGGER_WIDTH-1:0]                | Input  | 1–40 bit trigger channel. These inputs can be used to trigger a capture event (the trigger condition is specified at runtime using these signals). This input is used and must be connected to the user design logic if the STANDARD_TRIGGERS parameter is set to 0. If STANDARD_TRIGGERS is 1, the input i_trigger is ignored, and the Snapshot trigger detect logic is connected internally to i_monitor [TRIGGER_WIDTH-1:0]. |

| i_user_clk                                  | Input  | User clock (same as user design clock). All monitor and trigger inputs are sampled at the rising edge of this clock. This clock must be running for Snapshot to work, and the design must meet timing with respect to this clock.                                                                                                                                                                                               |

| o_stimuli[STIMULI_WIDTH-1:0] <sup>(†)</sup> | Output | 0–512 bits of test stimuli. The user can drive the value of this bus via the Snapshot GUI when arming Snapshot. These signals can be used as test inputs to the user design. The outputs o_stimuli are only valid when o_stimuli_valid is high; at other times they may change arbitrarily.                                                                                                                                     |

| o_stimuli_valid <sup>(†)</sup>              | Output | Asserted high when the signals o_stimuli are valid and stable. The signal o_stimuli_valid is raised just before a Snapshot capture is started and remains high at least until all data has been captured. This signal will be de-asserted and reasserted again before the next Snapshot capture. The user design can detect the rising edge of o_stimuli_valid to determine when new input stimuli are available.               |

| o_arm <sup>(†)</sup>                        | Output | Asserted high when Snapshot starts waiting for the trigger condition. This signal asserts at least ARM_DELAY cycles after o_stimuli_valid to give the user design time to react to the stimuli.                                                                                                                                                                                                                                 |

| o_trigger <sup>(†)</sup>                    | Output | The output o_trigger is rarely used. It asserts high INPUT_PIPELINING + 5 cycles after the trigger condition occurs. This signal is provided as an optional trigger for external instruments, for example, an oscilloscope. No OUTPUT_PIPELINING is added.                                                                                                                                                                      |

#### **Table Note**

$\dagger$  These outputs are in the i\_user\_clk domain and can be used in the design-under-test (DUT) to create desired events to be observed.

# **Snapshot Parameter List**

These parameters define the size and functionality of Snapshot.

**Table 5: Parameter Definitions**

| Parameter         | Default Value    | Defined Value                                                                                                                                                                                                                                                                                                             |

|-------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DUT_NAME          | "none_specified" | Field provided to the user to help distinguish Snapshot logic instances in different designs. This string is printed in the Snapshot log file whenever a Snapshot capture is taken. Maximum length is 128 characters.                                                                                                     |

| MONITOR_WIDTH     | 40               | Monitor channel width. Sets the number of signals to be monitored by Snapshot. The valid range is 1 to 4064 bits.                                                                                                                                                                                                         |

| MONITOR_DEPTH     | 1024             | The number of consecutive data samples (user_clk cycles) in a single Snapshot, captured from the i_monitor bus. Valid values range from 512 to 16384. The implementation rounds this number up as required by the supported BRAM sizes.                                                                                   |

| TRIGGER_WIDTH     | 40               | Trigger channel width. The valid range is 1 to 40 bits.                                                                                                                                                                                                                                                                   |

| NUM_TRIGGERS      | 3                | The maximum number of sequential triggers to compile into the Snapshot circuit. Setting this parameter to a lower number decreases the Achronix core logic resources needed for Snapshot. During a Snapshot debug session, the user may configure up to NUM_TRIGGERS sequential triggers. Valid values range from 1 to 3. |

| STANDARD_TRIGGERS | 1                | If the STANDARD_TRIGGERS parameter value is set to 1, then the i_trigger input is ignored, and instead i_monitor [TRIGGER_WIDTH-1:0] is used as trigger signals. If the STANDARD_TRIGGERS parameter value is set to 0, then the i_trigger[TRIGGER_WIDTH-1:0] input is used as trigger signals.                            |

| STIMULI_WIDTH     | 20               | Number of stimuli signals output to the user design. The valid range is 0 to 512 bits.                                                                                                                                                                                                                                    |

| INPUT_PIPELINING  | 3                | Adds the specified number of pipeline stages to the i_monitor and i_trigger signals to enable fast i_user_clk speeds. This parameter has no effect on the collected data (the .vcd file), or on the point where the trigger occurs.                                                                                       |

| OUTPUT_PIPELINING | 0                | Adds the specified number of pipeline stages to the o_arm, o_stimuli, and o_stimuli_valid outputs to enable fast i_user_clk speeds. This parameter has no effect on the collected data (the . vcd file), or on the point where the trigger occurs.                                                                        |

| Parameter            | Default Value | Defined Value                                                                                                                                                                                                                                                                               |

|----------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARM_DELAY            | 1             | Delay between assertion of o_stimuli_valid and o_arm. The o_arm output signal indicates when Snapshot starts waiting for the trigger condition. This signal asserts at least ARM_DELAY cycles after o_stimuli_valid to give the user design time to react to the stimuli.                   |

| ENABLE_EDGE_TRIGGERS | 1             | When set to 1, both edge-sensitive (rise/fall) and level-sensitive (1 /0) trigger conditions may be used during a Snapshot debug session. When set to 0, only level-sensitive trigger conditions may be used. Setting to 0 decreases the Achronix core logic resources needed for Snapshot. |

## Startup Trigger Parameters

Normally, trigger conditions are specified via the ACE Snapshot GUI prior to taking a capture. However, that makes it hard to observe conditions that occur right after startup. As alternative, an initial trigger condition can be specified using parameters. When INITIAL\_TRIGGER is set, Snapshot is armed immediately after startup and waits for the initial trigger condition. The ACE Snapshot GUI has a separate Startup Trigger button to collect the captured data.

Since initial triggers have virtually no circuit overhead, they are enabled by default with a don't-care trigger. With these defaults, the Startup Trigger button collects data from the start of user mode (or as close to the start as possible). Snapshot needs a few clock cycles to initialize before it can collect data or detect trigger conditions. For Speedcore instances, this delay is three cycles if MONITOR\_DEPTH ≤ 1024; otherwise it is six cycles. Signals will not be monitored during those few cycles unless INPUT\_PIPELINING is used. If INPUT\_PIPELINING is at least 3 (for small depth) or 6 (for larger depth), data is collected from the start of user mode.

**Table 6: Snapshot Startup Trigger Parameters**

| Parameter            | Default<br>Value | Defined Value                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INITIAL_TRIGGER      | 1                | Enables a startup trigger condition. Set the other INITIAL_* parameters to specify the trigger condition. When INITIAL_TRIGGER is 1, Snapshot automatically arms right after startup. If INITIAL_TRIGGER is 0, the INITIAL_* parameters are ignored, and Snapshot waits in the Idle state until the user arms Snapshot via the ACE GUI or TCL interface.                          |

| INITIAL_NUM_TRIGGERS | 1                | Number of sequential triggers to use for the startup trigger. Valid range is 1 to NUM_TRIGGERS.                                                                                                                                                                                                                                                                                   |

| INITIAL_TRIGGER1     | X's              | INITIAL_TRIGGER1 is specified as a sequence of characters "0" for level 0, "1" for level 1, "R" for rising edge, "F" for falling edge, "X" for don't care, with one character per trigger bit, similar to the binary value specified for a bus in the ACE GUI. For example, if TRIGGER_WIDTH is set to 5, INITIAL_TRIGGER1 could be set to "11XR0" to define the trigger pattern. |

| Parameter         | Default<br>Value | Defined Value                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INITIAL_TRIGGER2  | X's              | Specifies the second startup trigger using the same format as INITIAL_TRIGGER1. Snapshot waits for INITIAL_TRIGGER2 after INITIAL_TRIGGER1 has occurred. This parameter is ignored if INITIAL_NUM_TRIGGERS < 2.                                                                                                                                                                                                                                                       |

| INITIAL_TRIGGER3  | X's              | Specifies the third startup trigger using the same format as INITIAL_TRIGGER1. Snapshot waits for INITIAL_TRIGGER3 after INITIAL_TRIGGER2 has occurred. This parameter is ignored if INITIAL_NUM_TRIGGERS < 3.                                                                                                                                                                                                                                                        |

| INITIAL_USE_AND_1 | 1                | When set to 1, the INITIAL_TRIGGER1 pattern matches the input trigger data if <b>ALL</b> of the trigger bits match the trigger pattern (AND logic). When set to 0, the INITIAL_TRIGGER1 pattern matches the input trigger data if <b>ANY</b> of the trigger bits matches the trigger pattern (OR logic). In both cases, don't-care bits (marked "X") are ignored. However, if all INITIAL_TRIGGER1 bits are "X" (don't-care), this parameter <b>must</b> be set to 1. |

| INITIAL_USE_AND_2 | 1                | Similar to INITIAL_USE_AND_1, but for INITIAL_TRIGGER2.                                                                                                                                                                                                                                                                                                                                                                                                               |

| INITIAL_USE_AND_3 | 1                | Similar to INITIAL_USE_AND_1, but for INITIAL_TRIGGER3.                                                                                                                                                                                                                                                                                                                                                                                                               |

| INITIAL_PRE_STORE | 1                | Amount of pre-store data to cache and output prior to the trigger event. Valid values are 0 (no pre-store), 1 (25% pre-store), 2 (50% pre-store), and 3 (75% pre-store). If the startup trigger occurs before INITIAL_PRE_STORE clock cycles have occurred, by necessity less pre-store data is collected.                                                                                                                                                            |

# Parameter Impact on Core Logic Utilization

The following parameters impact the amount of core logic resources required for the Snapshot circuit:

- MONITOR\_WIDTH

- MONITOR DEPTH

- TRIGGER\_WIDTH

- NUM\_TRIGGERS

- ENABLE EDGE TRIGGERS

- STIMULI\_WIDTH

- INPUT\_PIPELINING

- OUTPUT\_PIPELINING

#### Note

The Snapshot resource utilization is really only important for designs that take up most of the FPGA, or in very small FPGA cores. If a design that includes Snapshot is pushing the limits of (or exceeding) core fabric resources, adjust the parameters above to reduce the size of the Snapshot logic.

Below is a rough estimate of the number of gates required based on these parameters:

- The number of BRAMs/BRAMFIFOs must be sufficient to store MONITOR\_WIDTH × MONITOR\_DEPTH bits

- Input pipelining consumes roughly (MONITOR\_WIDTH + TRIGGER\_WIDTH) × INPUT\_PIPELINING flip-flops.

- Output pipelining consumes roughly STIMULI WIDTH × OUTPUT PIPELINING flip-flops.

- The trigger circuit requires roughly NUM\_TRIGGERS × 5 × TRIGGER\_WIDTH flip-flops. The number of flip-flops can be reduced by setting NUM\_TRIGGERS to 1 or 2, by reducing the width, or by disabling edge triggers. Edge triggers account for roughly 40% of the trigger circuit.

#### Note

For high-speed circuits, input or output pipelining may be required to meet performance.

## Snapshot Verilog Interface

```

// - MONITOR_DEPTH will be rounded up to the next value supported by

this implementation.

// - If STANDARD_TRIGGERS is 1, the i_trigger input is ignored and instead

i_monitor[TRIGGER_WIDTH - 1 : 0] are used as trigger signals.

// - Stimuli are valid only when o_stimuli_valid is true; at other times

o stimuli are not stable.

// - o_arm indicates when Snapshot starts waiting for the trigger condition.

This happens at least ARM_DELAY cycles after o_stimuli_valid, to give

the user design time to react to the stimuli.

// - INPUT_PIPELINING is added to i_monitor and i_trigger, to make it easier

to collect high-frequency signals from various locations. Likewise,

//

OUTPUT_PIPELINING is added to o_stimuli, o_stimuli_valid, and o_arm.

Note that these parameters have *no impact* on the collected data

//

(the vcd file) or on the point where the trigger occurs.

//

// - To set a startup trigger condition, set INITIAL_TRIGGER to 1, then

set the INITIAL_ parameters to specify the trigger condition.

INITIAL_TRIGGER1 is a sequence of characters "0", "1", "R", "F", "X", one

//

//

character per bit, similar to the binary value specified for a bus

//

in the ACE GUI.

// - The o_trigger output is seldom used. It goes high INPUT_PIPELINING + 5

cycles after the trigger condition occurred. This signal is provided

//

as a trigger for external equipment such as a scope. No output

//

pipelining is added.

// - SNAPSHOT MODE is used for development.

`default_nettype none

`timescale 1 ps / 1 ps

module ACX_SNAPSHOT #(

localparam integer max_dut_name_chars = 128,

parameter [8*max_dut_name_chars-1 : 0] DUT_NAME = "none_specified",

parameter integer MONITOR_WIDTH = 40,

// >= 1

parameter integer MONITOR_DEPTH = 1024, // 1024 .. 16384

// 1..40

parameter integer TRIGGER_WIDTH = 40,

parameter integer NUM_TRIGGERS = 3,

// 1..3

parameter bit STANDARD_TRIGGERS = 1, // use i_monitor instead of i_trigger

```

```

parameter integer STIMULI_WIDTH = 20, // <= 512</pre>

parameter integer INPUT_PIPELINING = 3, // for i_monitor and i_trigger

parameter integer OUTPUT_PIPELINING = 0, // for o_stimuli(_valid) and o_arm

// between o_stimuli_valid and o_arm

parameter integer ARM_DELAY = 1,

parameter bit ENABLE_EDGE_TRIGGERS = 1,

parameter bit INITIAL_TRIGGER = 0, // set startup trigger condition

parameter [1:0] INITIAL NUM_TRIGGERS = 1, // 1..NUM_TRIGGERS

parameter [8*TRIGGER_WIDTH-1 : 0] INITIAL_TRIGGER1 = {TRIGGER_WIDTH{8'h58}},

parameter [8*TRIGGER_WIDTH-1 : 0] INITIAL_TRIGGER2 = {TRIGGER_WIDTH{8'h58}},

parameter [8*TRIGGER WIDTH-1 : 0] INITIAL TRIGGER3 = {TRIGGER WIDTH{8'h58}},

parameter bit INITIAL_USE_AND_1 = 1, // 1 = AND, 0 = OR

parameter bit INITIAL_USE_AND_2 = 1,

parameter bit INITIAL_USE_AND_3 = 1,

parameter [1:0] INITIAL_PRE_STORE = 1, // 0, 1, 2, 3 (= 0, 25%, 50% 75%)

parameter integer SNAPSHOT_MODE = 0

) (

// jtag connections, must be connected to top-level ports

input wire i_tck,

input wire i_trstn,

input wire i_tms,

input wire i_tdi,

output wire o_tdo,

// signals to/from user design

input wire

i_user_clk,

input wire [MONITOR_WIDTH-1 : 0]

i_monitor,

input wire [TRIGGER_WIDTH-1 : 0]

i_trigger, // if !STANDARD_TRIGGERS

output wire [STIMULI_WIDTH-1 : 0]

o_stimuli,

output wire

o_stimuli_valid,

output wire

o_arm,

output wire

o_trigger // for external devices

);

```

## Snapshot VHDL Interface

```

component ACX_SNAPSHOT is

generic (

: string := "none_specified";

DUT_NAME

MONITOR_WIDTH : natural := 40;

-- >= 1

MONITOR_DEPTH : natural := 1024;

-- 1024 ... 16384

TRIGGER_WIDTH : natural := 40;

-- 1 ... 40

NUM_TRIGGERS

: natural := 3;

-- 1, 2, 3

STANDARD_TRIGGERS: std_logic := '1';

-- use "i_monitor" instead of

"i_trigger"

STIMULI_WIDTH : natural := 20;

-- <= 512

INPUT_PIPELINING: natural := 3;

-- FOR i_monitor AND i_trigger

OUTPUT_PIPELINING: natural := 0;

-- FOR o_stimuli(_valid) AND

o_arm

```

```

ARM_DELAY

: natural := 1;

-- BETWEEN o_stimuli_valid AND

o_arm

ENABLE_EDGE_TRIGGERS : std_logic := '1';

INITIAL_TRIGGER

: std_logic := '0'; -- SET STARTUP TRIGGER

CONDITION

INITIAL_NUM_TRIGGERS : std_logic_vector (1 downto 0) := "01"; -- 1, 2,

INITIAL_TRIGGER1

: string :=

TRIGGER_WIDTH. VALID CHARACTERS ARE X, 0, 1, R, AND F.

INITIAL_TRIGGER2

: string :=

TRIGGER_WIDTH. VALID CHARACTERS ARE X, 0, 1, R, AND F.

INITIAL_TRIGGER3

: string :=

TRIGGER_WIDTH. VALID CHARACTERS ARE X, 0, 1, R, AND F.

INITIAL_USE_AND_1 : std_logic : = '1'; -- 1 = AND, 0 = OR

INITIAL_USE_AND_2 : std_logic : = '1'; -- 1 = AND, 0 = OR

INITIAL USE AND 3

INITIAL_PRE_STORE : std_logic_vector (1 downto 0) := "00"; -- 0, 1,

2, 3 (= 0, 25\%, 50\%, 75\%)

SNAPSHOT_MODE

: natural := 0 -- reserved

);

port ( --- JTAG connections, must be connected to TOP-LEVEL ports ---

i_tck

: in std_logic;

: in std_logic;

i_trstn

: in std_logic;

i_tms

i_tdi

: in std_logic;

o_tdo

: out std_logic;

--- SIGNALS to/from USER DESIGN ---

i_user_clk : in std_logic;

: in std_logic_vector (MONITOR_WIDTH-1 downto 0);

i_monitor

i_trigger

: in std_logic_vector (TRIGGER_WIDTH-1 downto 0);

: out std_logic_vector (STIMULI_WIDTH-1 downto 0);

o_stimuli

o_stimuli_valid : out std_logic;

: out std_logic;

o_arm

: out std_logic

o_trigger

);

end component;

```

# Chapter - 4: Snapshot Example

The following is a complete example of a simple user design with Snapshot. The user design consists of two counters and has the following features:

- counter\_a[7:0] counts from 0 to limit\_a repeatedly

- limit\_a[7:0] can be set dynamically with the Snapshot stimuli

- counter\_b[15:0] 16-bit counter (wraps around)

- External reset or reset via Snapshot stimuli

In order to use the Snapshot logic in a user design, the technology-specific Snapshot Verilog file from the Achronix libraries must be included:

```

`include "speedster<technology>/common/speedster<technology>_snapshot_v3.v"

```

Where <technology> is replaced with the target technology library name.

Two clocks are required by the Snapshot macro:

- i user c1k this clock is provided by the user design and is used to sample the user design signals.

- i\_tck the IEEE 1149.1 JTAG based TCK used to read the data out from the Snapshot macro through the JTAG TDO port.

Snapshot evaluates triggers and collects data at the rate of the user\_clk, whose frequency must be declared in the SDC file.

The design must meet timing with respect to user\_clk. Even if timing failures in the user design are deemed acceptable, their existence might hide timing failures in the Snapshot logic. Instead, "acceptable" timing failures must be made explicit with exceptions in the SDC file. If the Snapshot logic itself does not meet timing, consider increasing the INPUT\_PIPELINING and OUTPUT\_PIPELINING parameters.

The JTAG clock ( $i_tck$ ) for Snapshot must be declared as a 10 MHz clock (period 100 ns). It is recommended that this frequency is also specified during synthesis, because Synplify may over-optimize this slow logic.

The example below includes CLK\_IPIN and IPIN instances for a Speedcore device. For a standalone FPGA, use IPAD instances instead. Pad placement appropriate to the device and board must be specified. JTAG signals must not be connected to IPINs or IPADs.

The Snapshot macro should be instantiated in the user design, as shown below, and connected to the signals that may need to be observed. Next, the design is synthesized with Synplify and run through the ACE flow to generate a bitstream. Once the Achronix device has been programmed with the bitstream, the Snapshot debugger tool may be used from the ACE GUI or in batch mode via the ACE TCL interface.

#### Note

When the user design is run through the ACE place and route flow, a Snapshot configuration file will be generated in <code><ace\_project\_dir>/<active\_impl\_dir>/output/names.snapshot</code>. This file contains all the signal names connected to Snapshot (automatically extracted from the user design), along with monitor, trigger, and stimuli width settings based on the user RTL, clock frequency based on the user SDC constraints, etc. This file is automatically loaded in the Snapshot Debugger View in the ACE GUI to configure Snapshot whenever the active implementation in the ACE session changes.

# Clock Constraints (SDC File)

Both the JTAG TCK clock and the Snapshot user clock must be defined in the user SDC clock constraints:

```

# Snapshot JTAG clock: 10MHz

create_clock -period 100 [get_ports i_tck] -name tck

set_clock_groups -asynchronous -group {tck}

# User design clock; example: 100MHz

create_clock -period 10 [get_ports i_clk_100] -name i_clk_100

set_clock_groups -asynchronous -group {i_clk_100}

```

## Example Verilog RTL

```

// Copyright (c) 2017 Achronix Semiconductor Corp.

// All Rights Reserved.

`include "speedster16t/common/speedster16t_snapshot_v3.v"

`default_nettype none

`timescale 1ps/1ps

module snapshot_counter_v3_sc (

// jtap ports:

input wire i_tck,

input wire i_trstn,

input wire i_tms,

input wire i_tdi,

output wire o_tdo,

output wire o_tdo_oen,

// user design ports:

input wire i_clk_100,

input wire i_rst_n

);

wire clk;

CLK_IPIN ipin_i_clk_100(.din(i_clk_100), .dout(clk));

// Snapshot stimuli are only valid when stimuli_valid is high.

wire stimuli_valid;

reg [2:0] stimuli_valid_d; // for edge detection/stretching

always @(posedge clk)

begin

stimuli_valid_d <= (stimuli_valid_d << 1) | stimuli_valid;</pre>

```

```

wire rst_n;

IPIN #(

.mode(`DEF_IPIN_MODE_CLOCKED)

) ipin_i_reset_n (

.din(i_rst_n),

.clk(clk),

.ce(1'b1),

.rstn(1'b1),

.dout(rst_n)

);

reg [3:0] pipe_i_rst_n; // pipeline from i_rst_n pad, for timing

wire do_reset; // set via stimuli (active-high)

// At edge detection of stimuli_valid, do_reset is a reset input (active-high).

// While do_reset stays high, we de-assert reset after 3 cycles.

reg reset_n = 0;

always @(posedge clk)

begin

pipe_i_rst_n <= (pipe_i_rst_n << 1) | rst_n;</pre>

if (stimuli_valid && !stimuli_valid_d[2])

reset_n <= pipe_i_rst_n[3] && !do_reset;</pre>

else

reset_n <= pipe_i_rst_n[3];</pre>

end

// The main user design consists of two counters.

// counter_a : 8-bit counter with configurable period. The period is set

by setting limit_a via the Snapshot stimuli. Default

//

limit_a = 62 (hence counter_a has default period 63).

// counter_b : 16-bit counter

reg [7:0] limit_a = 62;

reg [7:0] counter_a = 0; // counts 0..limit_a

reg [15:0] counter_b = 0;

always @(posedge clk)

begin

if (!reset_n)

begin

counter_a <= 0;</pre>

counter_b <= 0;</pre>

end

else

begin

if (counter_a == limit_a)

counter_a <= 0;</pre>

```

```

else

counter_a <= counter_a + 1;</pre>

counter_b <= counter_b + 1;</pre>

end

end

wire [7:0] limit_a_in; // set via stimuli; if not 0, value for limit_a

always @(posedge clk)

begin

if (stimuli_valid && limit_a_in != 0)

limit_a <= limit_a_in;</pre>

end

localparam MONITOR_WIDTH = 38;

localparam TRIGGER_WIDTH = 38;

wire [MONITOR_WIDTH-1 : 0] monitor;

wire arm;

assign monitor = {

counter_b,

counter_a,

limit_a,

arm,

stimuli_valid,

reset_n

};

localparam STIMULI_WIDTH = 9;

wire [STIMULI_WIDTH-1 : 0] stimuli;

assign {

do_reset,

limit_a_in

} = stimuli;

ACX_SNAPSHOT #(

.DUT_NAME("counter_v3"),

.MONITOR_WIDTH(MONITOR_WIDTH),

.MONITOR_DEPTH(2000), // will be rounded up

.TRIGGER_WIDTH(TRIGGER_WIDTH),

.NUM_TRIGGERS(3),

.STANDARD_TRIGGERS(1), // use i_monitor as trigger input

.STIMULI_WIDTH(STIMULI_WIDTH),

.INPUT_PIPELINING(3),

.OUTPUT_PIPELINING(0),

.ARM_DELAY(2),

.ENABLE_EDGE_TRIGGERS(1)

) x_snapshot (

.i_tck(i_tck),

.i_trstn(i_trstn),

.i_tms(i_tms),

.i_tdi(i_tdi),

```

```

.o_tdo(o_tdo),

.o_tdo_oen(o_tdo_oen),

.i_user_clk(clk),

.i_monitor(monitor),

.i_trigger(), // not used if STANDARD_TRIGGERS = 1

.o_stimuli(stimuli),

.o_stimuli_valid(stimuli_valid),

.o_arm(arm),

.o_trigger()

);

endmodule

```

# Chapter - 5: Probing in a Hierarchical Design

## Overview

Snapshot provides the ability to probe signals deep within a hierarchical design without the need to modify every level of RTL, i.e., pulling the signals though the hierarchy up to the top level.

A special macro allows the user to define which signals are to be probed within the deeply embedded module. These probe points are then matched at the top-level module where Snapshot is instantiated. Synplify or ACE (depending on usage) aligns the deeply embedded and top-level signals, providing access to the embedded signals without having to explicitly bring them to the top level through multiple levels of RTL.

This method uses modules ACX\_PROBE\_CONNECT and ACX\_PROBE\_POINT. There are two options for using them:

- Use a user-defined tag to associate an ACX\_PROBE\_POINT with an ACX\_PROBE\_CONNECT

- Use a hierarchical pin name (with wildcards) to associate pins with an ACX PROBE CONNECT

Then monitor the ACX\_PROBE\_CONNECT output with Snapshot.

Generally, the method with tags is preferred, because it is often hard to determine the full hierarchical name of a pin. The method with a pin name is useful for tapping a signal from a macro that cannot be edited (for example, probing inside the library macros or third-party IP).

#### Note

The first method, with tags, uses Synplify syn\_hyper\_source and syn\_hyper\_connect instances; error messages may refer to those terms.

#### Module Declarations

```

module ACX_PROBE_POINT #(

parameter integer width = 1, // set to input width

parameter tag = "" // set to unique string

) (

input [width-1:0] din

);

endmodule

```

An ACX\_PROBE\_POINT takes as input one or more signals that need to be observed with Snapshot. It is instantiated in the hierarchy at the point where these signals are available.

```

module ACX_PROBE_CONNECT #(

parameter integer width = 1, // must match width of source

parameter tag = "", // must match tag of source

parameter pin = "", // "instance:pin" or "instance:bus", wildcards allowed

parameter must_connect = 1'b1 // whether missing source is error or warning

) (

output [width-1:0] dout

```

```

);

endmodule

```

The output of an ACX\_PROBE\_CONNECT instance are then monitored with Snapshot. This instance can be created in the same module as the ACX\_SNAPSHOT instance. The software uses the tag string to find a matching ACX\_PROBE\_POINT, then replaces both modules with a direct connection between the input of ACX\_PROBE\_POINT and the output of ACX\_PROBE\_CONNECT.

Alternatively, for cases where it is not possible to insert an ACX\_PROBE\_POINT, ACX\_PROBE\_CONNECT can be used with a hierarchical pin name instead of a tag. The ACE find command may be useful when trying to determine hierarchical names.

## Example

This code below is the same as the design shown in Snapshot Example (see page 20), but places the user design (the two counters) inside a separate module, counters. One can easily imagine that this module is designed to compute some function (all\_zero in this example) without necessarily exposing the counters themselves. But during debugging, counter values need to be observed to verify correctness. Rather than adding ports to expose the counters, maybe for many levels of hierarchy, probe points can be used instead.

As mentioned, using probe points with tags is preferred, but for the sake of the example. a probe point was only placed on counter a; counter b is identified by pin name.

```

Nested module with local counters

`default_nettype none

`timescale 1ps/1ps

module counters (

input clk,

input reset_n,

input [7:0] limit_a,

output all_zero

);

// The main user design consists of two counters.

// counter_a : 8-bit counter with configurable period.

// counter_b : 16-bit counter

reg [7:0] counter_a = 0; // counts 0..limit_a

reg [15:0] counter_b = 0;

always @(posedge clk)

begin

if (!reset_n)

begin

counter_a <= 0;

counter b <= 0;

end

else

if (counter_a == limit_a)

counter_a <= 0;</pre>

```

```

clse

counter_a <= counter_a + 1;

counter_b <= counter_b + 1;

end

end

assign all_zero = (counter_a == 0 && counter_b == 0);

/********* probe points for Snapshot ***********************

ACX_PROBE_POINT #(

.width(8),

.tag("counter_a")

) probe_counter_a (

.din(counter_a)

);

endmodule // counters

`default_nettype wire</pre>

```

Next, at the top level where Snapshot is instantiated, we create matching ACX\_PROBE\_CONNECT instances that use the same tags. For counter\_b the pin name method is used to create the connection. While counter\_a and counter\_b are seemingly driven by ACX\_PROBE\_CONNECT, behind the scenes they will be connected to the real counters.

```

Top-level module with Snapshot

`include "speedster16t/common/speedster16t_snapshot_v3.v"

`default_nettype none

`timescale 1ps/1ps

module snapshot_counter_v3_sc (

// jtap ports:

input wire i_tck,

input wire i_trstn,

input wire i_tms,

input wire i_tdi,

output wire o_tdo,

output wire o_tdo_oen,

// user design ports:

input wire i_clk_100,

input wire i_rst_n

wire clk;

CLK_IPIN ipin_i_clk_100(.din(i_clk_100), .dout(clk));

// Snapshot stimuli are only valid when stimuli_valid is high.

```

```

wire stimuli_valid;

reg [2:0] stimuli_valid_d; // for edge detection/stretching

always @(posedge clk)

begin

stimuli_valid_d <= (stimuli_valid_d << 1) | stimuli_valid;</pre>

end

wire rst_n;

IPIN #(

.mode(`DEF_IPIN_MODE_CLOCKED)

) ipin_i_reset_n (

.din(i_rst_n),

.clk(clk),

.ce(1'b1),

.rstn(1'b1),

.dout(rst_n)

);

reg [3:0] pipe_i_rst_n; // pipeline from i_rst_n pad, for timing

wire do_reset; // set via stimuli (active-high)

// At edge detection of stimuli_valid edge, do_reset is a reset input (active-high).

// While do_reset stays high, we de-assert reset after 3 cycles.

reg reset_n = 0;

always @(posedge clk)

begin

pipe_i_rst_n <= (pipe_i_rst_n << 1) | rst_n;</pre>

if (stimuli_valid && !stimuli_valid_d[2])

reset_n <= pipe_i_rst_n[3] && !do_reset;</pre>

else

reset_n <= pipe_i_rst_n[3];</pre>

end

reg [7:0] limit_a = 62;

wire [7:0] limit_a_in; // set via stimuli; if not 0, value for limit_a

always @(posedge clk)

begin

if (stimuli_valid && limit_a_in != 0)

limit_a <= limit_a_in;</pre>

wire all_zero;

```

```

counters x_counter (

.clk(clk),

.reset_n(reset_n),

.limit_a(limit_a),

.all_zero(all_zero)

);

localparam MONITOR_WIDTH = 38;

localparam TRIGGER_WIDTH = 38;

wire [MONITOR_WIDTH-1 : 0] monitor;

wire arm;

wire [7:0] counter_a;

ACX_PROBE_CONNECT #(

.width(8),

.tag("counter_a")

) probe_counter_a (

.dout(counter_a)

);

wire [15:0] counter_b;

ACX_PROBE_CONNECT #(

.width(16),

.pin("*.counter_b[*]:q")

) probe_counter_b (

.dout(counter_b)

);

assign monitor = {

counter_b,

counter_a,

limit_a,

all_zero,

arm,

stimuli_valid,

reset_n

};

localparam STIMULI_WIDTH = 9;

wire [STIMULI_WIDTH-1 : 0] stimuli;

assign {

do_reset,

limit_a_in

} = stimuli;

ACX_SNAPSHOT #(

.DUT_NAME("v3"),

.MONITOR_WIDTH(MONITOR_WIDTH),

.MONITOR_DEPTH(3000), // will be rounded up

.TRIGGER_WIDTH(TRIGGER_WIDTH),

.NUM_TRIGGERS(3),

```

```

.STANDARD_TRIGGERS(1), // use i_monitor as trigger input

.STIMULI_WIDTH(STIMULI_WIDTH),

.INPUT_PIPELINING(3),

.OUTPUT_PIPELINING(0),

.ARM_DELAY(2),

.ENABLE_EDGE_TRIGGERS(1)

) x_snapshot (

.i_tck(i_tck),

.i_trstn(i_trstn),

.i_tms(i_tms),

.i_tdi(i_tdi),

.o_tdo(o_tdo),

.o_tdo_oen(o_tdo_oen),

.i_user_clk(clk),

.i_monitor(monitor),

.i_trigger(), // not used if STANDARD_TRIGGERS = 1

.o_stimuli(stimuli),

.o_stimuli_valid(stimuli_valid),

.o_arm(arm),

.o_trigger()

);

endmodule // snapshot_counter_v3_sc

`default_nettype wire

```

## Chapter - 6: Running the Snapshot User Interface

#### The JTAG connection must be configured before using the Snapshot Debugger!

ACE interacts with the FPGA using the JTAG interface through a Bitporter pod or FTDI FT2232H device. This JTAG interface must be properly configured in ACE before using the Snapshot Debugger view. The configuration is managed using the Configure JTAG Connection Preference Page, which is easily accessible by pressing the **Configure JTAG Interface** ( ) button in the Snapshot Debugger view. See Configuring the JTAG Connection for more details.

Snapshot is the real-time design debugging tool for Achronix FPGAs. Snapshot, which is embedded in the ACE Software, delivers a practical platform to evaluate the signals of a user's design in real-time, and optionally send stimuli to the user's design.

To utilize the Snapshot debugger tool, the Snapshot macro must be instantiated inside the RTL for the Design-Under-Test (DUT). After instantiating the macro and programming the device, the user will be able to debug the design in the ACE GUI using the Snapshot Debugger view and the VCD Waveform Editor, found within the Bitporter perspective.

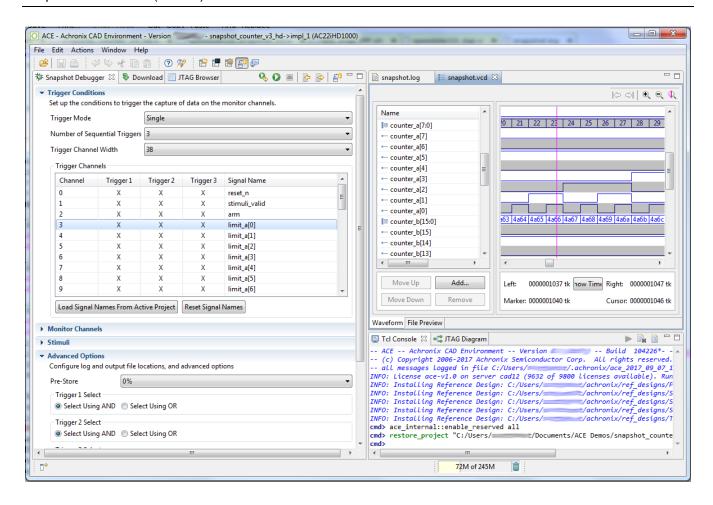

Figure 5: Snapshot Communication with the Snapshot Debugger View within ACE (Running on the Host PC)

When instantiated in a design, the Snapshot macro can be used to interface with any logic mapped to the Achronix FPGA core. The Snapshot macro provides a JTAG / JTAP interface to control/observe debug logic mapped to the core. This allows the ACE Snapshot Debugger view, which drives the JTAG interface, to control / observe the signals associated with the debug logic.

Within the ACE GUI, the Snapshot Debugger view allows a designer to configure an embedded Snapshot Debugger core, interactively arm the core, and generate a VCD waveform output of the collected samples. By default, the generated VCD waveform output will be displayed in the ACE Editor Area using the VCD Waveform Editor. The VCD output can also be read into a third-party waveform viewer.

At a high level, to utilize Snapshot the user must first:

- 1. instantiate the Snapshot macro ACX\_SNAPSHOT in the user's design

- 2. synthesize the design

- 3. place and route the design in ACE

- 4. generate the Bitstream for the design in ACE

- 5. configure ACE's JTAG connection to the FPGA (see Configuring the JTAG Connection)

- 6. program the Achronix device with the Bitstream

- use of the ACE GUI's Download View is documented in the section Playing a STAPL File (Programming a Device)

- use of the acx\_stapl\_player executable on the command-line is documented in the *Bitstream Programming and Debug Interface User Guide* (UG004)

Once those prerequisite steps are complete, the ACE GUI's Snapshot Debugger View allows the user to evaluate /interact with the running design in real-time

The following sections will further explain Snapshot and guide the user through the process.

# Accessing the Snapshot Debugger

## Open the ACE GUI and Select Your Project

Open the ACE GUI tool, and load or activate your project in the Projects View as shown below. See the Loading Projects, Setting the Active Implementation, and Working with Projects and Implementations sections for details.

Figure 6: ACE Tool

## Open the Snapshot Debugger

Click the toolbar button to change to the Programming and Debug Perspective ( = ) as described in the Working with Perspectives section. The Snapshot Debugger View should be visible by default, as shown below. If not, you can click **Window**—**Show View**—**Snapshot Debugger** from the main menu bar.

The Snapshot Debugger View should have automatically loaded the default Snapshot configuration file for your project that was generated when you ran your design through place and route, located in <code><ace\_project\_dir>/<active\_impl\_dir>/output/names.snapshot</code>. If it loaded, you will see the correct signal names from your user design in the Trigger Channels, Monitor Channels, and Stimuli tables. If it did not automatically load, you can click the <code>Load Snapshot Configuration</code> ( ) toolbar button in the Snapshot Debugger View to browse to the location of you preferred <code>\*.snapshot configuration</code> file, or manually enter the signal names, channel widths, etc to match your design.

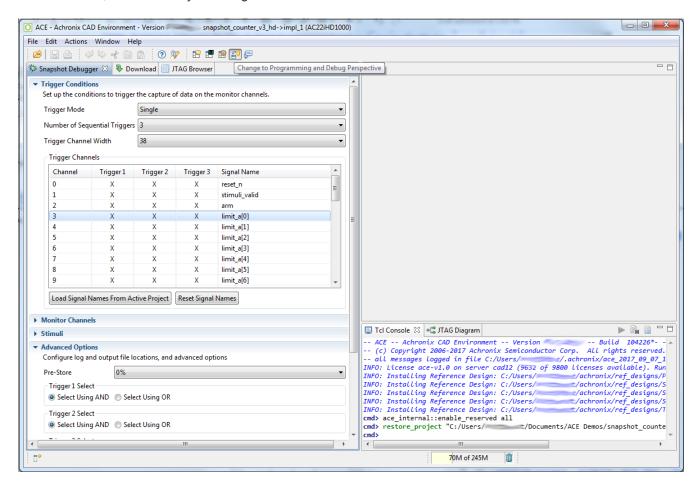

Figure 7: Snapshot Debugger View

## Configuring the Trigger Pattern

1

The Trigger Channel signal names are automatically configured to the correct values when the names snapshot file is loaded. The names snapshot file is generated during design preparation (the **Run Prepare** Flow Step), which contains the user design signal names connected to Snapshot, along with the trigger width and the maximum number of sequential triggers.

## Configuring the Trigger Mode

The **Trigger Mode** option allows the user to select the trigger mode to use when the Arm action is run.

#### **Single**

The default trigger mode is **Single**, which means the trigger conditions are programmed in to the ACX\_SNAPSHOT macro and then the GUI waits for a single trigger event to occur which matches those trigger conditions, and then a single VCD file is recorded. This option arms Snapshot and captures data only once.

#### **Immediate**

If **Immediate** trigger mode is selected, pressing the Arm button results in the same behavior as **Single** trigger mode, except that all 3 trigger patterns are treated as "Don't Care" (X's) so that the trigger event will occur as soon as the Arm button is pressed. This mode is useful to quickly capture the state of the running design without waiting for any trigger pattern to be met.

#### Repetitive

If **Repetitive** trigger mode is selected, the trigger conditions are programmed in to the ACX\_SNAPSHOT macro and samples are captured repetitively until the upper limit of trigger event records is reached. When **Repetitive** trigger mode is selected, an additional set of repetitive trigger mode options will appear to allow the user to configure the number of sequential times Snapshot should be armed repetitively using the configured trigger conditions, and the way in which the output VCD files are managed. This mode is useful when the trigger conditions do not narrow in on the exact data pattern and the pattern you intend to observe occurs sporadically at the trigger conditions. You can let the repetitive trigger mode run for a long period of time, taking several capture records at the trigger conditions, to help find the pattern you are interested in. The user can optionally cancel the remaining Snapshot session once the desired data is captured.

The repetitive trigger Record Limit setting determines how many times (number of records) the GUI will repeatedly Arm the Snapshot debugger and capture samples. The user may set this to automatically run Snapshot up to 128 times.

The repetitive trigger VCD Record Limit setting determines how many Snapshot records to capture in a single VCD file. This essentially concatenates the VCD files from consecutive runs of Snapshot (records) into a single VCD file. The VCD file waveform contains a set of virtual signals to indicate the system timestamp at which each Snapshot record was captured. The user may concatenate up to 10 Snapshot records in a single VCD file.

If the Overwrite VCD File option is selected, the VCD Waveform File name specified in the Advanced Options section will be used to store the output VCD file. The file will be overwritten with the new VCD file each time the VCD record limit is reach. If the Overwrite VCD File option is not selected, then multiple VCD files will be written out and a unique VCD record number will be added to the VCD Waveform File name specified in the Advanced Options section for each VCD. For example, if you set the Record Limit to 8 and set the VCD Record Limit to 2, and set the VCD Waveform file path the "./snapshot.vcd", then Snapshot would output 4 VCD files to "./snapshot1.vcd", "./snapshot2.vcd", "./snapshot4.vcd", each containing 2 Snapshot capture records.

## Configuring Trigger Patterns

The Snapshot Debugger can be configured to use a **Trigger Channel Width** of 1 to 40 bits. The value entered in the Snapshot Debugger View must match the value of the *TRIGGER\_WIDTH* parameter set on the ACX\_SNAPSHOT module in the user design RTL. (This will be the width of the *i\_trigger* bus.)

The SnapShot Debugger is capable of handling one to three sequential trigger patterns. The post-trigger data is sampled once the last trigger pattern in the sequence is matched.

The user may specify the number of desired sequential trigger patterns using the **Number of Sequential Triggers** option in the Snapshot Debugger View. If **1** is selected, Trigger 2 and Trigger 3 are ignored. If **2** is selected, Trigger 3 is ignored and Snapshot will trigger when Trigger 1 is matched, followed (on any subsequent clock) by a match on Trigger 2. If **3** is selected, then Snapshot will trigger after a match on Trigger 1, followed (on any subsequent clock) by a match on Trigger 2.

Each sequential trigger is hooked up to the trigger channels on the Snapshot Debugger core. The LSb of the trigger pattern is hooked to trigger channel 0, and the MSb is hooked to upper most trigger channel bit (TRIGGER\_WIDTH - 1).

Each sequential trigger is made up of three parts: the pattern mask, the edge mask, and the don't care mask. In the Snapshot Debugger View, these 3 masks are combined for ease of use into a single trigger pattern value, which allows each bit to be specified as **X** (don't care), **R** (rising edge), **F** (falling edge), **0** (level 0), or **1** (level 1). The trigger pattern defines the trigger channel signal conditions that are required to detect a match. If a given trigger channel value is set to X (don't care), then this trigger channel is ignored when computing a match. If a given trigger channel value is set to R (rising edge), then this trigger channel is is evaluated as a match when a rising edge of this signal is seen by Snapshot. If a given trigger channel value is set to F (falling edge), then this trigger channel value is set to 1 (level 1), then this trigger channel is is evaluated as a match as long as this signal's level is seen as a 1 by Snapshot (it is not edge sensitive). If a given trigger channel value is set to 0 (level 0), then this trigger channel is is evaluated as a match as long as this signal's level is seen as a 0 by Snapshot (it is not edge sensitive).

If any active Trigger is configured with as all X's (don't care), the trigger pattern will be a match on the first clock cycle that trigger is evaluated.

The values within a trigger pattern may cause a trigger match event either by AND'ing or OR'ing. If AND'ing, then all signal values not masked (set to X) must match their pattern for the trigger match event to occur. If OR'ing, then the trigger match event will occur if any of the non-masked (not set to X) signal values match the specified pattern. The AND/OR configuration is set per sequential trigger using the **Select using AND** or **Select using OR** radio buttons. This selection can be different for each sequential trigger.

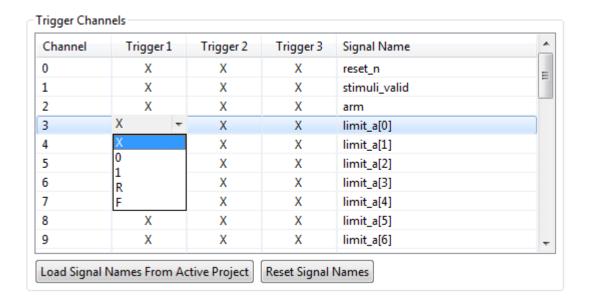

In the "Trigger Channels" table of the Snapshot Debugger View, the trigger patterns can be viewed and edited.

#### **Setting Pattern Values Using the Table**

For each channel, a value of  $\mathbf{X}$  (don't care),  $\mathbf{R}$  (rising edge),  $\mathbf{F}$  (falling edge),  $\mathbf{0}$  (level 0), or  $\mathbf{1}$  (level 1) can be specified via a pull-down menu under each "Trigger" column as shown below.

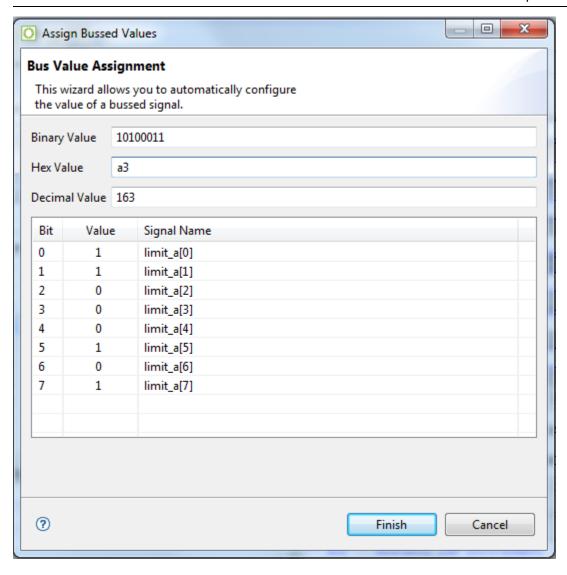

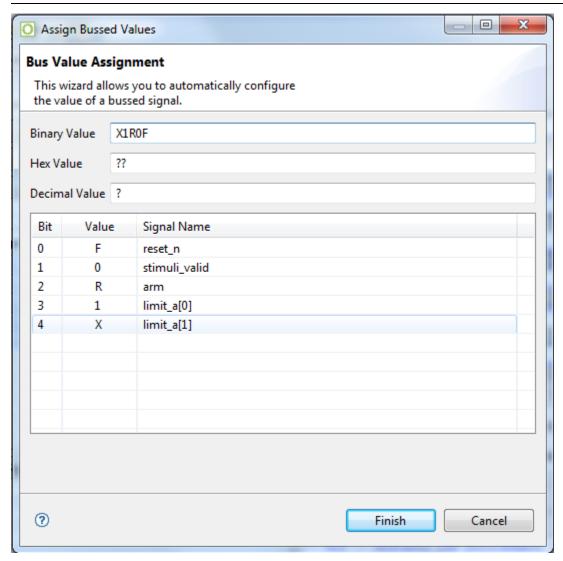

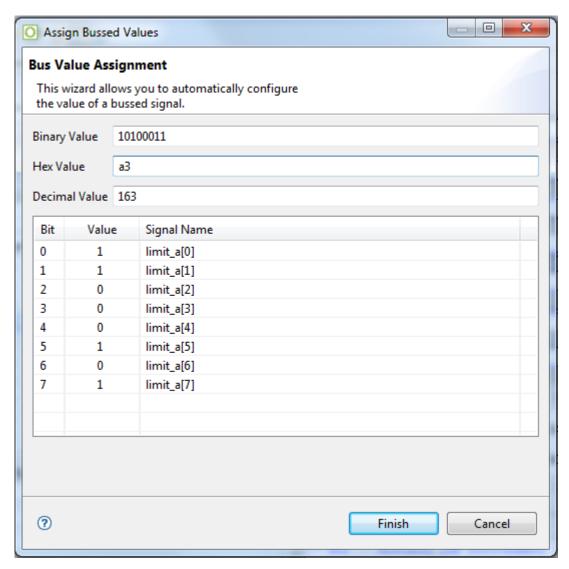

#### **Setting Multiple Pattern Values as a Bus**

The Assign Bussed Values Dialog wizard allows the user to assign a value to multiple signals from the SnapShot Debugger view's "Trigger Channels" or "Stimuli Channels" tables as a bus. After configuring the bus in the dialog, the values of each signal are propagated to all the selected signals in the SnapShot Debugger View. There are 2 ways to launch this dialog to allow bus assignment of values:

- 1. With your mouse, left click to select a single row in the SnapShot Debugger View table which has a bussed signal name (i.e. din[2]). Then right mouse click to edit the **Value by Bus**. This method will automatically find all the other bits in the bus with the same signal name (i.e. din[0], din[1], din[2], etc.) and open the dialog to allow editing of the entire bus of signals.

- 2. With your mouse, hold CTRL or SHIFT and left click to select multiple rows in the SnapShot Debugger View table. Then right mouse click to edit the **Value by Selection**. This method will open the dialog to allow editing of all selected signals as a bussed value.

See Assign Bussed Values Dialog for more information on this dialog.

# Configuring the Monitor Signals

The Monitor Signals are automatically configured to the correct values when the names.snapshot file is loaded. The names.snapshot file is generated during design preparation (the **Run Prepare** Flow Step ), which contains the user design signal names connected to Snapshot, along with the monitor width and number of samples.

The value of **Monitor Channel Width** in the SnapShot Debugger view must be configured to match the value of the *MONITOR\_WIDTH* parameter of the ACX\_SNAPSHOT instance inside the RTL of the design being debugged. (This will be the width of the *i monitor* bus.)

The value of **Number of Samples** in the SnapShot Debugger view should be configured to match the value of the *MONITOR\_DEPTH* parameter of the ACX\_SNAPSHOT instance inside the RTL of the design being debugged. If the value in the GUI does not match the value in the RTL, the value from the RTL will be used and a warning will be printed in the Snapshot log file.

#### Naming captured signal data

Custom signal names for each channel can be entered under the "Signal Name" heading within the "Monitor Channels" table. The signal/bus names in the "Monitor Channels" table are then used as labels on the captured signal data in the VCD waveform output, and will be visible in the VCD Waveform Editor.

Multiple signals can be combined into a bus by selecting multiple rows in the "Monitor Channels" table, right-clicking on a selected signal row to bring up a popup context menu, and selecting **Assign Bus Name** ( ) from the context menu to bring up the Assign Bussed Signal Names Dialog. After configuring the bus in the Assign Bussed Signal Names Dialog, the bus name and indices are propagated to all the previously-selected signals. To select a contiguous range of rows, select the first signal, hold the Shift key, and select the last signal. To select a non-contiguous set of rows, select the first signal, then while holding down the Ctrl key on the keyboard, select the other signals.

Signal names may be returned to their defaults by selecting the **Reset Signal Names** button under the "Monitor Channels" table. Note that this resets all signal names in the table at once, not just the currently selected rows /signals.

The Load Signal Names From Active Project button loads the names.snapshot file generated during design preparation (the Run Prepare Flow Step), which renames all signals with their project-specific names, and also loads the project-specific default settings for monitor width, user clock frequency, default log and vcd file path, etc.

# Configuring the Test Stimuli

The stimuli channel signal names are automatically configured to the correct values when the names. snapshot file is loaded. The names. snapshot file is generated during design preparation (the **Run Prepare** Flow Step), which contains the user design signal names connected to Snapshot, along with the stimuli width.

Snapshot has the capability to send 0 to 512 bits of test stimuli (the ACX\_SNAPSHOT macro output signal o\_stimuli) to the Design Under Test (DUT). This data is sent once per arming session, is only valid while the o stimuli\_valid signal is high.

This o\_stimuli output is optional, and need not be connected to the DUT - it may safely be left floating when the user wants to use Snapshot to only read signals.

The value of **Stimuli Channel Width** in the SnapShot Debugger view must be configured to match the value of the *STIMULI\_WIDTH* parameter of the ACX\_SNAPSHOT instance inside the RTL of the design being debugged. (This will be the width of the *o stimuli* bus.)

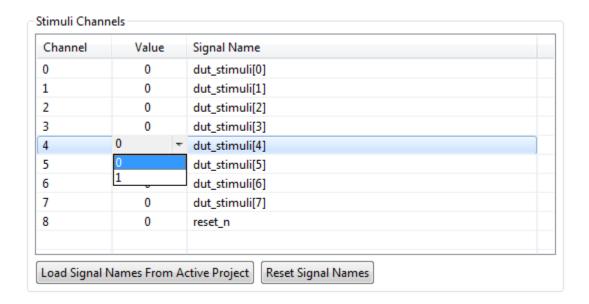

In the "Stimuli Channels" table of the Snapshot Debugger View, the stimuli values can be viewed and edited.

#### Setting Stimuli Values Using the Table

For each channel, an output value of **0** (level 0), or **1** (level 1) can be specified via a pull-down menu under the "Value" column as shown below.

#### Setting Multiple Stimuli Values as a Bus

The Assign Bussed Values Dialog wizard allows the user to assign a value to multiple signals from the SnapShot Debugger view's "Stimuli Channels" table as a bus. After configuring the bus in the dialog, the values of each signal are propagated to all the selected signals in the SnapShot Debugger View. There are 2 ways to launch this dialog to allow bus assignment of values:

- 1. With your mouse, left click to select a single row in the SnapShot Debugger View table which has a bussed signal name (i.e. din[2]). Then right mouse click to edit the **Value by Bus**. This method will automatically find all the other bits in the bus with the same signal name (i.e. din[0], din[1], din[2], etc.) and open the dialog to allow editing of the entire bus of signals.

- 2. With your mouse, hold CTRL or SHIFT and left click to select multiple rows in the SnapShot Debugger View table. Then right mouse click to edit the **Value by Selection**. This method will open the dialog to allow editing of all selected signals as a bussed value.

See Assign Bussed Values Dialog for more information on this dialog.

# Configuring Advanced Options

#### Pre-Store

In the Snapshot Debugger View, the **Pre-Store** setting configures the portion of samples that are collected before the trigger, and (indirectly) how many are collected after the trigger.

For example, assume the user has configured Snapshot to use a monitor depth of 1024 samples. See the table below:

Table 7: Effect of "Pre-store" on samples collected before and after the trigger event

| "Pre-Store" value | Samples collected before trigger | Samples collected after trigger |

|-------------------|----------------------------------|---------------------------------|

| 0%                | 0                                | 1024                            |

| "Pre-Store" value | Samples collected before trigger | Samples collected after trigger |

|-------------------|----------------------------------|---------------------------------|

| 25%               | 256                              | 768                             |

| 50%               | 512                              | 512                             |

| 75%               | 768                              | 256                             |

When a **Pre-Store** value other than **0%** is selected, the .vcd file will contain a signal *snapshot\_pre\_store* that transitions (goes low) at the point where the (last sequential) trigger event occurred. Thus, users may easily find the trigger event without needing to actually count the samples.