# Simulation User Guide (UG072)

All Achronix Devices

UG072

# Copyrights, Trademarks and Disclaimers

Copyright © 2024 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedcore, Speedster, and ACE are trademarks of Achronix Semiconductor Corporation in the U.S. and/or other countries All other trademarks are the property of their respective owners. All specifications subject to change without notice.

## Notice of Disclaimer

The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

# Achronix Semiconductor Corporation

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail: info@achronix.com

# Table of Contents

| Chapter 1: Overview                         | 1  |

|---------------------------------------------|----|

| Simulation Software Tool Flow               | 1  |

| Simulation Libraries                        | 2  |

| Including Memory Initialization Files       | 2  |

| Chapter 2 : Simulation from within ACE      | 4  |

| Example Design                              | 4  |

| Configuring the Simulation Tool Environment | 4  |

| Configuring the Project Source Files        | 5  |

| Configuring the Simulation Options          | 6  |

| Configuring Simulation                      | 9  |

| Default Simulation Flow                     | 9  |

| Custom Simulation Flow                      | 12 |

| Configuring the Simulation Waveform         | 13 |

| Running the Simulation Flow Steps           | 15 |

| Viewing the Simulation Outputs              | 18 |

| Chapter 3 : Simulation Outside of ACE       | 22 |

| General Project Setup                       | 22 |

| General RTL Simulation Flow                 | 23 |

| General Gate-Level Simulation Flow     | 3 |

|----------------------------------------|---|

| General Post-Route Simulation Flow     | 4 |

| Example Design Description             | 5 |

| Aldec Riviera Simulator Example        | 6 |

| RTL Simulation in Riviera20            | 6 |

| Step 1 – Create Simulation Directory20 | 6 |

| Step 2 - Create a .do File20           | 6 |

| Step 3 - Run the Simulation2           | 7 |

| Step 4 – View the Waveform28           | 8 |

| Step 5 – Open the Workspace28          | 8 |

| Step 6 – Initialize the Simulation29   | 9 |

| Step 7 - Add Signals to the Waveform29 | 9 |

| Step 8 – View the Waveform30           | 0 |

| Gate-Level Simulation in Riviera3      | 1 |

| Step 1 – Create the Synthesis Project  | 1 |

| Step 2 – Synthesize the Design         | 1 |

| Step 3 - Create a Workspace            | 1 |

| Step 4 - Run the Simulation            | 2 |

| Step 5 – View the Results              | 2 |

| Post-Route Simulation in Riviera       | 2 |

| Step 1 – Create the ACE Project3       | 3 |

| Step 2 - Run Place and Route3          | 3 |

| Step 3 - Create the Workspace3         | 3 |

| Step 4 - Run the Simulation34          | 4 |

| Step 5 – View the Results34            | 4 |

| Cadence Xcelium Simulator Example34    | 4 |

| RTL Simulation in Xcelium             | 34 |

|---------------------------------------|----|

| Step 1 – Invoke the Xcelium Tool      | 34 |

| Step 2 - Add Signals to the Waveform  | 36 |

| Step 3 - Run the Simulation           | 38 |

| Step 4 – View the Waveform            | 39 |

| Step 5 - View Console Messages        | 39 |

| Gate-Level Simulation in Xcelium      | 40 |

| Step 1 - Create the Synthesis Project | 41 |

| Step 2 - Synthesize the Design        | 41 |

| Step 3 - Run Simulation               | 41 |

| Step 4 – View Simulation Results      | 41 |

| Post-Route Simulation in Xcelium      | 42 |

| Step 1 – Create the ACE Project       | 42 |

| Step 2 - Run Place and Route          | 42 |

| Step 3 - Run Simulation               | 43 |

| Step 4 – View Simulation Results      | 43 |

| Siemens QuestaSim Simulator Example   | 44 |

| RTL Simulation in QuestaSim           | 44 |

| Step 1 - Create the Project           | 44 |

| Step 2 - Initialize the Work Library  | 44 |

| Step 3 - Create the File List         | 44 |

| Step 4 - Compile the Design           | 45 |

| Step 5 - Prepare the Simulation Run   | 45 |

| Step 6 - Set up the Waveform          | 46 |

| Step 7 – Run the Simulation           | 48 |

| Step 8 - View the Waveform            | 49 |

| Gate-Level Simulation in QuestaSim    | 49 |

|        | Step 1 – Create the Synthesis Project  | 49 |

|--------|----------------------------------------|----|

|        | Step 2 - Synthesize the Design         | 49 |

|        | Step 3 – Set up the Simulation Project | 49 |

|        | Step 4 – Initialize the Work Library   | 50 |

|        | Step 5 - Create the File List          | 50 |

|        | Step 6 – Compile the Design            | 50 |

|        | Step 7 - Prepare the Simulation Run    | 50 |

| Pos    | st-Route Simulation in QuestaSim       | 50 |

|        | Step 1 – Create the ACE Project        | 51 |

|        | Step 2 - Run Place and Route           | 51 |

|        | Step 3 - Set up the Simulation Project | 51 |

|        | Step 4 – Initialize the Work Library   | 51 |

|        | Step 5 - Create the File List          | 51 |

|        | Step 6 - Compile the Design            | 51 |

|        | Step 7 - Prepare the Simulation Run    | 52 |

| Synops | sys VCS Simulator Example              | 52 |

| RTI    | L Simulation in VCS                    | 52 |

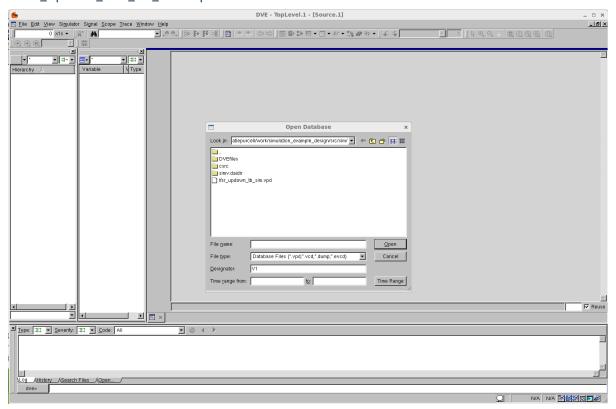

|        | Step 1 – Run the VCS Simulator         | 52 |

|        | Step 2 - Start the Simulation GUI      | 53 |

|        | Step 3 - Open the Simulation Database  | 54 |

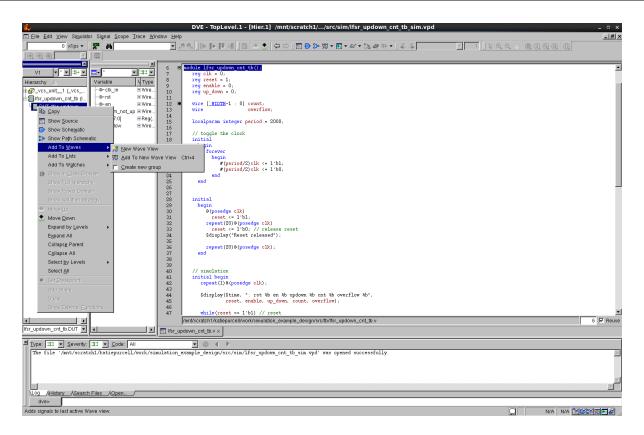

|        | Step 4 - Add Signals to the Waveform   | 54 |

|        | Step 5 - View the Simulation Results   | 55 |

| Gat    | te-Level Simulation in VCS             | 56 |

|        | Step 1 – Create the Synthesis Project  | 56 |

|        | Step 2 - Synthesize the Design         | 56 |

|        | Step 3 - Run the VCS Simulator         | 56 |

| Pos    | st-Route Simulation in VCS             | 56 |

|         | Step 1 – Create the ACE Project         | 56 |

|---------|-----------------------------------------|----|

|         | Step 2 - Run Place and Route            | 56 |

|         | Step 3 - Run the VCS Simulator          | 57 |

| Chapter | 4 : DSM Simulation Package              | 58 |

|         | Device Simulation Model                 | 58 |

|         | Description                             | 58 |

|         | Selecting the Required DSM              | 58 |

|         | DSM Utility Package                     | 58 |

|         | Device-Specific Simulation Files        | 59 |

|         | Instantiate DSM Utility Package         | 59 |

|         | Version Control                         | 60 |

|         | require_version() Task                  | 60 |

|         | Example Design                          | 61 |

|         | set_verbosity() Task                    | 63 |

|         | Chip Status Output                      | 63 |

|         | Bind Macros                             | 64 |

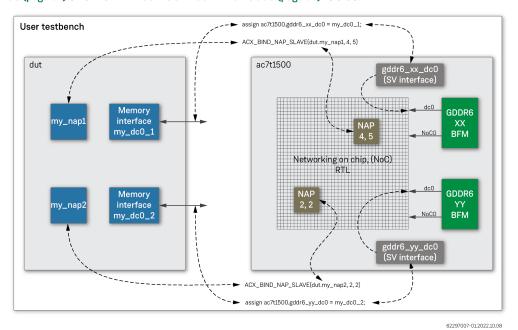

|         | Direct-Connect Interfaces               | 64 |

|         | Suggested Flows                         | 65 |

|         | DSM DC Interfaces                       | 65 |

|         | Direct Connect to DSM Interfaces        |    |

|         | Port Binding File to DSM Interfaces     | 67 |

|         | Dual-Mode Connections to DSM Interfaces | 68 |

|         | Clock Frequencies                       | 69 |

|         | Configuration                           | 71 |

|         | Startup Sequence                        | 72 |

|         | fcu configure() Task                    | 72 |

| Chapter 5 : Simulation User Guide Revision History |    |

|----------------------------------------------------|----|

| ACX_DEVICE_INSTALL_DIR                             | 76 |

| ACE_INSTALL_DIR                                    | 76 |

| Environment Variables                              | 76 |

| SystemVerilog Interfaces                           | 74 |

| Parallel Configuration                             | 74 |

| Address Width                                      | 74 |

| Configuration File Format                          | 73 |

# Chapter 1: Overview

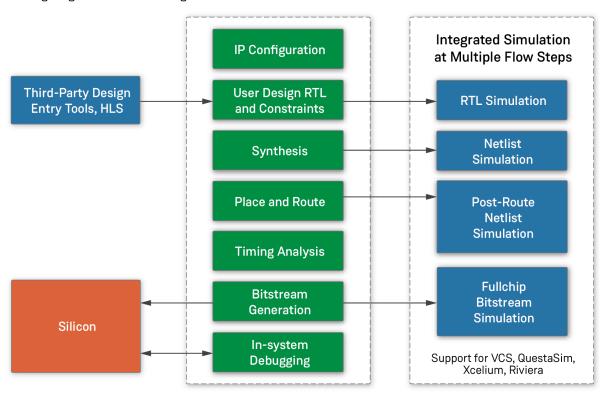

## Simulation Software Tool Flow

The Achronix tool suite includes synthesis and place-and-route software that maps RTL designs (VHDL or Verilog) into Achronix devices. In addition to synthesis and place-and-route functions, the Achronix software tools flow also supports simulation at several flow steps (RTL, synthesized netlist, and post place-and-route netlist), as shown in the figure below.

Functional simulation can be done at the following stages:

- Functional RTL level (referred to as RTL simulation)

- · Gate-level, post-synthesis netlist (referred to as gate-level simulation)

- · Gate-level, post-place-and-route netlist (referred to as post-route simulation)

- · Full-chip bitstream simulation with gate-level netlist

The following diagram shows the stages of simulation in the context of the Achronix software tool flow.

70541507-01.2024.11.21

Figure 1 · Stages of Simulation Flow

## Simulation Libraries

This guide covers simulation for all Achronix devices. The text in this user guide contains references to <DEVICE>. The user should replace this with the target device name for your project, for example AC7t1500. The base ACE install package does not contain any simulation libraries by default. The simulation libraries are device-specific and are installed from within the device overlay installation packages.

Table 1 · Achronix Simulation Libraries

| Directory                           |            | ory            | Description                                                                                                                                                       |

|-------------------------------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ace_install_dir></ace_install_dir> |            |                | Directory path to where ACE is installed.                                                                                                                         |

|                                     | /libraries |                | Root directory for simulation and other libraries provided by Achronix. This is the top-level library include directory (+incdir+) for Achronix device libraries. |

|                                     |            | /device_models | Contains the technology-specific top-level<br>Achronix device library include files for simulation<br>and synthesis.                                              |

The top-level device-specific library include file required for simulation is <ace\_install\_dir>/libraries/device\_models/<DEVICE>\_simmodels.sv. This top-level include file includes all of the library files for the given target device.

# Including Memory Initialization Files

If a design uses memories and includes memory initialization files, the designer needs to consider carefully where to place the files when running simulation or synthesis. Achronix recommends using relative paths when referencing memory initialization files. Relative paths allows for changes in the location of the project without having to change the memory file reference in the RTL design files. However, when using relative paths, the designer must ensure that the path to a memory initialization file is relative to:

- · The simulation directory when simulating.

- The ACE directory when generating a bitstream.

If these two relative paths are different, for example at different levels in the project hierarchy, the designer can use compiler directives to choose the correct path for the particular situation. An example is shown below.

##

The above use of the SIMULATION compiler directive can also be a good way to design in special debug features that are only for simulation and not intended to be synthesized. Compiler directives can also be a good way to speed up certain sections of logic for simulation if desired.

`endif

# Chapter 2: Simulation from within ACE

As of ACE 10.0, Achronix provides built-in support for configuring the simulation environment via ACE project options and for running simulations via ACE flow steps. Using the built-in ACE simulation flow gives the end user a streamlined user experience, and a way to manage all aspects of the project (IP configuration, synthesis, simulation, place and route) from a single ACE project file.

# Example Design

Although it is a simple example the quickstart tutorial design can be used to quickly demonstrate the ACE simulation flow. See ACE Quickstart Tutorial in the *ACE Users Guide* (UG070)<sup>1</sup> for details. The ACE simulation flow is capable of supporting nearly any simulation setup for a wide variety of designs and testbench structures across the supported list of simulator tools.

# Configuring the Simulation Tool Environment

ACE simulation flow steps currently support installations of Siemens QuestaSim, Aldec Riviera, Cadence Xcelium, or Synopsys VCS to run the simulations. Therefore, the simulator tool must be installed in a directory accessible from the host on which ACE is running. Each simulator requires an environment variable to be set appropriately, as shown in the following table.

Table 2 • Environment Variables Needed for Simulation

| Simulation<br>Tool | Environment<br>Variable     | Linux Path                                                                                                                                                                                | Windows Path                                                                                                           |

|--------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Siemens QuestaSim  | ACX_QUESTASIM_TOOL_PAT<br>H | Set to the Linux executable QuestaSim launcher script path. A default launcher script example can be found in <ace_install>/examples/simulation_scripts/questasim_launcher.</ace_install> | Set to the directory path containing the vlog.exe, vcom.exe, and vsim.exe files (i.e., D:\questa_base64_2023.3\win64). |

<sup>1</sup> https://www.achronix.com/documentation/ace-user-guide-ug070

| Simulation<br>Tool | Environment<br>Variable | Linux Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Windows Path                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Aldec Riviera      | ACX_RIVIERA_TOOL_PATH   | Set to the Linux executable Riviera launcher script path. A default launcher script example can be found in <ace_install>/examples/simulation_scripts/riviera_launcher.  Optionally, for viewing waveforms, either:  • add the path to /bin sub-directory for Riviera installation directory to PATH variable and ALDEC_LICENSE_FILE in the shell environment (and not the launcher script), or;  • In local launcher script, use <riviera_install_path>/bin/vsiminstead of <riviera_install_path>/runvsimsa.</riviera_install_path></riviera_install_path></ace_install> | Set to the file path of the Riviera runvsimsa.bat file (i.e., D:\Aldec\Riviera-PRO-2020.10-x64\runvsimsa.bat. Optionally, for viewing waveforms, either:  • Add the path to /bin subdirectory for Riviera installation directory to PATH variable in the local environment, or;  • Set to the file path of the <riviera_install_path>/bin/vsiminstead of <riviera_install_path>/runvsimsa.bat.</riviera_install_path></riviera_install_path> |

| Synopsys VCS       | ACX_VCS_TOOL_PATH       | Set to the Linux executable VCS launcher script path. A default launcher script example can be found in <ace_install>/ examples/simulation_scripts/vcs_launcher.</ace_install>                                                                                                                                                                                                                                                                                                                                                                                            | (Not Supported)                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cadence Xcelium    | ACX_XCELIUM_TOOL_PATH   | Set to the Linux executable Xcelium launcher script path. A default launcher script example can be found in <ace_install>/ examples/simulation_scripts/xcelium_launcher</ace_install>                                                                                                                                                                                                                                                                                                                                                                                     | (Not Supported)                                                                                                                                                                                                                                                                                                                                                                                                                              |

# Configuring the Project Source Files

To run the simulation from ACE, end user design source RTL files and simulation testbench RTL files must be added to the ACE project.

## (i) Project Source File Ordering

The order in which source RTL files are added to an ACE project is the order in which the files will be compiled by the simulator. Therefore, if the chosen simulator requires that modules are defined before they are instantiated, add the lowest-level module definition files first, then the top-level module file last. Once

files are added to the ACE project, they may be re-order via drag-and-drop in the Projects View in the ACE GUI, or by calling the move\_project\_source\_file TCL command.

First, create or restore an ACE project file in the current ACE session. See the ACE Quickstart Tutorial for instructions on how to create the ACE project for the Quickstart example.

In the Projects view, click the project to select it and activate its implementation. Follow these steps to add the design source files for synthesis, simulation, place and route:

1. Click the ( ) Add Source Files toolbar button and select Add RTL Files.

2. In the Add RTL Files dialog, browse to the directory where the end-user design RTL is located and select all of the files

3. Click the **Open** button to add the RTL files to the project.

#### (i) Note

When adding RTL files to an ACE project, adding the top-level ACE library simulation include file for the target device (<ace\_install>/libraries/device\_models/<device>\_simmodels.sv (pag

) is not needed. ACE will automatically locate and add this file to the simulation.

- 4. Click the ( ) Add Source Files toolbar button and select Add Simulation Testbench Files.

- 5. In the "Add Simulation Testbench Files" dialog, browse to the directory where the simulation testbench RTL files are located and select all of the files. For waveform-specific files (\*.do or \*.tcl), select simulatorspecific file only.

#### (i) Notes

- \* . f files may also be added as simulation testbench source files in ACE. When using the default simulation flow, ACE will automatically add these files to the simulator compile commands with the "-f" option. ACE will pre-parse the file to determine of the file should be included in VHDL compile, Verilog compile, or both.

- Additional files maybe added, such as memory initialization files, test vector files, or any other data files that the user design RTL or testbench RTL need to load during the simulation compile or run. When using the default simulation flow, ACE will automatically copy these files into the simulation run directory (<ace\_project\_output\_dir>/<impl>/sim/<sim\_step>/ <tool>/) so they can be loaded using the filename or relative path of "./<filename>".

- 6. Click the **Open** button to add the simulation testbench files to the project.

- 7. Click the ( Save Project toolbar button to save the changes back to the \*.acxprj ACE project file.

The source files are now configured and saved to the ACE project. All of the source files are now visible in the Projects View under the **Source** tree for the project.

# Configuring the Simulation Options

The simulation environment and simulator command-line arguments are configured using the Simulation ACE project options. These options can be configured in the Options View in the ACE GUI, or via the set\_project\_option TCL command.

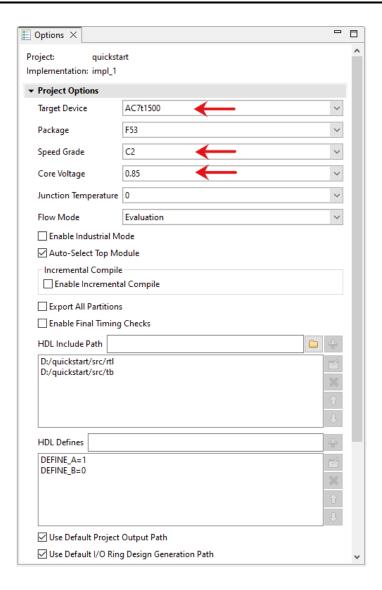

First, configure the top-level project settings. In the Options View, follow these steps to configure the project options:

1. Expand the Project Settings section and select the Target Device, Speed Grade, and Core Voltage for the project.

Figure 2 • ACE Options View

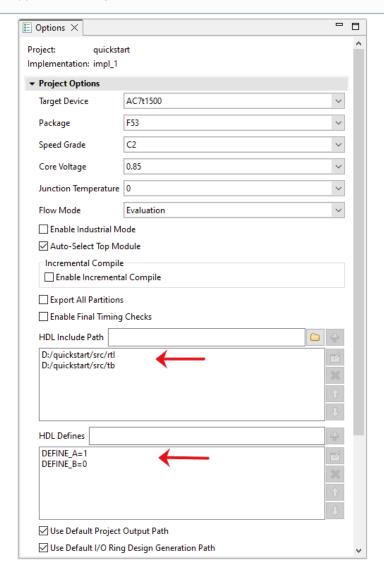

2. In the Project Settings section, scroll down and enter the a semicolon-separated list of directory paths for the HDL Include Path, for example: <test\_dir>/src/rtl;<test\_dir>/src/tb

- The HDL Include Path applies to both synthesis and simulation.

- ACE will automatically add the <ace\_install>/libraries directory to the HDL Include Path; they do need to be entered in the HDL Include Path project option.

- 3. If the end-user design or simulation testbench requires any HDL defines, enter them as a space-separated list in the HDL Defines project option, for example: SIMULATION\_DEFINE\_A=1 SIMULATION\_DEFINE\_B=0

(i) Note

The HDL Defines applies to both synthesis and simulation.

Figure 3 · Setting HDL Include Path and HDL Defines

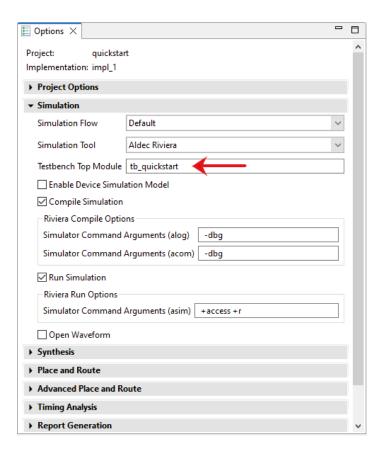

4. Scroll down and expand the Simulation section of options and enter the testbench top module name in the Testbench Top Module field.

Figure 4 · Setting the Testbench Top Module

# Configuring Simulation

There are two types of simulation flows which can be run via the ACE flow steps:

- Default simulation flow this flow is the simplest flow for end users. It uses the simulation scripts built into ACE to configure and run the simulation in the background.

- Custom simulation flow this flow allows the end user to create and use their own custom simulator scripts instead of using the built-in scripts, allowing a custom simulation environment to be connected in to the ACE flow steps.

## **Default Simulation Flow**

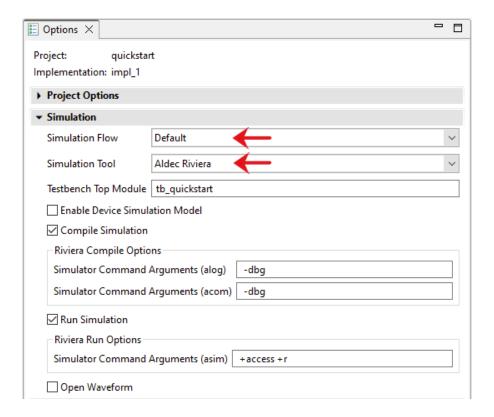

To use the Default simulation flow, first set the Simulation Flow project option to Default. Then select the simulator desired.

Figure 5 • Setting the Simulator Within ACE

ACE currently supports the following simulators for use with the default simulation flow:

- · Siemens QuestaSim

- · Aldec Riviera

- Synopsys VCS

- · Cadence Xcelium

Each simulator tool has its own simulator-specific set of simulation compile options and simulation run options, which allow command-line arguments to passed to the underlying simulator.

All simulators (except Xcelium) support separate compile and run steps. By default, the ACE project options to **Compile Simulation** and **Run Simulation** are enabled. These settings ensure that the simulation flow step first compiles and changes to the source HDL and testbench, and then runs the simulation. Optionally, the **Run Simulation** option can be disabled to perform a compile-only, or disable the **Compile Simulation** to perform a re-run of the previous compile.

The Cadence Xcelium simulation flow step supports running the xrun command for both compile and simulation run.

Optionally, the Open Waveform option can be enabled to open simulator-specific waveform viewer. When enabled, ACE invokes the simulator to load the simulation database that was generated as part of the simulation run. Waveforms are displayed as per the waveform operations specified in waveform (\*.do or \*.tcl) file. The simulator arguments for opening the waveform can be set in Simulator Waveform Arguments option.

Figure 6 · Setting Simulation and Compile Options

If targeting a Speedster device which has a device simulation model, a simulation option to **Enable Device Simulation Model** is activated. If this option is enabled, the simulation flow scripts will automatically include and compile the correct device simulation model files for the target device. ACE will also automatically set the \$ACX\_USE\_DSM environment variable to 1 before calling the simulator tools.

For all devices, ACE automatically sets the following environment variables prior to calling the simulator, so there is no need to set them manually:

- \$ACE\_INSTALL\_DIR the path to the ACE installation

- · \$ACX\_DEVICE\_INSTALL\_DIR the path to the device installation area inside the ACE install

- \$DEVICE the name of the target device for the project

ACE also automatically adds a define to the simulation to specify the selected simulator:

Table 3 · ACE Simulator Defines

| Simulator Tool    | Define            |

|-------------------|-------------------|

| Aldec Riviera     | +define+RIVIERA   |

| Siemens QuestaSim | +define+QUESTASIM |

| Synopsys VCS      | +define+VCS       |

| Cadence Xcelium   | +define+XCELIUM   |

The project is now ready to run through the flow.

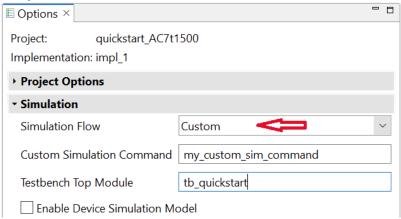

#### **Custom Simulation Flow**

Connecting a custom simulation flow into the ACE flow steps requires some ACE Simulation project options to be configured.

1. Set the Simulation Flow option to **Custom**:

Figure 7 · Selecting the Simulation Flow

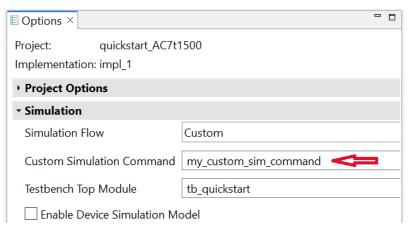

2. Next, configure the Custom Simulation Command. The custom simulation command is the TCL command that the ACE flow step will call to compile and run the simulation. Since there are multiple ACE simulation flow steps (as described below), ACE must pass in the simulation flow step ID to the custom simulation command. Therefore, the custom simulation command must be able to take a "-sim\_step <step>" command-line option, where the values of <step> are: rtl, gate, routed, and final.

There are two options for configuring the Custom Simulation Command:

• Use a TCL exec command to call an external executable script or program.

Use an ACE\_INIT\_SCRIPT to create a custom TCL proc to call the simulator. See Running ACE in the ACE

Users Guide (UG070)<sup>2</sup> for more details.

Figure 8 • Setting the Customer Simulation Command

If targeting a Speedster device which has a device simulation model, a simulation option to **Enable Device**Simulation Model is activated. If this option is enabled, the generated <ace\_project\_output\_dir>/<impl>/

sim/<simstep>/custom/verilog\_filelist.f will automatically include the correct device simulation

model top-level include files for the target device. However, the custom simulation flow needs to account for the

<ace\_install>/system/data/<device>/sim/<device>\_dsm\_incdirs.f file. ACE also automatically

sets the \$ACX\_USE\_DSM environment variable to 1 before calling the simulator.

# Configuring the Simulation Waveform

To configure simulator-specific waveform viewer as part of "Default Simulation Flow", refer to "Configuring the Project Source Files" and "Configuring the Simulation Options" sections under the chapter, Opening Simulator Waveform Viewer in ACE in the *ACE Users Guide* (UG070)<sup>3</sup> for configuring the Project Source Files and Simulation Options.

<sup>2</sup> https://www.achronix.com/documentation/ace-user-guide-ug070 3 https://www.achronix.com/documentation/ace-user-guide-ug070

<sup>1.8</sup> www.achronix.com

Table 4 • Simulator-specific Details for Configuring Simulation Waveform

| Simulator Tool    | Verilog tasks                                                                                    | Simulator GUI Command                                                                                     | Comments                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Aldec Riviera     | \$asdbDump;                                                                                      | vsim -do <input_file></input_file>                                                                        | <ul> <li><input_file> can be *.do or *.tcl file</input_file></li> <li>\$asdbDump generates dataset.asdb file by default. Refer to Riviera Pro Documentation to provide custom ASDB name.</li> <li>To dump signal data, ensure +access +r is passed as an argument in Riviera Run Options to provide read access.</li> </ul>                                                                |

| Siemens QuestaSim | <pre>\$wlfdumpvars(0, <tb_top_name>);</tb_top_name></pre>                                        | <pre>vsim -gui -voptargs=+acc -view <wlf_filename>.wlf -do <input_file></input_file></wlf_filename></pre> | <ul> <li><input_file> can be *.do or *.tcl file</input_file></li> <li><wlf_filename>.wlf is passed as -wlf argument in QuestaSim Run Options.</wlf_filename></li> <li>To dump signal data, ensure -voptargs=+acc is also passed as an argument in QuestaSim Run Options to provide read access.</li> </ul>                                                                                 |

| Synopsys VCS      | <pre>\$vcdplusfile("sim_ou tput_pluson.vpd"); \$vcdpluson(0, <tb_top_name>);</tb_top_name></pre> | <pre>dve -full64 -vpd sim_output_pluson.vpd</pre>                                                         | <ul> <li>The vpd filename is currently<br/>fixed to<br/>sim_output_pluson.vpd</li> </ul>                                                                                                                                                                                                                                                                                                   |

| Cadence Xcelium   | <pre>\$shm_open("<database _name="">.shm"); \$shm_probe("S");</database></pre>                   | <pre>xrun -gui -R -input <input_file>.tcl</input_file></pre>                                              | <ul> <li>This generates a         <database_name>.shm         directory which contains         the .trn file which must be         loaded in SimVision GUI         during waveform viewing.</database_name></li> <li>Use -r <snapshot_name>         instead of -R to provide a         custom snapshot name when         running simulation using         xrun.</snapshot_name></li> </ul> |

| Simulator Tool                                     | Verilog tasks                                                                                                                       | Simulator GUI Command                                                                     | Comments                                                                                            |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| (i) Table Notes                                    |                                                                                                                                     |                                                                                           |                                                                                                     |

| database t<br>and Xceliu<br>waveform<br>as part of | File can be passed as part of<br>Im (* . trn), the database fil<br>(* . do or * . tcl) file. Since<br>simulation testbench files, i | Simulator Waveform Argumentle is loaded using a TCL commander the waveform (*.do or *.tcl | nd and is specified in the<br>) file is added to the ACE project<br>utput directory when Simulation |

when it is passed as input to Simulator Waveform Arguments option.

• If ACX\_RIVIERA\_TOOL\_PATH is set to vsim under the bin/ subdirectory of the Riviera-PRO installation directory, ensure that under Riviera Run Options, use "-c +access+r" to run vsim in batch mode.

# Running the Simulation Flow Steps

ACE provides the following optional simulation flow steps:

**Table 5 · Optional Simulation Flow Steps**

| Name                                     | ID                    |  |

|------------------------------------------|-----------------------|--|

| RTL Simulation                           |                       |  |

| - Run RTL Simulation                     | run_simulation_rtl    |  |

| Synthesis                                |                       |  |

| - Run Gate-level Netlist Simulation      | run_simulation_gate   |  |

| Place and Route                          |                       |  |

| - Generate Post-Route Simulation Netlist | write_netlist_routed  |  |

| - Run Post-Route Netlist Simulation      | run_simulation_routed |  |

| Design Completion                        |                       |  |

| - Generate Final Simulation Netlist      | write_netlist_final   |  |

| - Run Final Netlist Simulation           | run_simulation_final  |  |

Name ID

#### **Table Notes**

All flow step IDs can be executed at the ACE GUI Tcl console (see Tcl Console View in the ACE Users Guide (UG070<sup>4</sup>) or as part of the user Tcl script that can be invoked when running ACE in batch mode. The following Tcl command allows executing the various flow steps IDs listed:

```

run [-step <string>] [-stop_at_step <string>] [-

resume] [-ic <string>]

```

Because advanced users are allowed to create their own flow steps (create\_flow\_step), this list may be a subset of the flow steps available to users. To see a complete list of current flow step IDs, use the Tcl command get\_flow\_steps.

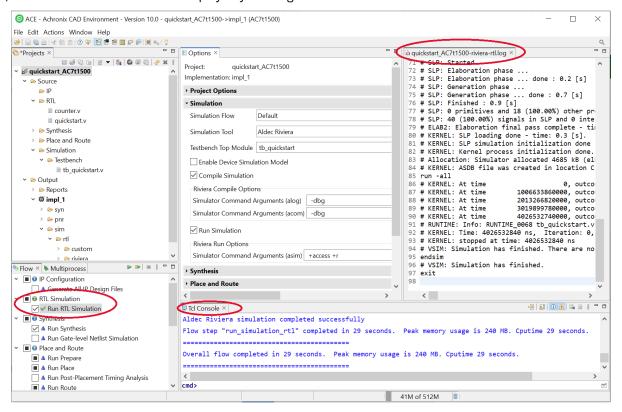

To run a given simulation flow step:

- 1. Enable the flow step by checking the checkbox next to the given flow step in the Flow View in the ACE GUI, or call the enable\_flow\_step <step\_id> TCL command.

- 2. Double-click the flow step in the Flow View in the ACE GUI to run it, or call the run -step <step\_id>TCL command.

1.8

<sup>4</sup> https://www.achronix.com/documentation/ace-user-guide-ug070

Figure 9 · Selecting Flow Steps to be Run

Prior to running the simulation, ACE will change working directories ("cd") into the simulation output directory: <ace\_project\_output\_dir>/<impl>/sim/<sim\_step>/<tool>/. ACE will then change back to the original ACE working directory after the simulation run completes. Make sure any relative file paths in the simulation testbench and user design RTL are relative to this directory.

- \* . f files may also be added as simulation testbench source files in ACE. When using the default simulation flow, ACE will automatically add these files to the simulator compile commands with the "-f" option. ACE will pre-parse the file to determine of the file should be included in VHDL compile, Verilog compile, or both.

- Additional files maybe added, such as memory initialization files, test vector files, or any other data

files that the user design RTL or testbench RTL need to load during the simulation compile or run.

When using the default simulation flow, ACE will automatically copy these files into the simulation run

directory (<ace\_project\_output\_dir>/<impl>/sim/<sim\_step>/<tool>/) so they can be

loaded using the filename or relative path of "./<filename>".

# Viewing the Simulation Outputs

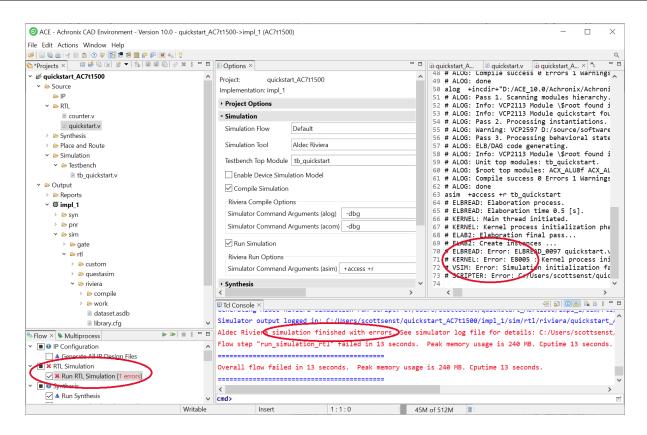

Once a simulation flow step has been run, the simulator log file will automatically be displayed in the ACE GUI Editor Area, and the ACE TCL Console will display any messages about the simulation run.

Figure 10 · Log File and Message Display

If there are any errors in the compile of the simulation, or if the simulator tool returns a non-zero return code, the ACE flow step will error out and stop the flow and ACE will open the simulation log file to the line that shows the error message.

Figure 11 · Simulator Error Message Display

However, depending on the design of the simulation testbench and the simulator, the simulation run could return a zero return code (indicating the simulation passed) while the testbench printed display statements to the simulation log file to indicate there was actually a failure. The ACE built-in simulation script automatically parses the simulation log file to look for error messages using the following regular expressions:

Table 6 · Log File Search RegEx

| Log Message Regex              | Effect                                                                                 |

|--------------------------------|----------------------------------------------------------------------------------------|

| {^Lint-} or {^Warning-}        | Remaining message is ignored until the next blank line                                 |

| {(ERROR[\s:].*)}               | ACE flow step reports an error                                                         |

| {(Error:.*)}                   | ACE flow step reports an error, unless the line also matches {vsim-8604} or {\\$setup} |

| {Test finished with .* errors} | ACE flow step reports an error                                                         |

| Log Message Regex                    | Effect                                                                   |

|--------------------------------------|--------------------------------------------------------------------------|

| Case insensitive {^error}            | ACE flow step reports an error, unless the line also matches {Errors: 0} |

| {Fatal error}                        | ACE flow step reports an error                                           |

| {vsim-PLI-3406}                      |                                                                          |

| Case insensitive {simulation failed} |                                                                          |

| Case insensitive {test failed}       |                                                                          |

If any messages in the simulation log file match these expressions, ACE will treat it as a simulation failure, even though the simulator returned a zero (passing) return code. Please use the regular expressions above as a guideline for developing testbench error messages to ensure ACE will catch them.

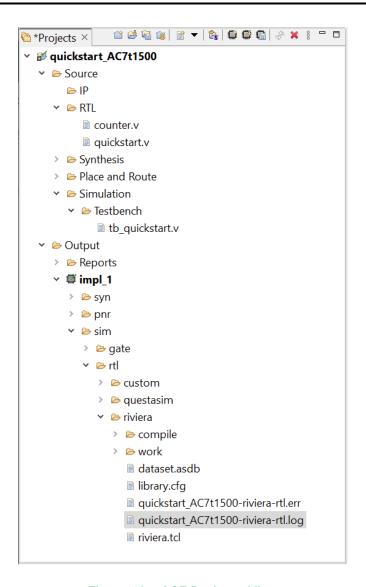

Once simulation has run, any simulation output will be captured in  $\ace_project_output_dir>/<impl>/ sim/<sim_step>/<tool>/, where:$

- $\cdot$  <sim\_step>is one of rtl, gate, routed, or final

- $\cdot$  <tool>is one of riviera, vcs, questasim, xcelium.

Simulation output files can be browsed and opened from within the ACE GUI Projects View.

Figure 12 • ACE Projects View

# Chapter 3: Simulation Outside of ACE

All simulation flow steps in ACE are optional. The end user has the freedom to configure their own custom simulation environment and run simulation of their design outside of ACE. The following sections give examples of how to configure custom simulation environments for each simulator outside of ACE.

# General Project Setup

The following project directory structure is used in this example:

**Table 7 · User Design Project Directory Structure**

| Directory                                                 | Description                                                           |  |

|-----------------------------------------------------------|-----------------------------------------------------------------------|--|

| <b>D</b> coto. y                                          | <b>33331 Pilot</b>                                                    |  |

| <pre><pre><pre><pre>oject_dir&gt;</pre></pre></pre></pre> | Root directory for the user design project                            |  |

| /src                                                      | Source file directory                                                 |  |

| /rtl                                                      | Contains source RTL for the user design                               |  |

| /mem_init_file                                            | Contains memory initialization files for BRAMs or LRAMs               |  |

| /tb                                                       | Contains the simulation testbench for the user design                 |  |

| /syn                                                      | Contains the synthesis project area and output                        |  |

| /ace                                                      | Contains the ACE project area and output                              |  |

| For Siemens Questasim                                     |                                                                       |  |

| /questasim-rtl                                            | Contains the RTL simulation project area and output                   |  |

| /questasim-gat                                            | e Contains the gate-level simulation project area and output          |  |

| /questasim-fin                                            | Contains the post-route (or final) simulation project area and output |  |

| For Aldec Riviera                                         |                                                                       |  |

| /riviera-rtl                                              | Contains the RTL simulation project area and output                   |  |

| /riviera-gate                                             | Contains the gate-level simulation project area and output            |  |

| /riviera-final                                            | Contains the post-route (or final) simulation project area and output |  |

| Directory           | Description                                                           |  |

|---------------------|-----------------------------------------------------------------------|--|

| For Cadence Xcelium |                                                                       |  |

| /xcelium-rtl        | Contains the RTL simulation project area and output                   |  |

| /xcelium-gate       | Contains the gate-level simulation project area and output            |  |

| /xcelium-final      | Contains the post-route (or final) simulation project area and output |  |

| For Synopsys VCS    |                                                                       |  |

| /vcs-rtl            | Contains the RTL simulation project area and output                   |  |

| /vcs-gate           | Contains the gate-level simulation project area and output            |  |

| /vcs-final          | Contains the post-route (or final) simulation project area and output |  |

## General RTL Simulation Flow

#### To perform RTL simulation:

- 1. First create a <sim\_tool>-rtl directory under <project\_dir>/src/.

- 2. Then change directories (cd) to the new <project\_dir>/src/<sim\_tool>-rtl directory (make it the current working directory) to launch subsequent simulator commands from.

- 3. Create the simulation project files and add the source files and library paths. This step can be done by creating a filelist.f with all the library includes, design files, and compiler directives. For an example of this type of file list, see the filelist.f examples in the section, Siemens QuestaSim Simulator Example (page 44) Add the following to the simulator project:

- a. The top-level Achronix technology-specific simulation library include directory path (incdir): <ace\_install\_dir>/libraries.

- b. The top-level Achronix technology-specific simulation library include file, found in <ace\_install\_dir>/libraries/device\_models/<device>\_simmodels.sv.

- c. The behavioral RTL (Verilog or VHDL) source files for the user design.

- d. The top-level simulation testbench (Verilog or VHDL) files.

- 4. Run the simulation and observe the output waveform.

# General Gate-Level Simulation Flow

## To perform gate-level simulation:

1. Create a synthesis project in the <project\_dir>/src/syn/ directory for Synplify Pro to compile and synthesize the source behavioral RTL files to map to Achronix technology. The output of synthesis (Synplify Pro) is a mapped gate-level Verilog netlist in the format that ACE can accept as input for the back-end place-and-route flow. Synplify Pro outputs the synthesized gate-level netlist with the \*.vm extension.

- 2. Create a <sim\_tool>-gate directory under <project\_dir>/src/.

- 3. Change directories (cd) to the new <project\_dir>/src/<sim\_tool>-gate directory (make it the current working directory) to launch subsequent simulator commands from.

- 4. Create the simulation project files and add the source files and library paths. This step can be performed by creating a filelist.f with all the library includes, design files, and compiler directives. For an example of this type of file list, see the filelist.f examples in the section, Siemens QuestaSim Simulator Example (page 44). Add the following to the simulator project:

- a. The top-level Achronix technology-specific simulation library include directory path (incdir): <ace\_install\_dir>/libraries.

- b. The top-level Achronix technology-specific simulation library include file, found in <ace\_install\_dir>/libraries/device\_models/<device>\_simmodels.sv.

- c. The synthesized gate-level Verilog netlist file (\*.vm) for the user design.

- d. The top-level simulation testbench (Verilog or VHDL) files.

- 5. Run the simulation and observe the output waveform.

## General Post-Route Simulation Flow

## To perform post-route simulation:

- 1. Create a project in the <project\_dir>/src/ace/ directory for ACE to place and route the source synthesized gate-level Verilog netlist file (\*.vm file output by Synplify Pro) for the user design. The user design must be run through the place-and-route flow in ACE, and the **Generate Final Simulation Netlist** flow step must be run to output the post-route gate-level netlist from ACE.

The post-route gate-level netlist represents the user design logic after all transformations and optimizations made by the flow prior to bitstream generation. ACE outputs the post-route gate-level netlist into the following location: project\_dir>/src/ace/<active\_impl\_dir>/pnr/output/<design>\_final.v.

This file is encrypted using industry-standard Verilog encryption techniques which are supported by all simulators in the Achronix software tool flow.

- 2. Create a <sim\_tool>-final directory under <project\_dir>/src/.

- 3. Change directories (cd) to the new <project\_dir>/src/<sim\_tool>-final directory (make it the current working directory) to launch subsequent simulator commands from.

- 4. Create the simulation project files and add the source files and library paths This step can be performed by creating a filelist.f with all the library includes, design files, and compiler directives. For an example of this type of file list, see the filelist.f examples in the section, Siemens QuestaSim Simulator Example (page 44). Add the following to the simulator project:

- a. The top-level Achronix technology-specific simulation library include directory path (incdir): <ace\_install\_dir>/libraries

- b. The top-level Achronix technology-specific simulation library include file, found in <ace\_install\_dir>/libraries/device\_models/<device>\_simmodels.sv

- c. The encrypted post-route gate-level Verilog netlist file  $(*\_final.v)$  for the user design.

- d. The top-level simulation testbench (Verilog or VHDL) files

- 5. Run the simulation and observe the output waveform.

# **Example Design Description**

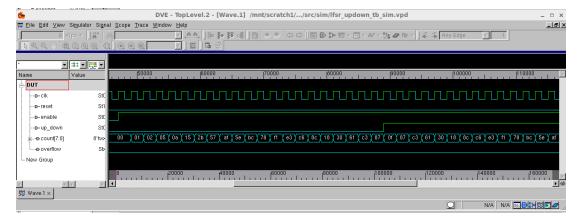

The example design used in various simulation flows described in this user guide instantiates an 8-bit LFSR that can count both up and down. There is an 8-bit output showing the result of the LFSR counter and an overflow signal.

## (i) Note

If simulating a design with BRAM or LRAM and using a memory initialization file, for example, rom\_file.txt, it has to be present in the mem\_init\_files directory, relative to where the simulation tool is invoked for all simulators except Aldec Rivera. Otherwise, the simulators will not be able to find the .txt file and will error out. For Aldec Riviera, refer to the steps described in Aldec Riviera Simulator Example (page 26) regarding a memory initialization file, rom\_file.txt.

## lfsr\_updown\_cnt.v

```

`define CNT_WIDTH 8

module lfsr_updown_cnt (

clk_in

// Clock input

rst

// Reset input

, // Enable input

en

down_not_up, // Up Down input

// Count output

cnt

// Overflow output

ovrflow

);

input clk_in;

input rst;

input en;

input down_not_up;

output [`CNT_WIDTH-1 : 0] cnt;

output

ovrflow;

reg [`CNT_WIDTH-1 : 0]

cnt;

assign ovrflow = (down_not_up) ? (cnt == {{`CNT_WIDTH-1{1'b0}}, 1'b1}) :

(cnt == {1'b1, {`CNT_WIDTH-1{1'b0}}});

always @(posedge clk_in)

begin

if (rst)

cnt <= {`CNT_WIDTH{1'b0}};</pre>

else if (en) begin

if (down_not_up) begin

cnt <= {~(^(cnt & `CNT_WIDTH'b01100011)),cnt[`CNT_WIDTH-1:1]};</pre>

end else begin

```

```

cnt <= {cnt[`CNT_WIDTH-2:0],~(^(cnt & `CNT_WIDTH'b10110001))};

end

end

end

// always @ (posedge clk_in)

endmodule : lfsr_updown_cnt</pre>

```

# Aldec Riviera Simulator Example

## RTL Simulation in Riviera

## Step 1 - Create Simulation Directory

Create a RivieraSim RTL simulation project directory under <project\_dir>/src/, then change directories (cd) to make <project\_dir>/src as the current working directory to launch Riviera from.

## Step 2 - Create a .do File

Create the file riviera\_script.do. The following commands are used in the riviera\_script.do file to compile and simulate the design.

```

#Creates a workspace called riviera_rtl_workspace in current directory. It automatically

changes directory to ./riviera_rtl_workspace

workspace.create riviera_rtl_workspace ./

#Creates a design called lfsr_updown_cnt

workspace.design.create lfsr_updown_cnt ./

#Save workspace

workspace.save

#If using a memory initialization file, copy the <mem_file>.txt to riviera_rtl_workspace

directory like this

# cp ../mem_init_files/mem_file.txt .

#Add the design RTL

design.file.add ../rtl/lfsr_updown_cnt.v

design.file.add ../tb/lfsr_updown_cnt_tb.v

design.file.add /<ACE_INSTALL_DIR>/libraries/device_models/<DEVICE>_simmodels.sv

#Compile design

#design.compile test

alog -work lfsr_updown_cnt -incdir {/<ACE_INSTALL_DIR>/libraries/} -msg 5 -dbg -protect

0 -quiet {/<project_dir>/src/rtl/lfsr_updown_cnt.v} {/<project_dir>/src/tb/

```

```

lfsr_updown_cnt_tb.v} {/<ace_install_path>/libraries/device_models/

<DEVICE>_simmodels.sv}

#Initialize design

#design.simulation.initialize lfsr_updown_cnt_tb

asim -lib lfsr_updown_cnt -dbg -t 0 -dataset {/<project_dir>/src/results/

lfsr_updown_cnt} -datasetname {sim} lfsr_updown_cnt_tb

#Run

run -all

#Saves workspace

workspace.close -save

```

Where <DEVICE> represents the name of the target device, such as AC7t1500.

## Step 3 - Run the Simulation

Run the script riviera\_script.do to compile and simulate the design using the following command. The results are then copied to the sim.log file.

```

/<RIVIERA_INSTALL_DIR>/riviera-pro-2014.06-x86_64/bin/vsimsa -do ./riviera_script.do > sim.log

```

Once simulation is complete, the sim. log displays a message similar to following:

```

sim.log

```

```

# ELAB2: Elaboration final pass complete - time: 0.3 [s].

# KERNEL: Kernel process initialization done.

# Allocation: Simulator allocated 7432 kB (elbread=1450 elab2=5844 kernel=137 sdf=0)

# KERNEL: ASDB file was created in location /simulation_example_design/src/results/

lfsr_updown_cnt/dataset.asdb

run -all

# KERNEL: Reset released

# KERNEL:

87000: rst 0 en 1 updown 0 cnt 11000011 overflow 0

# KERNEL:

129000: rst 0 en 1 updown 1 cnt 00000010 overflow 0

# KERNEL:

SIMULATION PASSED!!

# RUNTIME: Info: RUNTIME_0068 lfsr_updown_cnt_tb.v (66): $finish called.

# KERNEL: Time: 169 ns, Iteration: 1, Instance: /lfsr_updown_cnt_tb, Process:

@INITIAL#41_2@.

# KERNEL: stopped at time: 169 ns

# VSIM: Simulation has finished. There are no more test vectors to simulate.

workspace.close -save

quit

```

# VSIM: Simulation has finished.

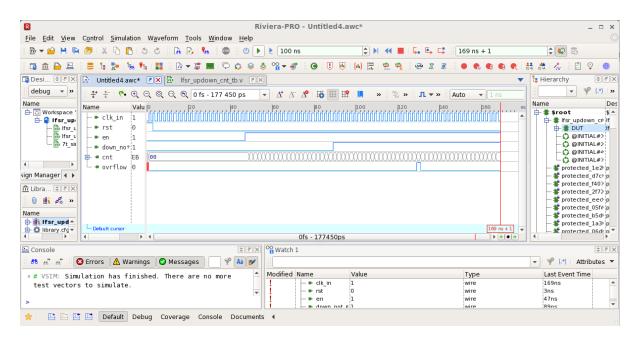

## Step 4 - View the Waveform

In Riviera, in order to view the waveform, simulation has to be rerun. Change the directory to /riviera\_rtl\_workspace. Invoke the Riviera GUI from this directory using the following command.

/<RIVIERA\_INSTALL\_DIR>/riviera-pro-2014.06-x86\_64/bin/riviera &

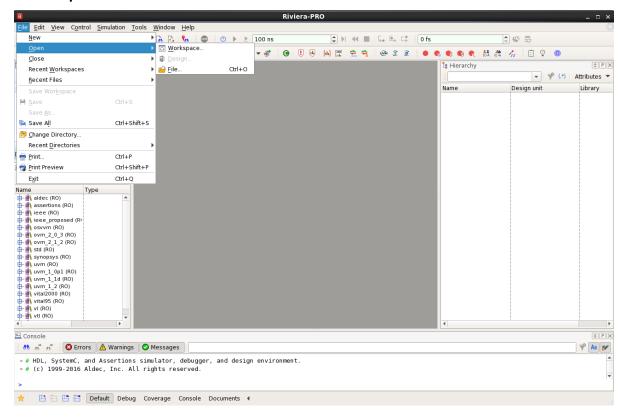

## Step 5 - Open the Workspace

After the Riviera GUI starts up, open the workspace file riviera\_rtl\_workspace.rwsp by selecting **File**  $\rightarrow$  **Open**  $\rightarrow$  **Workspace**.

Figure 13 · Riviera Workspace

#### (i) Note

If using a memory initialization file when simulating BRAM or LRAM, copying the rom\_file.txt to the workspace design directory is important; otherwise, when re-running simulation for viewing waveform, the rom\_file.txt will not be found.

## Step 6 - Initialize the Simulation

Initialize simulation as shown below by right-clicking on the file lfsr\_updown\_cnt\_tb.v in the Libraries pane and selecting Initialize Simulation.

Figure 14 · Initializing Simulation

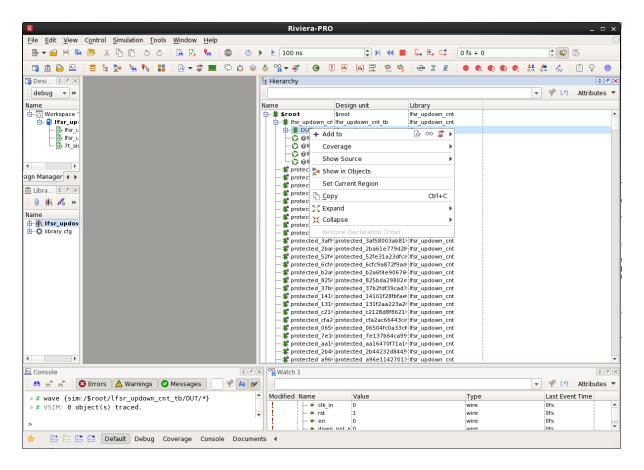

## Step 7 - Add Signals to the Waveform

Add signals to the waveform by right-clicking the DUT in the Hierarchy pane and selecting **Add to** → **Waveform**.

Figure 15 · Adding the Waveform

## Step 8 - View the Waveform

Click the Restart and Run -all button to view the waveform.

Figure 16 · Viewing the Waveform

### Gate-Level Simulation in Riviera

For gate-level simulation, a synthesized netlist has to first be generated using Synplify Pro before performing the simulation.

## Step 1 - Create the Synthesis Project

Create a new project in Synplify under <p

Where <DEVICE> represents the name of the target device, such as AC7t1500.

## Step 2 - Synthesize the Design

Synthesize the design using Synplify Pro. Synplify Pro generates a gate-level netlist with .vm extension, for the example design, the file ct\_dir>/src/syn/rev\_acx/lfsr\_updown\_cnt.vm is generated.

## Step 3 - Create a Workspace

To run the gate-level simulation, create a workspace and run the script as described in RTL Simulation in Riviera (page 26) except that the gate-level simulation uses the mapped netlist

#Creates a workspace called riviera\_gate\_workspace in current directory. It automatically changes directory to ./riviera\_gate\_workspace workspace.create riviera\_gate\_workspace ./

```

#Creates a design called lfsr_updown_cnt

workspace.design.create lfsr_updown_cnt ./

workspace.save

#If using a memory initialization file, copy the <mem_file>.txt to riviera_rtl_workspace

directory like this

# cp ../mem_init_files/mem_file.txt .

#Add the gate netlist

design.file.add ../syn/rev_2/lfsr_updown_cnt.vm

design.file.add ../tb/lfsr_updown_cnt_tb.v

design.file.add /<ACE_INSTALL_DIR>/libraries/device_models/<DEVICE>_simmodels.sv

#Compile design

#design.compile test

alog -work lfsr_updown_cnt -incdir {/<ACE_INSTALL_DIR>/libraries/} -msg 5 -dbg -protect

0 -quiet {/<project_dir>/src/rtl/lfsr_updown_cnt.v} {/<project_dir>/src/tb/

lfsr_updown_cnt_tb.v} {/<ACE_INSTALL_DIR>/libraries/device_models/<DEVICE>_simmodels.sv}

#Initialize design

#design.simulation.initialize lfsr_updown_cnt_tb

asim -lib lfsr_updown_cnt -dbg -t 0 -dataset {//project_dir>/src/results/

lfsr_updown_cnt} -datasetname {sim} lfsr_updown_cnt_tb

#Run

run -all

#Saves workspace

workspace.close -save

quit

```

Where <DEVICE> represents the name of the target device, such as AC7t1500.

## Step 4 - Run the Simulation

Follow Step 3 of RTL Simulation in Riviera (page 26) to run simulation.

## Step 5 - View the Results

Follow Steps 4 to the end of RTL Simulation in Riviera (page 26) to view the waveform.

### Post-Route Simulation in Riviera

For post-route simulation, the synthesized gate-level netlist must first be run through place and route using ACE.

## Step 1 - Create the ACE Project

## Step 2 - Run Place and Route

Run the place and route flow, including the 'Generate Final Simulation Netlist' step to obtain a post-route netlist. In this example, the netlist is generated under cproject\_dir>/src/ace/impl\_1/output/

lfsr updown cnt final.v.

## Step 3 - Create the Workspace

Run the post-route simulation by creating a workspace called final and run the script as described in the RTL Simulation in Riviera (page 26) section except that the post-route simulation uses the final netlist.

```

#Creates a workspace called riviera_final_workspace in current directory. It

automatically changes directory to ./riviera_final_workspace

workspace.create riviera_final_workspace ./

#Creates a design called lfsr_updown_cnt

workspace.design.create lfsr_updown_cnt ./

workspace.save

#Copy the in/exp files

cp ../tb/testvectors.in .

cp ../tb/testvectors.exp .

#If using a memory initialization file, copy the <mem_file>.txt to riviera_rtl_workspace

directory like this

# cp ../mem_init_files/mem_file.txt .

#Add the final netlist

design.file.add ../ace/impl_1/output/lfsr_updown_cnt_final.v

design.file.add ../tb/lfsr_updown_cnt_tb.v

design.file.add /<ACE_INSTALL_DIR>/libraries/device_models/<DEVICE>_simmodels.sv

#Compile design

#design.compile test

alog -work lfsr_updown_cnt -incdir {/<ACE_INSTALL_DIR>/libraries/} -msg 5 -dbg -protect

0 -quiet {/<project_dir>/src/rtl/lfsr_updown_cnt.v} {/<project_dir>/src/tb/

lfsr_updown_cnt_tb.v} {/<ace_install_path>/libraries/device_models/

<DEVICE>_simmodels.sv}

#Initialize design

#design.simulation.initialize lfsr_updown_cnt_tb

asim -lib lfsr_updown_cnt -dbg -t 0 -dataset {/<project_dir>/src/results/

lfsr_updown_cnt} -datasetname {sim} lfsr_updown_cnt_tb

```

```

#Run

run -all

#Saves workspace

workspace.close -save

quit

```

Where <DEVICE> represents the name of the target device, such as AC7t1500.

## Step 4 - Run the Simulation

Follow Step 3 of RTL Simulation in Riviera (page 26) to run simulation.

## Step 5 - View the Results

Follow Steps 4 to the end of RTL Simulation in Riviera (page 26) to view the waveform.

## Cadence Xcelium Simulator Example

### RTL Simulation in Xcelium

In order to run the RTL simulation using the Cadence Xcelium tool, follow the steps below:

#### Caution!

The user must set the `XCELIUM define in order for the Achronix libraries to compile correctly.

## Step 1 - Invoke the Xcelium Tool

Invoke the Cadence tool by specifying the path where the tool is installed using the command xrun and include the libraries path, path to <DEVICE>\_simmodels.sv, top-level RTL file, and testbench as shown below:

```

xrun -access +rwc +incdir+<ACE_INSTALL_DIR>/libraries/ /<ACE_INSTALL_DIR>/libraries/

device_models/<DEVICE>_simmodels.sv project_dir>/src/rtl/lfsr_updown_cnt.v

project_dir>/src/tb/lfsr_updown_cnt_tb.v -gui -sv

```

Where <DEVICE> represents the name of the target device, such as AC7t1500.

**Table 8 • Xcelium Command Options**

| Options               | Required | Description                                                                                                    |  |

|-----------------------|----------|----------------------------------------------------------------------------------------------------------------|--|

| -access +rwc          | Yes      | Turn on read, write and/or connectivity access                                                                 |  |

| -gui                  | No       | Invoke the GUI                                                                                                 |  |

| -sv                   | Yes      | Supports System Verilog constructs                                                                             |  |

|                       |          | This option is to be used only when reading back configuration memory (CMEM) contents during WGL simulations.  |  |

| +define+CMEM_READBACK | No       | (i) Note Simulating CMEM readback function takes on the order of hours to complete with the Xcelium simulator. |  |

When the compilation and elaboration of the design completes successfully, the following message is displayed at the end of xrun. log created in the same directory where the tool is run. Also the graphical debug environment, the SimVision GUI, is launched as shown in Step 2.

```

Building instance specific data structures.

Loading native compiled code:

..... Done

Design hierarchy summary:

Instances Unique

Modules:

837

258

UDPs:

5

0

Timing outputs:

4

1

Registers:

548

3671

Scalar wires:

8208

Expanded wires:

36

695

Vectored wires:

1084

Named events:

40

4

Always blocks:

2821

286

Initial blocks:

517

111

Cont. assignments:

2988

1421

Pseudo assignments:

631

380

Compilation units:

1

1

Simulation timescale:

Writing initial simulation snapshot:

Loading snapshot worklib.bram_outputs:vp ...... Done

SVSEED default: 1

```

ncsim: \*W,DSEM2009: This SystemVerilog design is simulated as per IEEE 1800-2009 SystemVerilog simulation semantics. Use -disable\_sem2009 option for turning off SV 2009 simulation semantics.

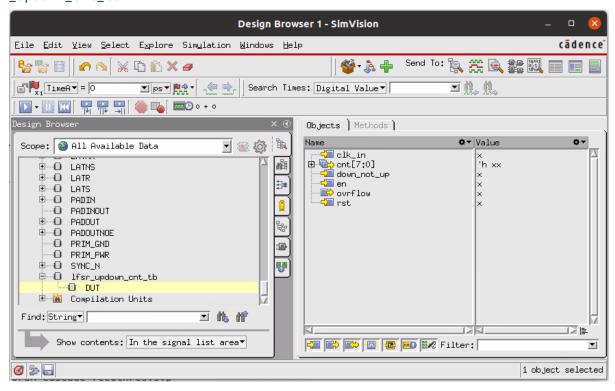

## Step 2 - Add Signals to the Waveform

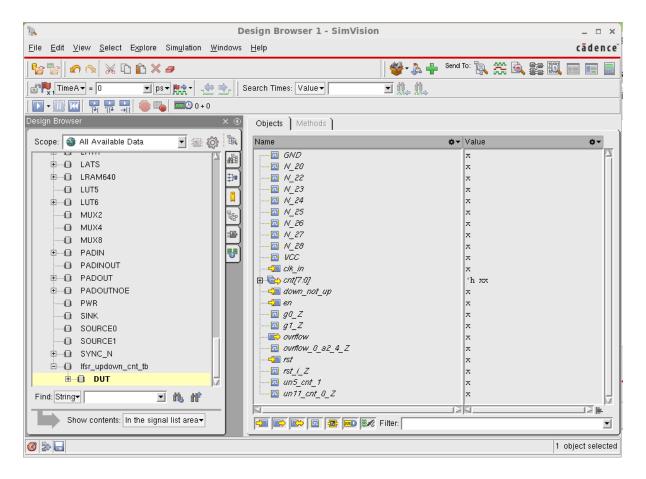

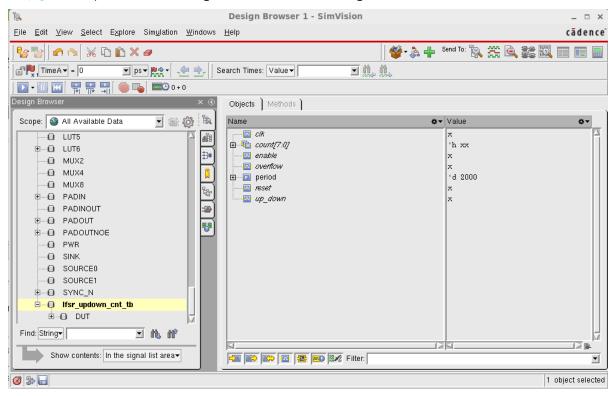

From the Design Browser pane in the SimVision main window, scroll down to and select the testbench, lfsr\_updown\_cnt\_tb.

Figure 17 · SimVision Main Window

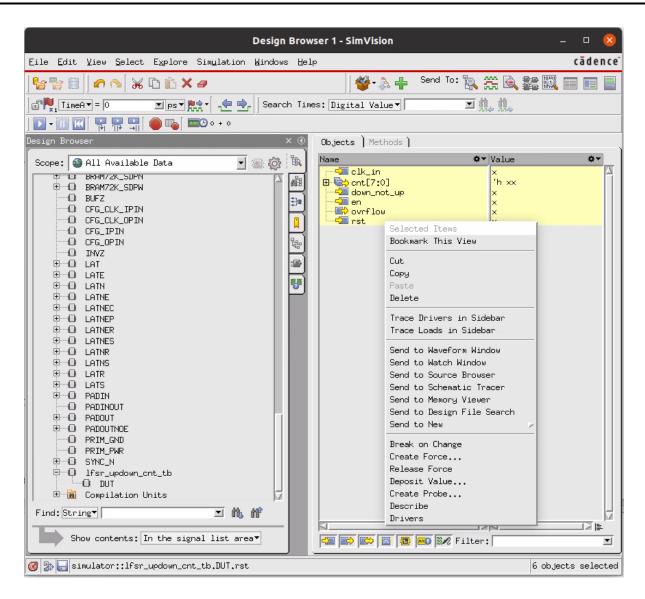

From the Objects view, select the DUT and all of the required signals. Right-click, select **Send to Waveform Window** to add the signals.

Figure 18 · Adding Signals to the Waveform

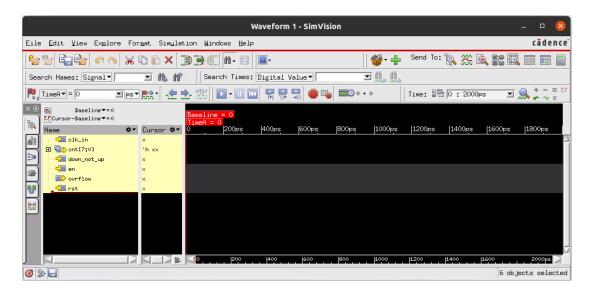

The Waveform window will open as shown below.

Figure 19 · Xcelium Waveform Window

## Step 3 - Run the Simulation

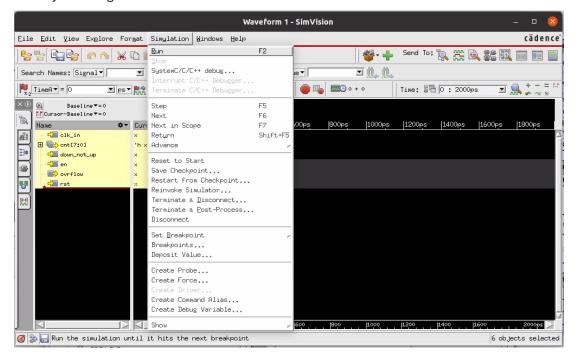

Run simulation by selecting **Simulation** → **Run**.

Figure 20 • Running Simulation

## Step 4 - View the Waveform

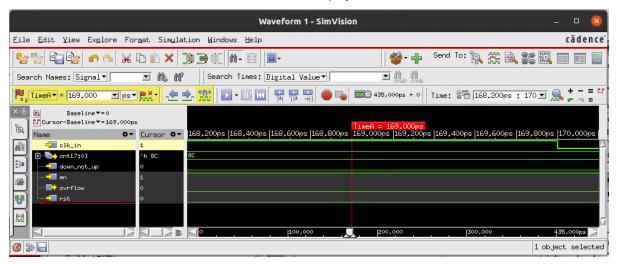

Select the View tab and Zoom Full X. The waveform will be displayed as shown below.

Figure 21 · SimVision Waveform Window

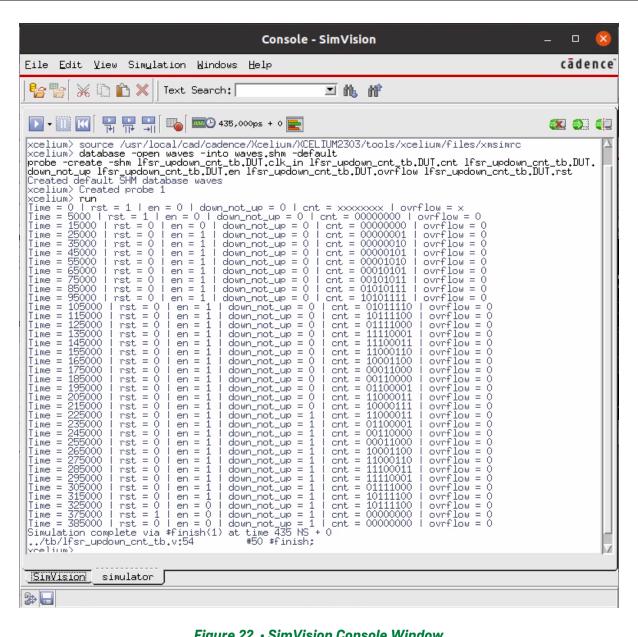

## Step 5 - View Console Messages

The console window displays messages from the testbench. It indicates that the test passed successfully and the simulation completion time.

Figure 22 · SimVision Console Window

#### Gate-Level Simulation in Xcelium

For gate-level simulation, a synthesized netlist has to first be generated using Synplify Pro before performing the simulation.

## Step 1 - Create the Synthesis Project

Create a new project in Synplify under <project\_dir>/src/syn, include <ACE\_INSTALL\_DIR>/libraries/ device\_models/<DEVICE>\_symplify.sv followed by the RTL design files and constraint files.

Where <DEVICE> represents the name of the target device, such as AC7t1500.

## Step 2 - Synthesize the Design

Synthesize the design using Synplify Pro. Synplify Pro generates a gate-level netlist with .vm extension, for the example design, the file <project\_dir>/src/syn/rev\_acx/lfsr\_updown\_cnt.vm is generated.

Rename the gate-level netlist extension from .vm to .v so that the Xcelium simulator understands that it is a Verilog file. Otherwise, the simulator will error out. The example netlist is renamed to lfsr\_updown\_cnt\_gate.v.

## Step 3 - Run Simulation

To run the gate-level simulation, use the same command as described in the RTL Simulation in Xcelium (page 34) section, except that the gate-level simulation uses the mapped netlist lfsr\_updown\_cnt\_gate.v file instead of source RTL files.

#### (i) Note

If ACE-driven synthesis is used, the netlist file will be under the cproject\_output\_dir>/syn/ rev\_acx/directory.

xrun -access +rwc +incdir+<ACE\_INSTALL\_DIR>/libraries/ <ACE\_INSTALL\_DIR>/libraries/ device\_models/<DEVICE>\_simmodels.sv <project\_dir>/src/syn/rev\_acx/lfsr\_updown\_cnt\_gate.v ct\_dir>/src/tb/lfsr\_updown\_cnt\_tb.v -gui -sv

Where <DEVICE> represents the name of the target device, such as AC7t1500.

## Step 4 - View Simulation Results

Follow the same steps described in RTL Simulation in Xcelium (page 34) (Steps 2 to 5) for loading the waveform and viewing the results. When the DUT is selected, the gate-level netlist signals appear as shown below.

Figure 23 · Adding Signals to the Waveform

#### Post-Route Simulation in Xcelium

For post-route simulation, the synthesized gate-level netlist must first be run through place and route using ACE.

## Step 1 - Create the ACE Project

Create a new project in ACE under <project\_dir>/src/ace. Add the gate-level netlist lfsr\_updown\_cnt.vm generated by Synplify Pro plus the constraint files.

## Step 2 - Run Place and Route

Run the place and route flow, including the 'Generate Final Simulation Netlist' step to obtain a post-route netlist. In this example, the netlist is generated under cproject\_dir>/src/ace/impl\_1/output/

lfsr\_updown\_cnt\_final.v.</code>

## Step 3 - Run Simulation

Run the post-route simulation using the same command as was used in RTL and gate-level simulation.

```

xrun -access +rwc +incdir+<ACE_INSTALL_DIR>/libraries/ <ACE_INSTALL_DIR>/libraries/

device_models/<DEVICE>_simmodels.sv project_dir>/src/ace/impl_1/output/

lfsr_updown_cnt_final.v project_dir>/src/tb/lfsr_updown_cnt_tb.v -gui -sv

```

Where <DEVICE> represents the name of the target device, such as AC7t1500.

## Step 4 - View Simulation Results

In post-route simulation, when DUT is selected, no signals are displayed since the post-route netlist file is encrypted. Instead, select the signals under Ifsr\_updown\_cnt\_tb and follow the same steps described in RTL Simulation in Xcelium (page 34) (Steps 2 to 5) for loading the waveform and viewing the results.

Figure 24 • Adding Signals to the Waveform

## Siemens QuestaSim Simulator Example

#### RTL Simulation in QuestaSim

## Step 1 - Create the Project

change directories (cd) to make it the current working directory to launch the simulator from.

## Step 2 - Initialize the Work Library

Initialize the simulator work library using the following QuestaSim command:

vlib ct\_dir>/src/questasim-rtl/work

## Step 3 - Create the File List

Create a filelist. f file to configure the project defines, include directories, and source files. If using VHDL, the file should appear similar to the following example:

#### Warning!

VHDL simulation is only supported at the RTL simulation level. Achronix does not provide the VHDL wrapper libraries for the Verilog library primitives. Behavioral VHDL is recommended. For Achronix IP, such as BRAM or DSP blocks, the ACE GUI provides IP configuration tools which can generate a VHDL wrapper on top of the configured Verilog primitive wrapper.

#### Example vhdl\_filelist.f

```

+incdir+predict_dir>/src/tb

+incdir+project_dir>/src/rtl

+incdir+<ACE_INSTALL_DIR>/libraries

+incdir+<ace_ext_dir>/libraries

<ace_install>/libraries/device_models/<DEVICE>_simmodels.sv

ject_dir>/src/rtl/lfsr_updown_cnt.vhd

project_dir>/src/tb/lfsr_updown_cnt_tb.vhd

```

Where <DEVICE> represents the name of the target device, such as AC7t1500.

If using Verilog, the filelist. f file should appear similar to the following example:

#### Example verilog\_filelist.f

```

+incdir+<project_dir>/src/tb

+incdir+<project_dir>/src/rtl

+incdir+<ACE_INSTALL_DIR>/libraries

+incdir+<ace_ext_dir>/libraries

<ace_install>/libraries/device_models/<DEVICE>_simmodels.sv

<project_dir>/src/rtl/lfsr_updown_cnt.v

<project_dir>/src/tb/lfsr_updown_cnt_tb.v

+libext+.v

```

Where <DEVICE> represents the name of the target device, such as AC7t1500.

## Step 4 - Compile the Design

Before the design can be simulated, it must be compiled. If using VHDL, use the following command to compile the design:

```

vcom -work roject_dir>/src/questasim-rtl/work -f project_dir>/src/questasim-rtl/

vhdl_filelist.f

```

If using Verilog, use the following command to compile the design:

```

vlog -sv -work ct_dir>/src/questasim-rtl/work -mfcu -f project_dir>/src/

questasim-rtl/verilog_filelist.f

```

**Table 9 • Important Command-Line Options**

| Option | Description                                                                        |  |

|--------|------------------------------------------------------------------------------------|--|

| -mfcu  | Multi-file compilation unit, all files in command line make up a compilation unit. |  |

| -SV    | Enable SystemVerilog features and keywords                                         |  |

## Step 5 - Prepare the Simulation Run

Open the simulator and load the compiled design using the following command:

```

vsim -lib project_dir>/src/questasim-rtl/work -gui

```

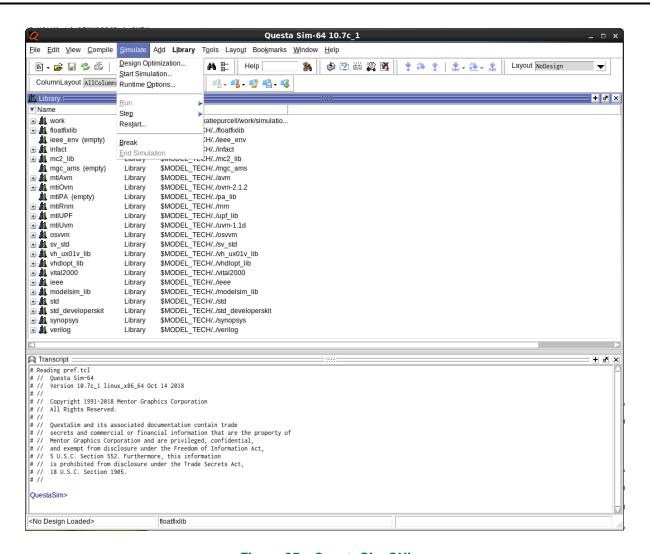

In the simulator GUI, select **Simulate** → **Start Simulation...** to prepare the simulation:

Figure 25 • QuestaSim GUI

## Step 6 - Set up the Waveform

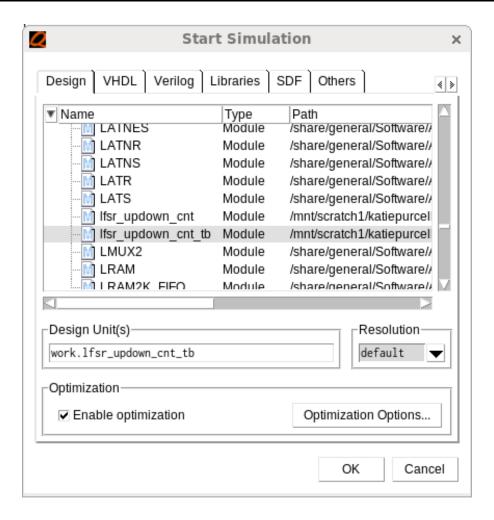

In the Start Simulation dialog, select the <code>lfsr\_updown\_cnt\_tb.v</code> testbench file to run. Click on **Optimization Options...** and choose the option for "Apply full visibility to all modules(full debug mode)" and click **OK**:

Figure 26 • Start Simulation Dialog Box

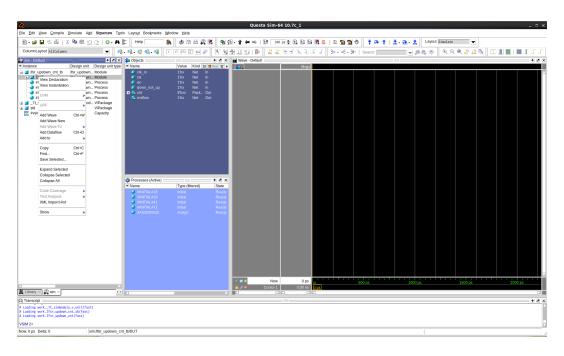

Select the signals to monitor and add them to the waveform by selecting DUT, selecting the desired signals, and then right-clicking and selecting **Add Wave**.

Figure 27 · Selecting Signals to Observe

## Step 7 - Run the Simulation

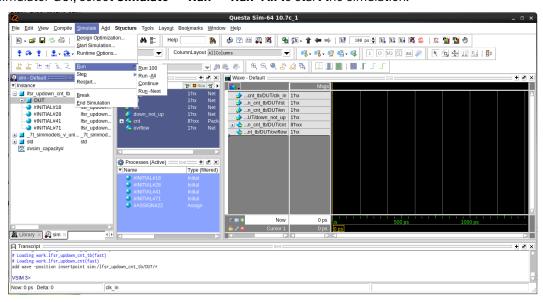

From the simulator GUI, select **Simulate** → **Run** → **Run** -All to start the simulation:

Figure 28 · Starting the Simulation Run

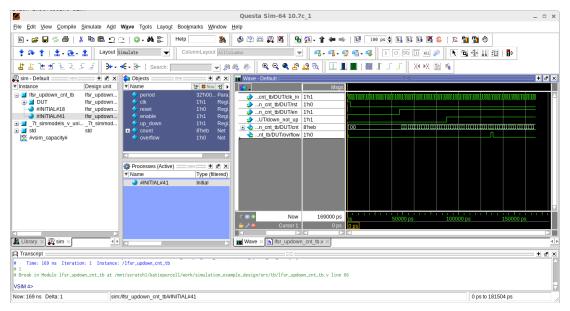

## Step 8 - View the Waveform

Simulation results are written to the waveform viewer for review:

Figure 29 · QuestaSim Waveform Viewer

### Gate-Level Simulation in QuestaSim

For gate-level simulation, a synthesized netlist has to first be generated using Synplify Pro before performing the simulation.

## Step 1 - Create the Synthesis Project

Create a new project in Symplify under ct\_dir>/src/sym, include <ACE\_INSTALL\_DIR>/libraries/

device\_models/CPEVICE>\_symplify, sy followed by the RTL design files and constraint files.

Where <DEVICE> represents the name of the target device, such as AC7t1500.

## Step 2 – Synthesize the Design

Synthesize the design using Synplify Pro. Synplify Pro generates a gate-level netlist with .vm extension, for the example design, the file ct\_dir>/src/syn/rev\_acx/lfsr\_updown\_cnt.vm is generated.

## Step 3 - Set up the Simulation Project

Create a QuestaSim gate-level simulation project directory under cproject\_dir>/src/questasim-gate, then enter this directory to make it the current working directory to launch the simulator from.

## Step 4 - Initialize the Work Library

Initialize the simulator work library using the following QuestaSim command:

```

vlib ct_dir>/src/questasim-gate/work

```

### Step 5 - Create the File List

Create a filelist. f file to configure the project defines, include directories, and source files:

#### Example verilog\_filelist.f

```

+incdir+<project_dir>/src/tb

+incdir+<project_dir>/src/rtl

+incdir+<ACE_INSTALL_DIR>/libraries

+incdir+<ace_ext_dir>/libraries

<ace_install>/libraries/device_models/<DEVICE>_simmodels.sv

<project_dir>/src/syn/rev_acx/lfsr_updown_cnt.vm

<project_dir>/src/tb/lfsr_updown_cnt_tb.v

+libext+.v

```

Where <DEVICE> represents the name of the target device, such as AC7t1500.

## Step 6 - Compile the Design

Compile the design for simulation using the following command:

```

vlog -sv -work ct_dir>/src/questasim-gate/work -mfcu -f project_dir>/src/

questasim-gate/verilog_filelist.f

```

## Step 7 - Prepare the Simulation Run

Open the simulator and load the compiled design using the following command:

```

vsim -lib <project_dir>/src/questasim-gate/work -gui

```

Complete the process by following Steps 6 to the end of RTL Simulation in QuestaSim (page 44) above.

## Post-Route Simulation in QuestaSim

For post-route simulation, the synthesized gate-level netlist must first be run through place and route using ACE.

## Step 1 - Create the ACE Project

## Step 2 - Run Place and Route