# ACE User Guide (UG070)

Achronix CAD Environment (v8.8)

# Copyrights, Trademarks and Disclaimers

Copyright © 2022 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedster and VectorPath are registered trademarks, and Speedcore and Speedchip are trademarks of Achronix Semiconductor Corporation. All other trademarks are the property of their prospective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

### **Achronix Semiconductor Corporation**

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail : info@achronix.com

# **Table of Contents**

| Preface                                                 |

|---------------------------------------------------------|

| About This Guide                                        |

| Related Documents                                       |

| Conventions Used in this Guide                          |

| Chapter - 1: Getting Started                            |

| Introduction                                            |

| ACE Quickstart Tutorial                                 |

| 1. Create your Project                                  |

| 2. Add your Design Files and Set Implementation Options |

| 3. Run the Flow                                         |

| 4. Analyze the Results                                  |

| Congratulations!!!                                      |

| Chapter - 2: Concepts                                   |

| Workbench                                               |

|                                                         |

| Perspectives                                            |

| Projects Perspective                                    |

| IP Configuration Perspective                            |

| NoC Performance Perspective                             |

| Programming and Debug Perspective                       |

| HW Demo Perspective                                     |

| Editors                                                 |

| HTML Report Browser                                     |

| Text Editor                                             |

| VCD Waveform Editor                                     |

| Views                                                   |

| Clock Domains View                                      |

| Clock Regions View                                      |

| Clusters View                                           |

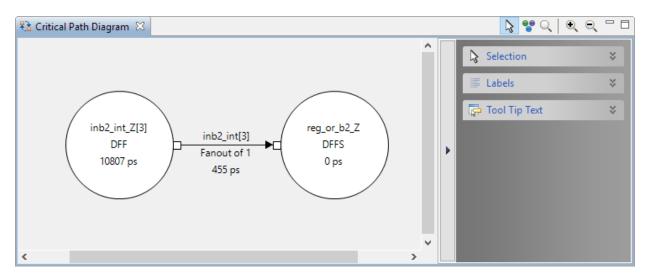

| Critical Path Diagram View                              |

| Critical Paths View                                     |

| Download View                                           |

| Flow View                               |      |

|-----------------------------------------|------|

|                                         | 61   |

| HW Demo View                            | 64   |

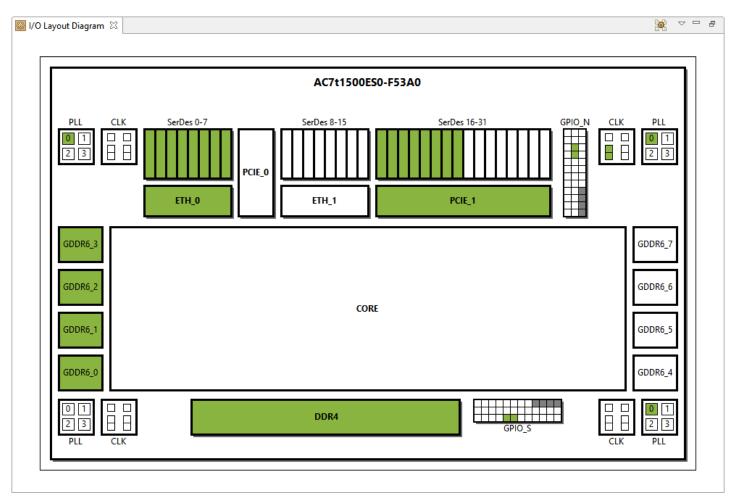

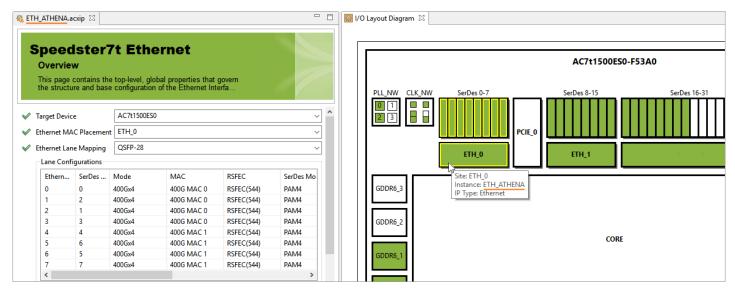

| I/O Designer Toolkit Views              | 66   |

| IO Assignment View                      |      |

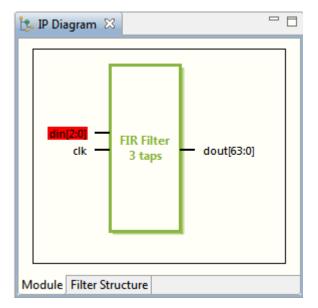

| IP Diagram View                         |      |

| IP Libraries View                       | 80   |

| IP Problems View                        | 81   |

| Multiprocess View                       | 82   |

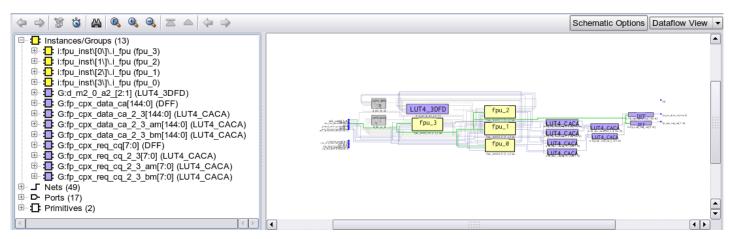

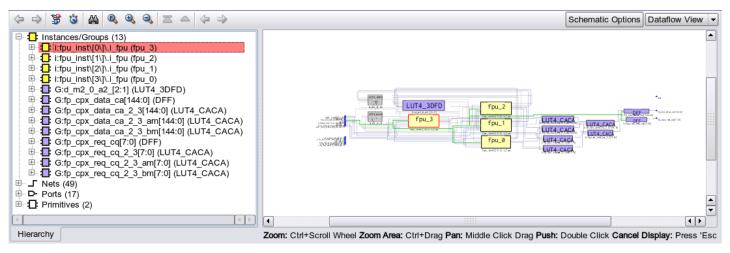

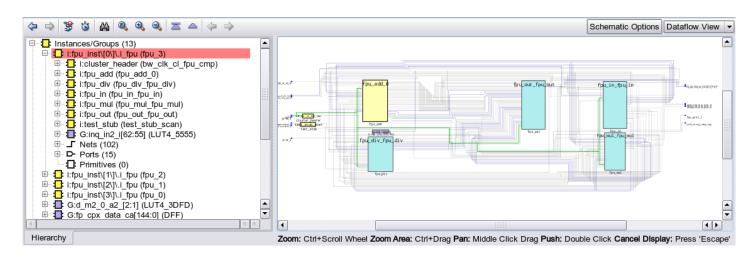

| Netlist Browser View                    | 88   |

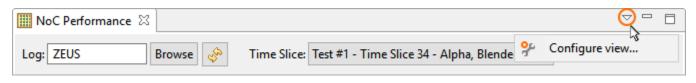

| NoC Performance View                    | 95   |

| NoC Time Slice View                     | 100  |

| Options View                            | 102  |

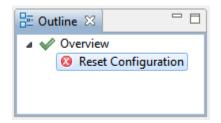

| Outline View                            | 114  |

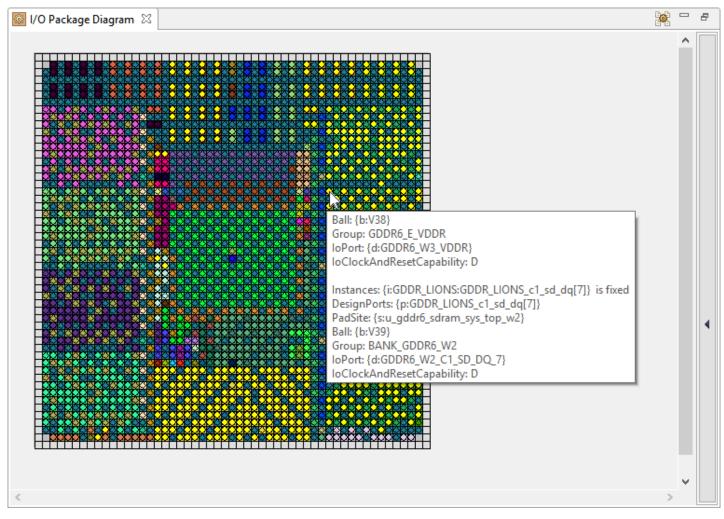

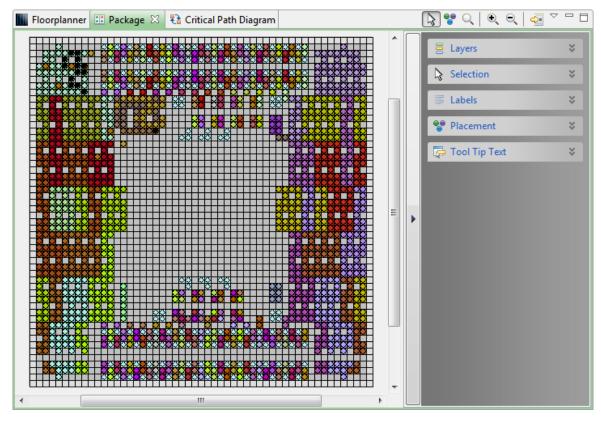

| Package View                            | 115  |

| Partitions View                         | 119  |

| Placement Regions View                  | 122  |

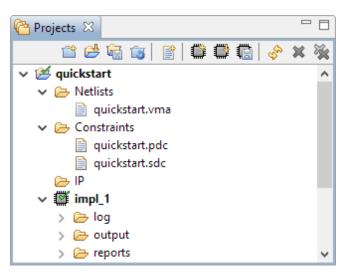

| Projects View                           | 127  |

| Properties View                         | 130  |

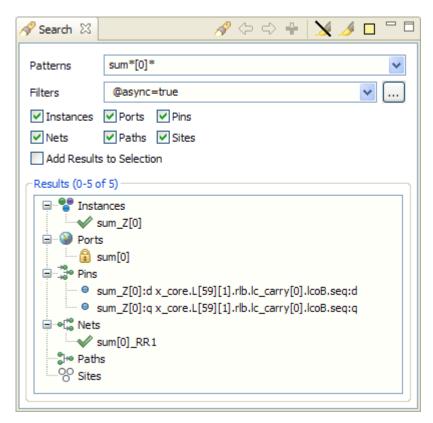

| Search View                             | 134  |

| Selection View                          | 138  |

| Snapshot Debugger View                  | 142  |

| Tcl Console View                        | 147  |

| Dialogs                                 | 1/18 |

| Add Signals to Waveform Viewer Dialog   |      |

| Add Source Files Dialog                 |      |

| Assign Bussed Signal Names Dialog       |      |

| Assign Bussed Values Dialog             |      |

| Configure Clock Pre-Routes Dialog       |      |

| Configure Table Columns Dialog          |      |

| Create a New Constraints File Dialog    |      |

| Create a New Text File Dialog           |      |

| Create Implementation Dialog            |      |

| Create Placement Region Dialog          |      |

| Create Project Dialog                   |      |

| Generate a Pin Assignment Report Dialog |      |

| Generate IP Design Files Dialog         |      |

| Load Project Dialog                     |      |

| New IP Configuration Dialog                                        |     |

|--------------------------------------------------------------------|-----|

| Restore Implementation Dialog                                      | 168 |

| Save Changed Properties Dialog                                     | 169 |

| Save Implementation Dialog                                         | 170 |

| Save Placement Dialog                                              |     |

| Save Placement Regions Dialog                                      | 173 |

| Save Script File As Dialog                                         | 174 |

| Search Filter Builder Dialog                                       | 175 |

| Generate I/O Ring Design Files Dialog                              | 176 |

| Create a SecureShare Zip File Dialog                               |     |

| Load Acxdb Dialog                                                  | 182 |

| Plot Serdes Diagram Dialog                                         | 183 |

| Toolbars                                                           | 185 |

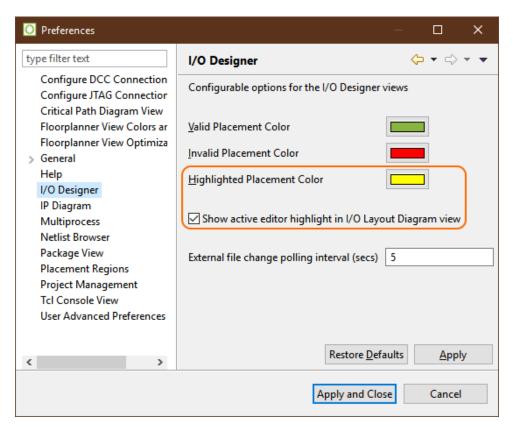

| Preferences                                                        | 186 |

| Configure DCC Connection Preference Page                           | 186 |

| Configure JTAG Connection Preference Page                          |     |

| Critical Path Diagram View Preference Page                         | 188 |

| Floorplanner View Colors and Layers Preference Page                | 190 |

| Floorplanner View Optimizations Preference Page                    | 196 |

| IP Diagram Preference Page                                         | 200 |

| Multiprocess: Configure Custom Job Submission Tool Preference Page | 201 |

| Other Colors and Fonts Preference Page                             | 202 |

| Package View Preference Page                                       | 204 |

| Placement Regions Preference Page                                  | 204 |

| Project Management Preference Page                                 | 206 |

| Tcl Console View Preference Page                                   | 206 |

| Text Editors Preference Page                                       | 207 |

| Projects                                                           | 211 |

| Implementations                                                    |     |

| Project File                                                       | 212 |

| Source Files                                                       | 213 |

| IP Configurations                                                  | 214 |

| Output Files                                                       | 214 |

| Log Files                                                          | 214 |

| Active Project and Implementation                                  | 216 |

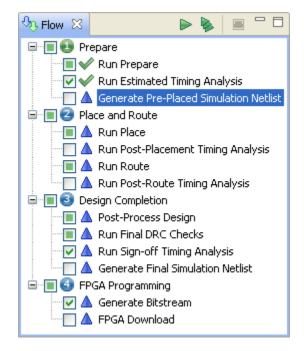

| Flow                                                               | 216 |

| Flow Steps                                                         |     |

| Flow Status                           | 220 |

|---------------------------------------|-----|

| Flow Mode                             | 221 |

| Reports                               |     |

| ' Utilization Report                  |     |

| Pin Assignment Report                 | 222 |

| Clock Report                          |     |

| Timing Report                         | 222 |

| Routing Report                        | 223 |

| Partitions Report                     | 223 |

| Power Dissipation Report              | 223 |

| Design Statistics Report              | 223 |

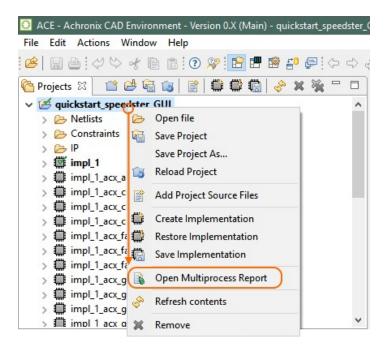

| Multiprocess Summary Report           | 223 |

| Implementation Options Report         | 225 |

| Advanced Concepts                     |     |

| ACE Verilog Attributes                |     |

| Clock Regions                         | 228 |

| Instance States                       | 229 |

| Filter Properties                     | 230 |

| Timing Across All Temperature Corners | 231 |

| ECO Commands                          | 232 |

| Fabric Clusters                       | 244 |

| Chapter - 3: Tasks                    | 245 |

| Running ACE                           |     |

| GUI Mode                              |     |

| Command-line Mode                     | 245 |

| Batch Mode                            | 246 |

| Lab Mode (Reduced Functionality)      | 246 |

| ACE Startup Arguments                 | 246 |

| Working With Perspectives             | 248 |

| Switching Between Perspectives        |     |

| Resetting Perspectives                | 248 |

| Working with Views and Editors        | 248 |

| Opening Views                         |     |

| Moving and Docking Views and Editors  | 248 |

| Rearranging Tabbed Views and Editors  | 249 |

| Detaching Views and Editors           | 250 |

| Tiling Editors                        | 250 |

| Working with Projects and Implementations254Creating Projects255Loading Projects256Removing Projects258Opening Project Files in an Editor258Adding Source Files250Opening Source Files260Opening Source Files261Creating Implementations261Saving Implementations262Copying Implementations262Copying Implementations262Setting the Active Implementation263Removing Output Files in an Editor263Opening Output Files in an Editor263Copying Implementations262Copying Implementations263Configuring Implementation263Opening Output Files in an Editor263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Flow265Running the Flow265Running the Flow265Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from the Console285Command Auto-Completion285Command Auto-Completion285 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Saving Projects255Loading Projects256Removing Project Files in an Editor258Adding Source Files258Adding Source Files260Opening Source Files in an Editor261Creating Implementations261Saving Implementations262Copying Implementations262Setting the Active Implementation263Removing Implementations262Setting the Active Implementation263Copying Implementations263Copying Implementations263Copying Implementations263Configuring Implementations263Configuring Implementation263Coping Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Flow265Running the Flow265Running the Flow266Running the Tol Console284Sending Commands from GUI Actions284Sending Commands from the Console285Command Highlighting285Command Auto-Completion285                                                                                                                     |

| Loading Projects256Removing Project Files in an Editor258Opening Project Files in an Editor258Adding Source Files258Removing Source Files260Opening Source Files in an Editor261Creating Implementations261Saving Implementations261Restoring Implementations262Copying Implementations262Setting the Active Implementation263Removing Implementations263Copying Implementations263Copying Implementations263Configuring Implementation263Configuring Implementation Options263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Flow265Running the Flow265Running the Flow265Running the Flow265Running the Titre Flow265Running the Tol Console280Using the Tcl Console284Sending Commands from GUI Actions285Command Auto-Completion285Command Auto-Completion285                                                                                       |

| Removing Projects258Opening Project Files in an Editor258Adding Source Files258Removing Source Files260Opening Source Files in an Editor261Creating Implementations261Saving Implementations262Copying Implementations262Copying Implementations262Setting the Active Implementation263Removing Implementations263Copying Implementations263Copying Implementations263Configuring Implementation263Configuring Implementation263Configuring Implementation Options263Opening Report Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Flow265Running a Sub-Flow266Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions284Sending Commands from the Console285Command Highlighting285Command Auto-Completion285                                                 |

| Opening Project Files in an Editor258Adding Source Files258Removing Source Files260Opening Source Files in an Editor261Creating Implementations261Saving Implementations261Restoring Implementations262Copying Implementations262Setting the Active Implementation263Removing Implementation263Configuring Implementation263Configuring Implementation263Configuring Implementation263Configuring Implementation263Configuring Implementation Options263Opening Report Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Folow265Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions285Command Highlighting285Command Auto-Completion285                                                                                                                      |

| Adding Source Files258Removing Source Files260Opening Source Files in an Editor261Creating Implementations261Saving Implementations261Restoring Implementations262Copying Implementations262Copying Implementations263Removing Implementations263Configuring Implementation263Configuring Implementation263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Flow265Running the Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                      |

| Removing Source Files260Opening Source Files in an Editor261Creating Implementations261Saving Implementations261Restoring Implementations262Copying Implementations262Setting the Active Implementation263Removing Implementations263Configuring Implementations263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Entire Flow265Running the Entire Flow265Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions284Sending Commands from the Console285Command Auto-Completion285                                                                                                                                                                                                                                                                                   |

| Opening Source Files in an Editor261Creating Implementations261Saving Implementations261Restoring Implementations262Copying Implementations262Setting the Active Implementation263Removing Implementations263Configuring Implementation Options263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Entire Flow265Running the Slow in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                 |

| Creating Implementations261Saving Implementations261Restoring Implementations262Copying Implementations262Setting the Active Implementation263Removing Implementations263Configuring Implementation Options263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Flow265Running the Flow265Running the Entire Flow266Running Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                      |

| Saving Implementations261Restoring Implementations262Copying Implementations262Setting the Active Implementation263Removing Implementations263Configuring Implementation Options263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Flow265Running the Flow265Running the Store Files266Running the Entire Flow265Running the Tcl Console280Using the Tcl Console284Sending Commands from GUI Actions285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                 |

| Restoring Implementations262Copying Implementations262Setting the Active Implementation263Removing Implementation Options263Configuring Implementation Options263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Flow265Running the Entire Flow265Running the Entire Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                               |

| Copying Implementations262Setting the Active Implementation263Removing Implementations263Configuring Implementation Options263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Entire Flow265Running the Intire Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Setting the Active Implementation263Removing Implementations263Configuring Implementation Options263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Entire Flow265Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Removing Implementations263Configuring Implementation Options263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Entire Flow265Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Configuring Implementation Options263Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Entire Flow265Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Opening Output Files in an Editor263Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Entire Flow265Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Opening Report Files in an Editor263Cleaning Projects264Running the Flow265Running the Entire Flow265Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions284Sending Commands from the Console285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Cleaning Projects264Running the Flow265Running the Entire Flow265Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions284Sending Commands from the Console285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Running the Flow265Running the Entire Flow265Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions284Sending Commands from the Console285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Running the Entire Flow265Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions284Sending Commands from the Console285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Running the Entire Flow265Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions284Sending Commands from the Console285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Running a Sub-Flow266Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions284Sending Commands from the Console285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

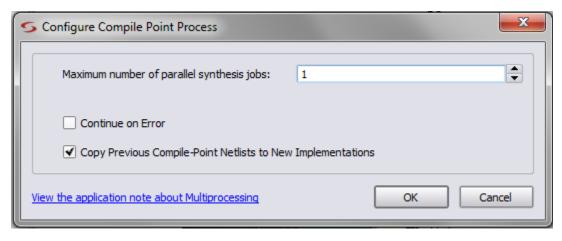

| Running Multiple Flows in Parallel267Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions284Sending Commands from the Console285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Detecting Changes to Project Source Files280Using the Tcl Console284Sending Commands from GUI Actions284Sending Commands from the Console285Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Using the Tcl Console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Sending Commands from GUI Actions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

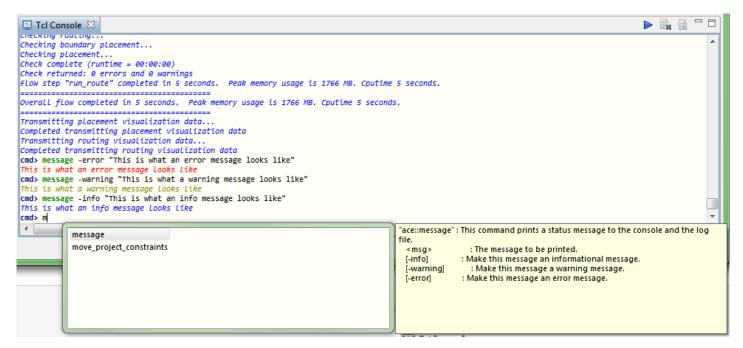

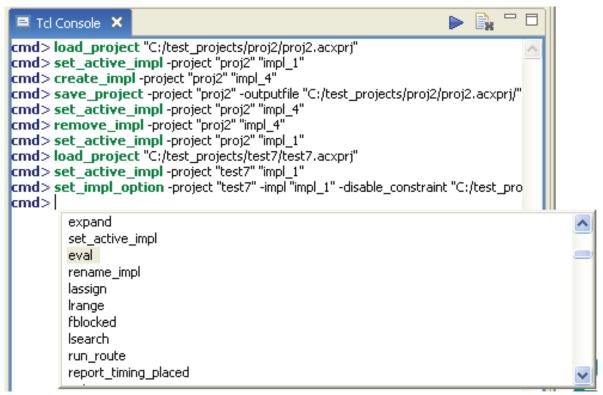

| Sending Commands from the Console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Command Highlighting285Command Auto-Completion285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

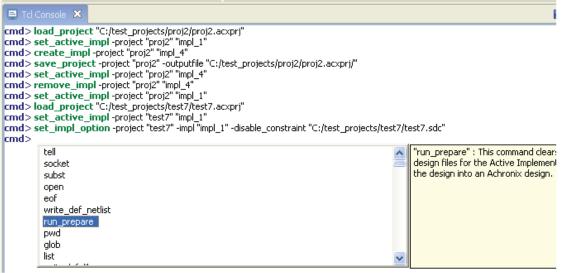

| Command Auto-Completion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Command Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Text Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Clearing the Console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Viewing the ACE Log File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Object Type Prefixes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Creating an IP Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Setting the IP Configuration                           | 290 |

|--------------------------------------------------------|-----|

| Generating the IP Design Files                         | 292 |

| Adding Configuration Files to a Project                | 292 |

| Live Link Tuning for SerDes and Derived Interfaces     | 292 |

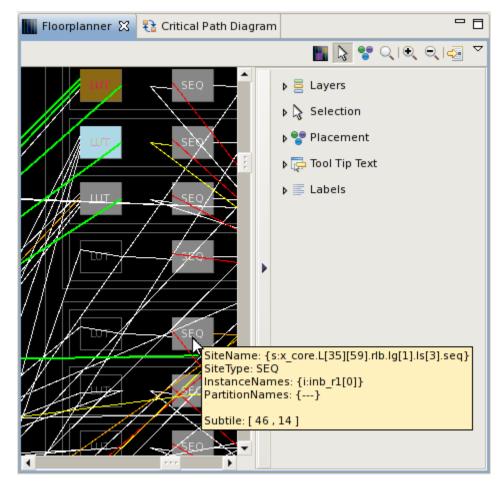

| Viewing the Floorplanner                               | 295 |

| Opening and Closing the Floorplanner's Fly-Out Palette |     |

| Zooming the Floorplanner In and Out                    |     |

| Floorplanner Panning                                   | 295 |

| Selecting Floorplanner Objects                         | 296 |

| Deselecting Floorplanner Objects                       | 297 |

| Toggling Floorplanner Mouse Tools                      | 297 |

| Filtering the Floorplanner View                        | 297 |

| Choosing Floorplanner Object Tooltips                  | 298 |

| Viewing Floorplanner Object Labels                     | 298 |

| Highlighting Objects in the Floorplanner View          | 298 |

| Pre-Placing a Design                                   | 301 |

| Placing an Object                                      |     |

| Changing Between Fixed and Soft Placement              |     |

| Group Placement Mode                                   |     |

| Removing Placement                                     |     |

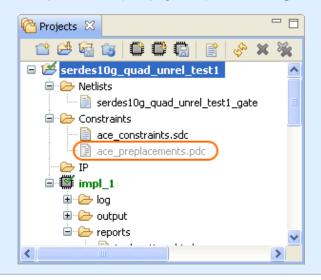

| Saving Pre-Placement Constraints                       |     |

| Using Pre-Placement in the Flow                        |     |

| Analyzing Critical Paths                               | 307 |

| Generating Timing Reports                              |     |

| Highlighting Critical Paths                            |     |

| Selecting Critical Path Objects                        |     |

| Zooming to Critical Paths                              |     |

| Printing Critical Path Details                         |     |

| Using Critical Path Diagrams                           |     |

| Viewing Critical Paths in the Schematic Viewer         |     |

| Applying and Checking Properties                       |     |

| Applying Properties                                    |     |

| Checking Whether Properties Were Applied               |     |

|                                                        |     |

| Configuring External Connections to Hardware           |     |

| Configuring the DCC Connection                         |     |

|                                                        |     |

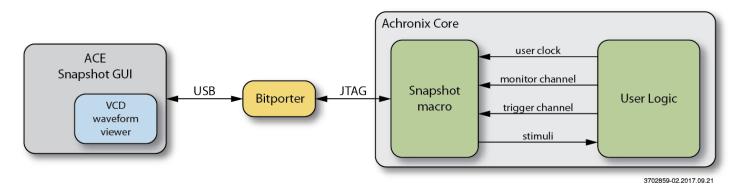

| Running the Snapshot Debugger                          | 318 |

| Snapshot Design Flow                                                 | 319   |

|----------------------------------------------------------------------|-------|

| Accessing the Snapshot Debugger                                      | 320   |

| Configuring the Trigger Pattern                                      | 322   |

| Configuring the Monitor Signals                                      | 325   |

| Configuring Test Stimulus                                            | 326   |

| Configuring Advanced Options                                         | 328   |

| Collecting Samples of the User Design                                | 330   |

| Saving/Loading Snapshot Configurations                               | . 331 |

| Snapshot in Batch Mode                                               | 332   |

| Playing a STAPL File (Programming a Device)                          | 334   |

| Selecting a STAPL File                                               | 334   |

| Selecting Actions and Procedures to be Played                        | 335   |

| Playing an Action                                                    | 335   |

| Optimizing a Design                                                  | 336   |

| Attempting Likely Optimizations Using Option Sets                    |       |

| Placement Regions and Placement Region Constraints                   | 338   |

| Placement Region Preferences                                         |       |

| Creating a New Placement Region                                      | 339   |

| Resizing an Existing Placement Region                                | . 341 |

| Moving an Existing Placement Region                                  | . 341 |

| Assigning Placement Region Constraints                               | 342   |

| Listing all Objects Constrained to a Placement Region                | 343   |

| Removing a Placement Region Constraint from an Object                | 344   |

| Saving Placement Region Definitions and Placement Region Constraints | 344   |

| Deleting Placement Regions                                           | 344   |

| Running the HW Demo                                                  | 344   |

| Installing HW Demo Designs                                           |       |

| Selecting The Target Device And Demo                                 | 345   |

| Loading The Demo JAM File                                            | 346   |

| Displaying Board Status                                              | 346   |

| Control of Running Demonstration Design                              | 346   |

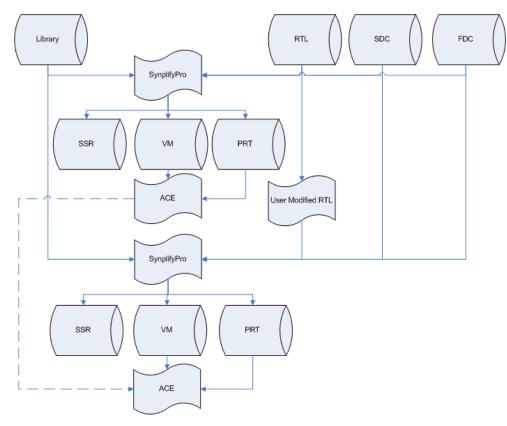

| Using Incremental Compilation (Partitions)                           | 347   |

| Overview of Incremental Compilation and Partitions                   | . 347 |

| Incremental Compile Tutorial                                         | 350   |

| Single-Process Incremental Compile Tutorial                          | . 351 |

| Multiprocess Incremental Compile Tutorial                            | 393   |

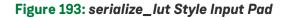

| Automatic Flop Pushing into I/O Pads                                 | 403   |

| Background                                                  |

|-------------------------------------------------------------|

| Capabilities                                                |

| ACE Attributes                                              |

| Examples                                                    |

| Implementation Options                                      |

| Timing Analysis Implications                                |

| Working with Virtual I/O                                    |

| Behavior                                                    |

| Implementation Options                                      |

| Port Attributes                                             |

| Runtime Messages                                            |

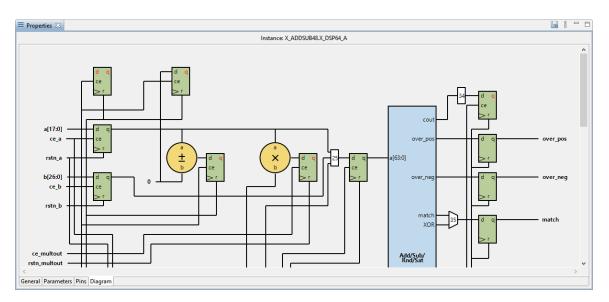

| Schematic View                                              |

| Managing I/Os                                               |

| Accessing Help                                              |

| Accessing Context-Sensitive Help                            |

| Navigating Help Topics                                      |

| Searching Help                                              |

| Using the ACE SecureShare Tool to Create a Support Zip File |

| Importing and Exporting Preferences                         |

| Import Preferences                                          |

| Export Preferences                                          |

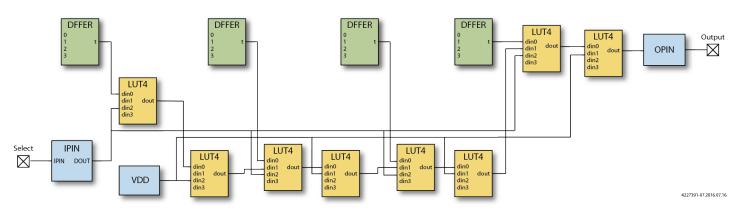

| Plotting Serdes Rx Diagrams using JTAG 428                  |

| Plotting a SerDes Diagram for a SerDes Lane                 |

| Chapter - 4: Tcl Command Reference                          |

| SDC Commands                                                |

| all_clocks                                                  |

| all_inputs                                                  |

| all_outputs                                                 |

| create_clock                                                |

| create_generated_clock                                      |

| get_cells                                                   |

| get_clocks                                                  |

| get_fanout                                                  |

| get_nets                                                    |

| get_pins                                                    |

| get_ports                                                   |

| set_clock_groups                                            |

| set_clock_latency 44        | 41 |

|-----------------------------|----|

| set_clock_uncertainty       | 12 |

| set_data_check              | 13 |

| set_disable_timing          | 15 |

| set_false_path              | 15 |

| set_input_delay 44          | 47 |

| set_input_transition        | 18 |

| set_load 44                 | 18 |

| set_max_delay               | 18 |

| set_min_delay               | 19 |

| set_multicycle_path         | 19 |

| set_output_delay            | 50 |

| Interactive Timing Commands | 52 |

| check_setup                 | 52 |

| prepare_sta                 | 53 |

| report_checks               | 54 |

| report_clock_properties     | 55 |

| reset_sta                   | 56 |

| ACE Tcl Commands            | 57 |

| add_clock_preroute          | 57 |

| add_project_constraints     | 57 |

| add_project_ip              | 58 |

| add_project_netlist         | 58 |

| add_region_find_insts       | 58 |

| add_region_insts            | 59 |

| apply_highlights            | 30 |

| apply_placement             | 30 |

| check_project_status        | 30 |

| clean_project               | 30 |

| clear_arcs                  | 61 |

| clear_drawing               | 31 |

| clear_flow                  | 31 |

| clear_lines                 | 31 |

| clear_ovals                 | 31 |

| clear_polygons              | 32 |

| clear_rectangles            | 32 |

| clear_strings               | 32 |

| clock_info                  | 32 |

| clock_relation               |     |

|------------------------------|-----|

| create_boundary_pins         |     |

| create_equivalent_regions    |     |

| create_flow_step 2           |     |

| create_impl                  |     |

| create_path                  |     |

| create_project               |     |

| create_region                |     |

| deselect                     |     |

| disable_flow_step 4          |     |

| disable_project_constraints  |     |

| display_file 4               | 168 |

| display_netlist              | 168 |

| display_properties           | 169 |

| draw_arc 4                   | 169 |

| draw_line                    | 470 |

| draw_oval                    | 470 |

| draw_polygon                 | 471 |

| draw_rectangle               | 472 |

| draw_string                  | 472 |

| enable_flow_step             | 473 |

| enable_project_constraints   | 473 |

| export_all_partitions        | 473 |

| export_partition             | 474 |

| filter                       | 474 |

| find                         | 475 |

| generate_ioring_design_files | 477 |

| generate_ip_design_files     | 477 |

| generate_route_delay_table   | 478 |

| get_ace_cputime              | 478 |

| get_ace_current_memory_usage | 478 |

| get_ace_ext_dir              | 478 |

| get_ace_ext_lib              | 478 |

| get_ace_peak_memory_usage    | 478 |

| get_ace_version              | 478 |

| get_active_impl              | 479 |

| get_active_project           | 479 |

| get_best_multiprocess_impl 4 | 180 |

| get_clock_region_bounds       | 480               |

|-------------------------------|-------------------|

| get_clock_regions             | 480               |

| get_clock_type                | 480               |

| get_compatible_ordering_codes | 480               |

| get_compatible_placements     | 480               |

| get_current_design            | 481               |

| get_current_partname          | 481               |

| get_efd_file_path             | 481               |

| get_enabled_constraints       | 481               |

| get_fabricdb_path             | 481               |

| get_file_line                 | 482               |

| get_flow_steps                | 482               |

| get_impl_names                | 482               |

| get_impl_option               | 482               |

| get_impl_option_is_supported  | 483               |

| get_inst_partition            | 483               |

| get_inst_region               | 483               |

| get_installation_directory    | 483               |

| get_location                  | 483               |

| get_part_names                | 483               |

| get_partition_changed         | 484               |

| get_partition_force_changed   | 484               |

| get_partition_info            | 484               |

| get_partition_insts           | 485               |

| get_partition_names           | 485               |

| get_partition_timestamp       | 485               |

| get_partition_type            | 485               |

| get_path_property             | 485               |

| get_placement                 | 486               |

| get_pod_names                 | 486               |

| get_project_constraint_files  | 486               |

| get_project_directory         | 487               |

| get_project_ip_files          | 487               |

|                               | 407               |

| get_project_names             |                   |

| get_project_names             | 487               |

|                               | 487<br>487        |

| get_project_netlist_files     | 487<br>487<br>487 |

| get_region_bounds                        | \$ |

|------------------------------------------|----|

| get_region_insts                         | 3  |

| get_regions                              | 9  |

| get_report_sweep_temperature_corners 489 | 9  |

| get_selection                            | Э  |

| get_stapl_actions                        | C  |

| get_techlib_name                         | C  |

| get_techlib_path                         | C  |

| get_techlibdb_path                       | C  |

| get_techlibt_name                        | 1  |

| get_techlibt_path                        | 1  |

| get_techlibx_name                        | 1  |

| get_techlibx_path                        | 1  |

| has_ace_ext_lib                          | 1  |

| has_partitions                           | 2  |

| highlight                                | 2  |

| ignore_cancel                            | 2  |

| initialize_flow                          | 2  |

| insert_delay                             | 2  |

| is_incremental_compile                   | 3  |

| is_labmode                               | 3  |

| load_flowscripts                         | 3  |

| load_project                             | 3  |

| message                                  | 4  |

| move_partition                           | 4  |

| move_project_constraints                 | 4  |

| move_project_netlists                    | 4  |

| optimize_tile                            | ō  |

| redirect                                 | 5  |

| refresh_drawing                          | 5  |

| regenerate_all_ip_design_files           | 5  |

| remove_clock_preroute                    | 3  |

| remove_flow_step                         | 3  |

| remove_impl                              | 3  |

| remove_path                              | 7  |

| remove_project                           | 7  |

| remove_project_constraints               | 7  |

| remove_project_constraints_pvt           | 7  |

| remove_project_ip         | 498 |

|---------------------------|-----|

| remove_project_netlist    | 498 |

| remove_region             | 498 |

| remove_region_insts       | 498 |

| rename_impl               | 499 |

| report_clock_regions      | 499 |

| report_clocks             | 500 |

| report_coverage           | 500 |

| report_design_stats       | 500 |

| report_impl_options       | 501 |

| report_partitions         | 501 |

| report_performance        | 502 |

| report_pins               | 502 |

| report_placement          | 503 |

| report_power              | 503 |

| report_routing            | 504 |

| report_utilization        | 505 |

| reset_impl_option         | 505 |

| restore_impl              | 506 |

| restore_project           | 506 |

| run                       | 507 |

| run_fanout_control        | 507 |

| run_final_drc_checks      | 508 |

| run_fpga_download         | 508 |

| run_generate_bitstream    | 508 |

| run_generate_fullchip_sim | 508 |

| run_generate_netlist      | 509 |

| run_insert_holdbuffers    | 509 |

| run_multiprocess          | 509 |

| run_multiprocess_iterator | 511 |

| run_place                 | 513 |

| run_post_process          | 513 |

| run_prepare               | 513 |

| run_route                 | 513 |

| run_secureshare           | 513 |

| run_snapshot              | 515 |

| run_stapl_action          | 515 |

| run_timing_analysis       | 516 |

| run_tool                     | 517   |

|------------------------------|-------|

| run_un_post_process          | . 517 |

| run_unplace                  | . 517 |

| run_unroute                  | 518   |

| save_clock_preroute          | 518   |

| save_impl                    | 519   |

| save_placement               | 519   |

| save_project                 | 520   |

| save_properties              | 521   |

| save_regions                 | 521   |

| select                       | 521   |

| set_active_impl              | 522   |

| set_clock_type               | 522   |

| set_cluster                  | 523   |

| set_equivalent_pins          | 523   |

| set_flyline_direction        | 523   |

| set_impl_option              | 523   |

| set_max_flyline_fanout       | 524   |

| set_partition_force_changed  | 524   |

| set_partition_info           | 524   |

| set_placement                | 525   |

| set_project_constraints_pvt  | 526   |

| set_property                 | 526   |

| set_region_bounds            | 527   |

| set_region_type              | 527   |

| set_units                    | 527   |

| sleep                        | 528   |

| source_encrypted             | 528   |

| trace_connections            | 528   |

| untar                        | 528   |

| write_bitstream              | 529   |

| write_critical_paths_script  | 530   |

| write_netlist                | 530   |

| write_partition_blackbox     | 531   |

| write_partition_db           | 531   |

| write_tcl_history            | 531   |

| Chapter - 5: Troubleshooting | 532   |

| ACE Exit Error Codes         | 532   |

| Duplicate Names for Arrays                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Definitions/Constraints                                                                                                                 |

| Asynchronous Reset of I/O from the Core                                                                                                       |

| Multi-process Functionality License Requirements                                                                                              |

| Non-ASCII Characters in Path                                                                                                                  |

| Unable to Load Project: Project is Locked                                                                                                     |

| Changing ACE Font Sizes         535           Fonts in Views         535           Fonts in HTML Reports         536                          |

| Unable to Initialize Reserved Module Name List                                                                                                |

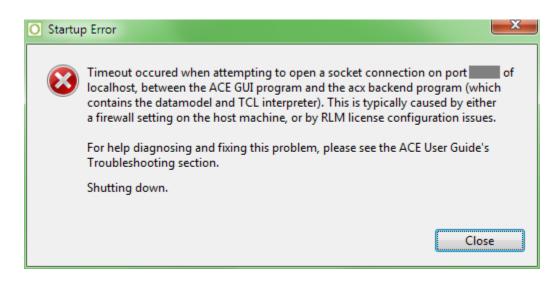

| Startup Error — ACE is Unable to Connect on Port NNNN of Localhost                                                                            |

| Multiprocess Summary Report Shows "No Timing Results Found" for Successfully Run<br>Implementations with Existing Timing Reports              |

| Windows: ACE Incorrectly Reports Read/Write File Permission Problems                                                                          |

| Windows: ACE GUI Shown as "Not Responding" 540                                                                                                |

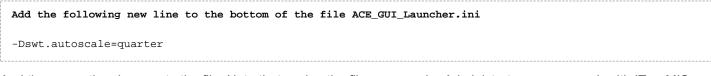

| Windows: Garbage sometimes appears in the Floorplanner View during panning operations (and remains after panning is completed)                |

| Windows: ACE Startup Error Due to Missing DLL Component in Windows 10                                                                         |

| Windows: The icons and buttons in ACE are too small                                                                                           |

| Asking Windows to upscale images and fonts for all applications                                                                               |

| Asking just ACE to upscale images and fonts                                                                                                   |

| Linux: Resource Limits: ACE Reports an OutOfMemory Error, But There is Plenty of Free Memory<br>Available                                     |

| Linux: In the TWM Window Manager, the First Time the ACE GUI is Started After Installation, the ACE Window is So Small Users Might Not See it |

| Linux: Odd Behavior When Using X DISPLAY Forwarding if the X Client and X Server Are More than One Major Revision Apart                       |

| Linux: ACE Menus Do Not Show Icons Next to the Action Names                                                                                   |

| Linux: ACE Ignores LD_LIBRARY_PATH                                                                                                            |

| Linux: Incompatible Default Web Browser                                                                                                       |

| Linux: ACE Requires an Unusually Large Amount of Virtual Memory (Due to WebKit2)                                                              |

| Linux: ACE Draws Slowly Onscreen (or Looks Ugly); Can I Change This Using Themes?                                                             |

| Themes                                                                                                          | 548 |

|-----------------------------------------------------------------------------------------------------------------|-----|

| Animations and Other Effects                                                                                    | 549 |

| Linux: Views and Editors Detach when Dragged Instead of Docking in the Workbench                                | 550 |

| Linux: CDE: Dialogs and Wizards Sometimes Appear Behind the Main ACE Window, Especially After Minimize/Maximize | 550 |

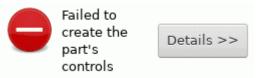

| Linux: "Failed to create the part's controls": Some Views and IP Editors may fail to initialize                 | 551 |

| Upgrading an ACE Installation                                                                                   |     |

| On Linux                                                                                                        | 553 |

| GUI Problems after Upgrading?                                                                                   | 553 |

| Revision History                                                                                                | 555 |

# Preface

# About This Guide

This guide is a reference manual for the Achronix CAD Environment (ACE), used for placing, routing, configuring, and debugging Achronix FPGAs. ACE works in conjunction with third-party synthesis and simulation tools to provide a complete design environment for Achronix FPGAs.

This guide consists of the following chapters:

- Getting Started (see page 22) includes an Introduction to ACE and a quick Tutorial.

- Concepts (see page 24) covers all the basic concepts of ACE, and can be considered a reference manual for the various GUI elements.

- Tasks (see page 245) details how to complete various tasks within the GUI, plus provides the related TCL commands.

- TCL Command Reference (see page 432) provides a complete TCL command reference, including syntax.

- Troubleshooting (see page 532) shows a number of common problems and the recommended solutions.

- Revision History (see page 555) lists the changes to each revision of this document.

# **Related Documents**

The latest version of this document (UG070) is available from your Achronix FAE.

The following documents will always be available for download at http://www.achronix.com/documentation/

- ACE Installation and Licensing Guide (UG002)

- Bitstream Programming and Debug Interface User Guide (UG004)

- Snapshot User Guide (UG016)

- Synthesis User Guide (UG018)

The following supplemental documents, typically available at the Achronix FTP site (login required), should also be consulted for the very latest information:

• ACE Release Notes (RN001)

Further documents are available for each fabric family on both the website and FTP site.

Please consult your Achronix FAE for a complete list of documentation relevant to your Achronix products.

# Conventions Used in this Guide

| Item                                                        | Format                                                                     | Examples                                                                                   |

|-------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Command-line entries                                        | Formatted with a bold fixed-width font, or in a special code block.        | <pre>\$ Open top_level_name.log Command-line code example \$ Open top_level_name.log</pre> |

| File Names                                                  | Formatted with a fixed-width font.                                         | filename.ext                                                                               |

| GUI buttons, menus, menu or list choices, and radio buttons | Formatted with a variable-width bold font.                                 | Select <b>File -&gt; Open</b> , select the desired file, then click <b>OK</b> to continue. |

| Variables                                                   | Formatted with italic emphasis and enclosed by the angle brackets < and >. | <pre><design_dir>/output.log</design_dir></pre>                                            |

| RTL Names                                                   | Formatted with italic emphasis.                                            | read_clk                                                                                   |

| Window and dialog box headings and sub-headings             | Heading formatted in quotation marks.                                      | Under "Output Files", select                                                               |

| Window and dialog box names                                 | Name uses initial caps.                                                    | From the Add Files dialog box,                                                             |

# Chapter - 1: Getting Started

# Introduction

The Achronix implementation flow uses an industry standard RTL synthesis flow based on Synplify-Pro from Synopsis. Working in conjunction with the synthesis tool, Achronix CAD Environment (ACE) provides:

- Placement

- Routing

- Timing Analysis

- Bitstream Generation

- FPGA Configuration

- On-chip Debugging

- Hard/Soft IP Configuration Tools

- Simulation Netlist Generation

# ACE Quickstart Tutorial

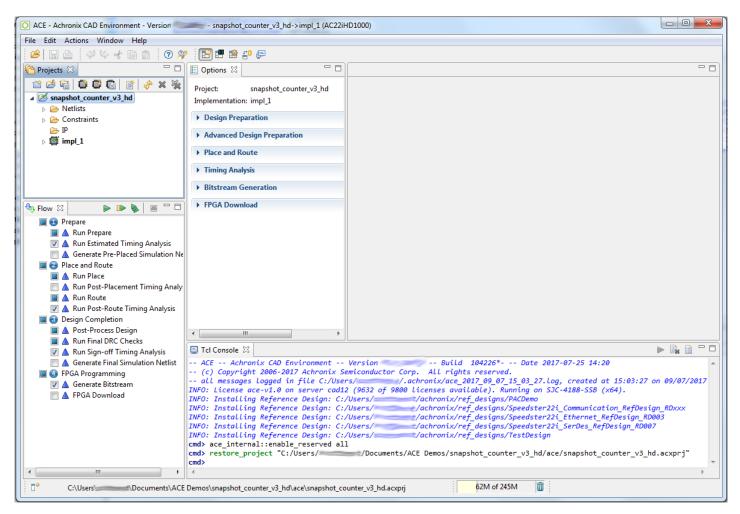

Start by copying all the files from <install\_dir> /Achronix/examples/quickstart/<device> into a new empty directory (<test\_dir>). Use the <device> directory that matches the Target Device implementation option that you select in step 2. Now click the ( 🗗 ) icon in the upper right corner of the Welcome view to minimize these instructions. Then follow these simple steps to complete your first design in ACE.

### 1. Create your Project

In the Projects View (see page 127), click the **Create Project** ( $\stackrel{\text{(in)}}{=}$ ) toolbar button. In the Create Project Dialog (see page 163), enter (or browse to) the path to <*test\_dir*> in the Project Directory field. Enter "quickstart" in the Project Name field and click **OK**. You should now see your new project show up in the Projects view.

See Creating Projects (see page 254) or Working with Projects and Implementations (see page 254) for more details.

### 2. Add your Design Files and Set Implementation Options

In the Projects View, click the "quickstart" project to select it. Now click the **Add Files** ( ) toolbar button. In the Add Source Files Dialog (see page 150), select quickstart.vma, quickstart.pdc, and quickstart.sdc by holding down the **CTRL** key and clicking each item. Now click the **Open** button to add the files to your project. Finally, in the Options view, expand the **Design Preparation** section and select the **Target Device** that matches the set of design files that you copied earlier. You now have a project that is ready to run through the flow!

See Adding Source Files (see page 258) or Working with Projects and Implementations (see page 254) for more details.

### 3. Run the Flow

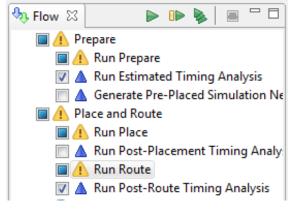

In the Flow View (see page 61), click the **Run Flow** ( ) toolbar button. Output from the Flow (see page 216) is shown in the Tcl Console View (see page 147). When the flow is finished running, you see the Flow Steps (see page 216) in the Flow View updated with a green check mark ( ) to indicate success, and all newly generated reports are displayed in the editor area.

See the Flow (see page 216) concept or Running the Flow (see page 265) for more details.

### 4. Analyze the Results

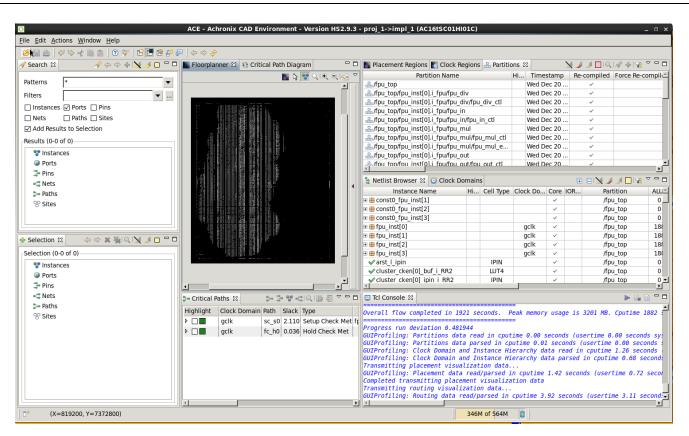

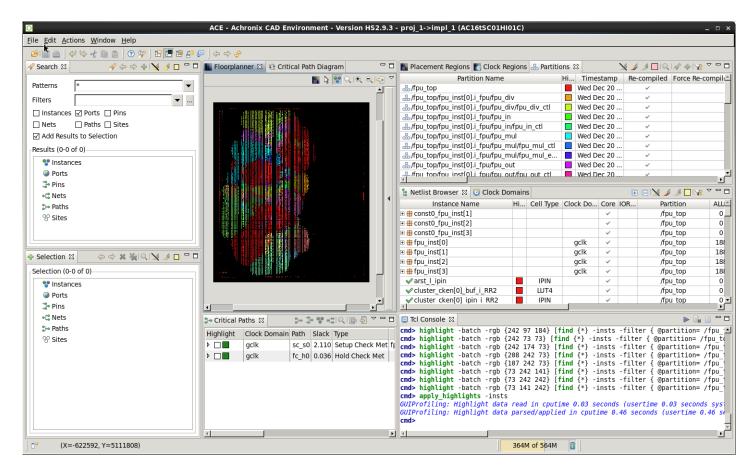

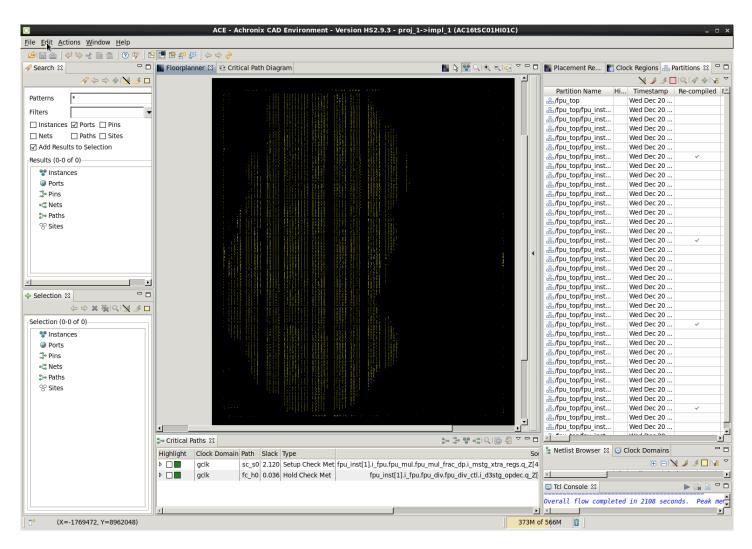

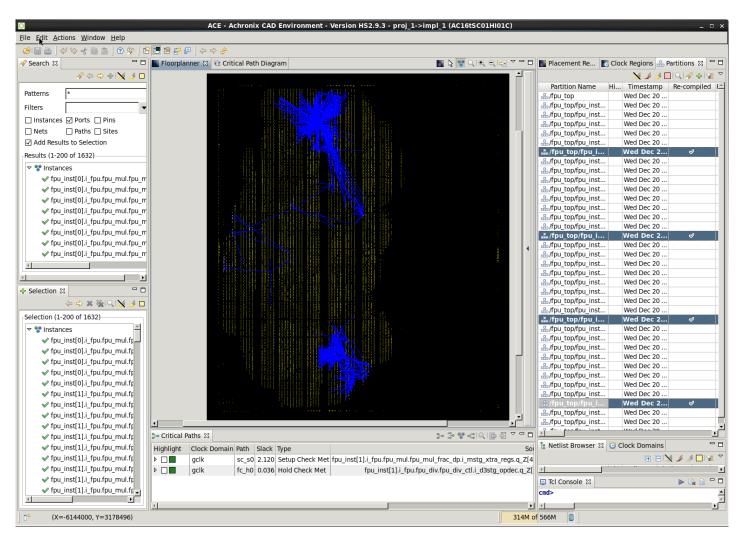

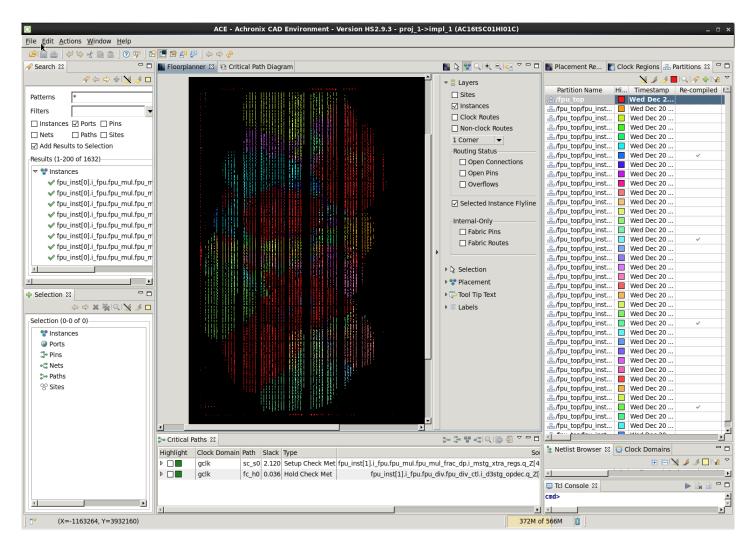

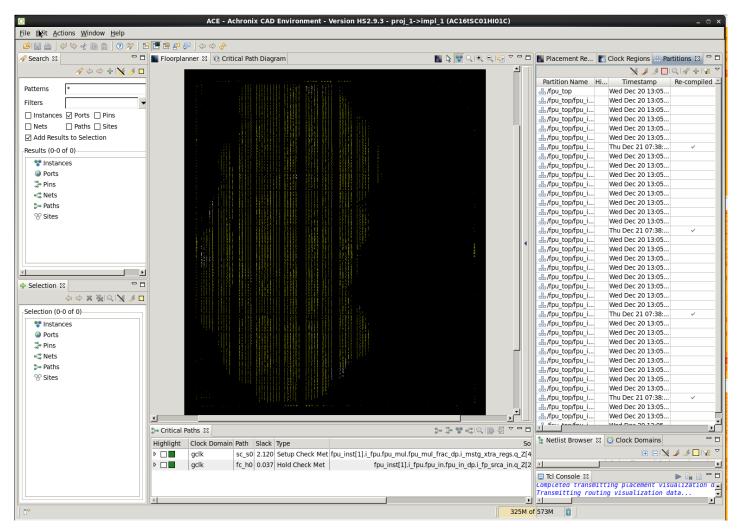

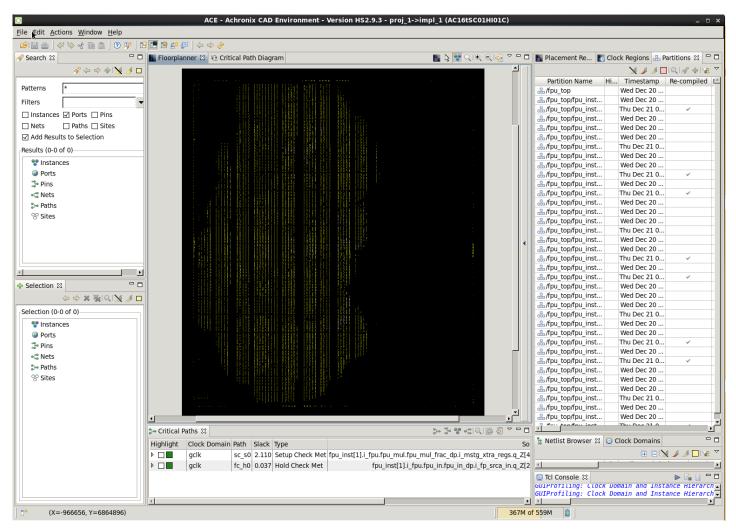

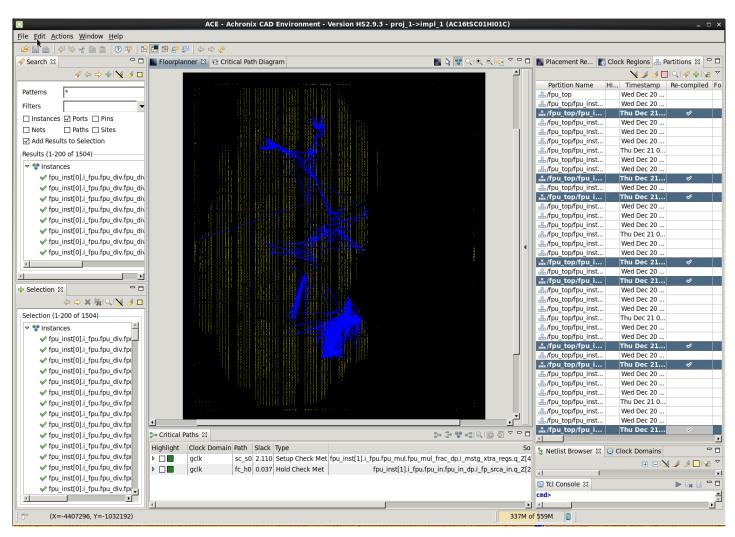

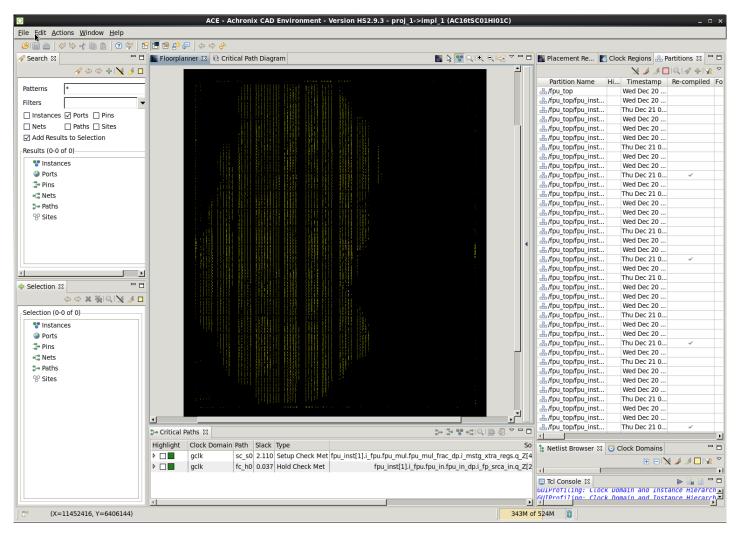

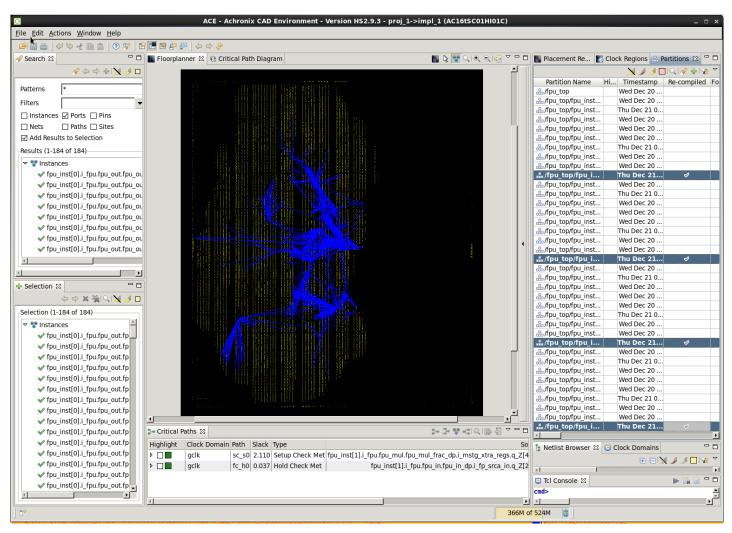

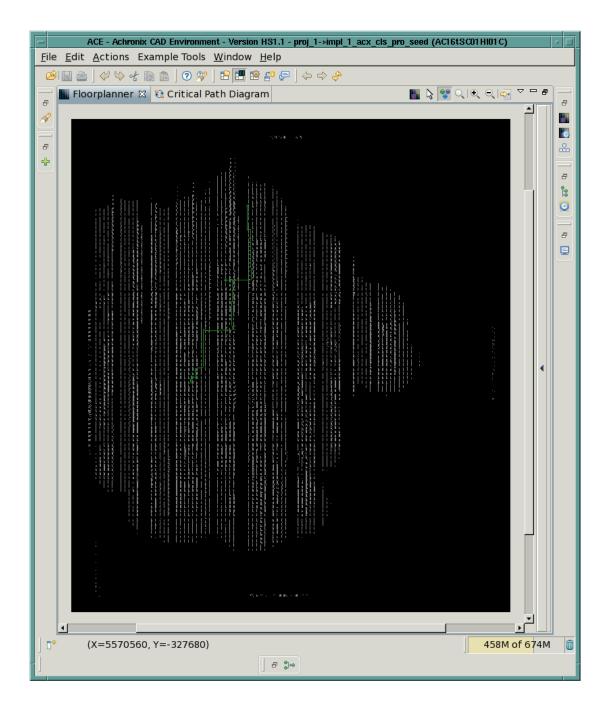

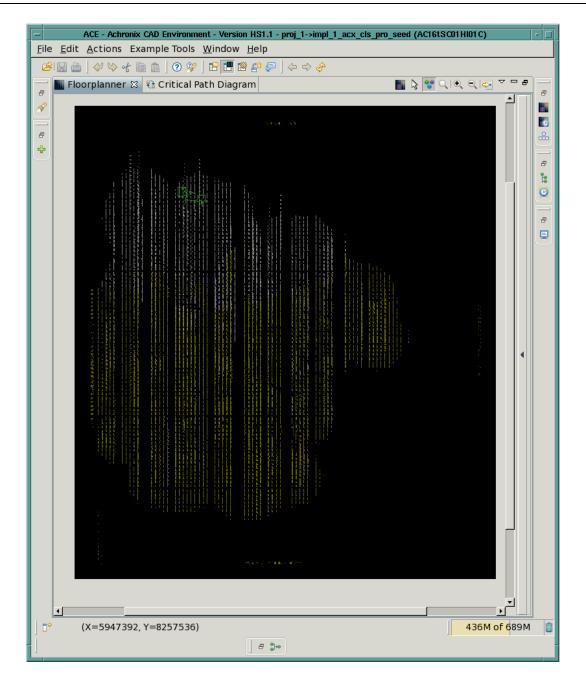

On the main toolbar, click the **Floorplanner Perspective** (  $\square$ ) toolbar button. Within this perspective, use the Critical Paths View (see page 48) to analyze critical paths and highlight them in the Floorplanner View (see page 53). Clicking the **Zoom To Path** (  $\bigcirc$  ) toolbar button in the Critical Paths View zooms the Floorplanner View (see page 53) to the path currently selected in the Critical Paths View. Use the Search View (see page 134) and Selection View (see page 138) to locate objects of interest. Clicking the **Zoom To Selection** (  $\bigcirc$  ) toolbar button in the Selection View zooms the Floorplanner View to the objects in the current selection set.

### Congratulations!!!

You have successfully completed a design in ACE!

# Chapter - 2: Concepts

# Workbench

The term Workbench refers to the desktop development environment within ACE. The Workbench aims to achieve seamless tool integration by providing a common platform for the creation, management, and navigation of project resources.

Each Workbench window contains one or more Perspectives (see page 24). Perspectives contain views (see page 31) and editors (see page 26) and control what appears in certain menus and tool bars. More than one Workbench window can exist on the desktop at any given time.

# Perspectives

There are many different kinds of information a user must view within ACE. Perspectives are used to filter the information into usable logically consistent groupings. A perspective provides a set of functionality aimed at accomplishing a specific type of task or works with specific types of resources. A perspective defines the initial set and layout of views (see page 31), editors (see page 26), menus, and toolbars in the Workbench (see page 24) window.

For example, the Projects perspective combines views (see page 31) commonly used while managing project source files, while the Floorplanner perspective contains the views that are used while viewing chip layout and floorplanning information. Users frequently switch perspectives while working inside the Workbench (see page 24).

Within the Workbench (see page 24) window, all perspectives share the same set of Editors (see page 26).