# Speedster7t Ethernet User Guide (UG097)

**Speedster FPGAs**

**Preliminary Data**

# Copyrights, Trademarks and Disclaimers

Copyright © 2022 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedster and VectorPath are registered trademarks, and Speedcore and Speedchip are trademarks of Achronix Semiconductor Corporation. All other trademarks are the property of their prospective owners. All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

#### **Preliminary Data**

This document contains preliminary information and is subject to change without notice. Information provided herein is based on internal engineering specifications and/or initial characterization data.

#### **Achronix Semiconductor Corporation**

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail: info@achronix.com

# Table of Contents

| Chapter - 1: Introduction              | . 7 |

|----------------------------------------|-----|

| Summary                                | . 7 |

| Features                               | . 7 |

| 400G/200G PCS Layer                    |     |

| 100G PCS Layer                         | . 7 |

| 10/25/40/50G PCS Layers                | . 7 |

| Reed-Solomon FEC (RS-FEC)              |     |

| MAC                                    |     |

| System Multirate and Multichannel      | . 8 |

| Architecture                           | . 8 |

| PMA (SerDes)                           | . 9 |

| PCS                                    | 10  |

| MAC                                    | 10  |

| Specifications                         | 10  |

| Channels                               | 10  |

| Bitmux                                 | 11  |

| SerDes                                 | 11  |

| System Latency                         | 13  |

| Chapter - 2: System Architecture       | 14  |

| Ethernet Interface System Architecture | 14  |

| Data Flow                              | 15  |

| Data Connections                       | 16  |

| Status and Flow Control Signals        | 16  |

| Control and Status Registers           | 16  |

| IP Generation and Configuration        | 17  |

| EIU                                    | 17  |

| NAP Columns                            | 17  |

| Memory Buffering                       | 17  |

| Clocks                                 | 18  |

| Packet and Quad Segmented Modes        | 18  |

| Configuration                          | 19  |

| NAP Data Connections                   | 19  |

| Timestamp                        | 20 |

|----------------------------------|----|

| Transmit Flags                   | 20 |

| Receive Flags                    |    |

| Transmit Clock Frequencies       | 24 |

| Receive Clock Frequencies        |    |

| Combined TX and RX Frequencies   | 27 |

| Express and Pre-emptive MACs     |    |

| Flow Control                     | 28 |

| Transmit Rate Limiting           | 28 |

| Receive Flow Control             | 29 |

| Direct Connect Interface Signals |    |

| MAC Identifier                   | 30 |

| Chapter - 3: 2D NoC Connectivity | 34 |

| Packet Mode                      | 34 |

| Quad-Segmented Mode              | 36 |

| Chapter - 4: Ethernet Clocks     | 39 |

| Clock Domains                    |    |

| Clock Frequencies                | 40 |

| Reference and FIFO Clocks        |    |

| SerDes Clocks                    | 41 |

| Selecting Clock Frequencies      | 41 |

| Flow Control                     | 41 |

| Transmit Overrate 100G and Below | 42 |

| 200G and Above                   | 44 |

| Chapter - 5: Register Map        | 45 |

| Introduction                     | 45 |

| Global Address Space             | 45 |

| CSR Addressing                   | 45 |

| Target ID Addressing             |    |

| IP ID Addressing                 |    |

| Address Dictionary               | 46 |

| Individual Module Address Maps   |    |

| System Control                   | 47 |

## Speedster7t Ethernet User Guide (UG097)

|                   | Quad MAC                                     |    |

|-------------------|----------------------------------------------|----|

| (                 | Quad PCS                                     | 58 |

| Chap <sup>•</sup> | ter - 6: IEEE Timestamping                   | 68 |

| Ove               | rview                                        | 68 |

|                   | Enabling Timestamping within ACE             |    |

| F                 | rame Timestamping                            | 71 |

| IEEE              | 1588 TX One-Step Frame Field Update          | 72 |

|                   | Overview                                     |    |

|                   | EEE 1588 Message Header Structure            |    |

|                   | Jpdate Function Overview                     |    |

|                   | ransparent Clock Concepts                    |    |

|                   | Locally Generated Event Messages             |    |

|                   | ransport Layer Identification                |    |

|                   | JDP Payload Checksum Correction Field Update |    |

|                   | · ·                                          |    |

| Chap <sup>,</sup> | ter - 7: Ethernet IP Support in ACE          | 81 |

| Ove               | rview                                        | 81 |

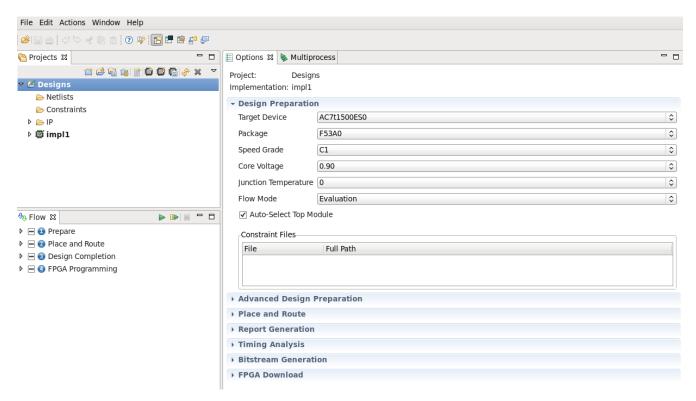

| Step              | o 1 – Creating a Project                     | 81 |

| Step              | 2 – Configure and Generate ACE IP            | 82 |

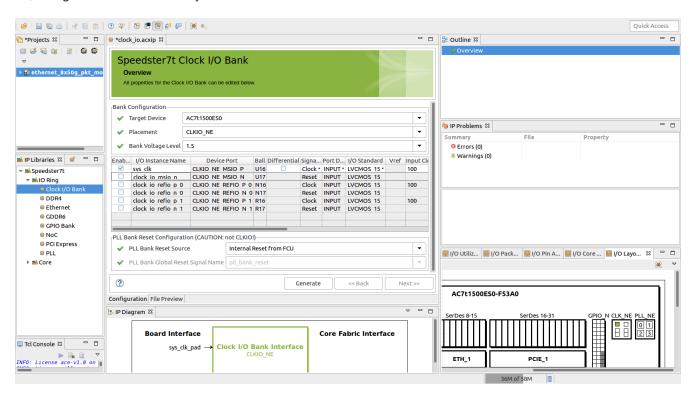

| S                 | System Clock Input                           | 82 |

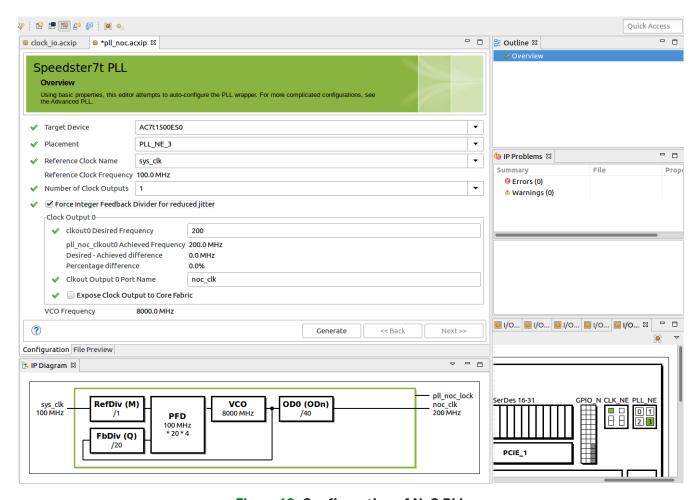

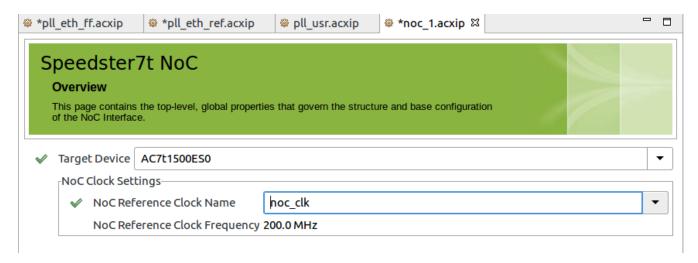

| ١                 | NoC                                          | 82 |

|                   | Ethernet PLLs                                |    |

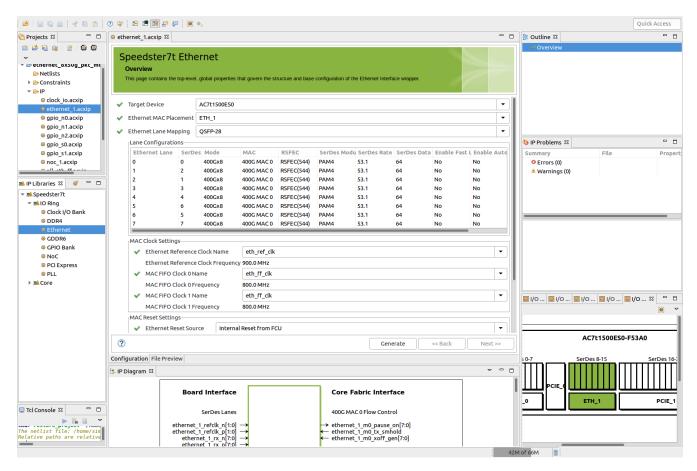

|                   | thernet Interface                            |    |

| C                 | Check for Errors and Generate the Bitstream  | 87 |

| Gen               | erated Constraint files                      | 87 |

| Chap              | ter - 8: Extended Features                   | 88 |

| Low               | Latency                                      | 88 |

| Loop              | oback                                        | 88 |

|                   | Direct (Local) PMA Loopback Mode             |    |

| F                 | Reverse SerDes Loopback Mode                 | 88 |

| L                 | oopback Limitations                          | 88 |

| Revis             | ion History                                  | 90 |

# Chapter - 1: Introduction

## Summary

Speedster®7t FPGAs include high-speed Ethernet interfaces which can support a wide variety of Ethernet packet protocols and speeds of up to 400 Gbps per channel. These Ethernet interfaces are paired with the latest generation SerDes which individually support 100 Gbps data rates. With eight of these SerDes per Ethernet interface, each interface can support 2× 400 Gbps Ethernet IP channels.

The number of Ethernet interfaces varies according to the device. In the descriptions below, the Speedster7t AC7t1500 is used as an example. This device has two Ethernet interfaces, allowing for 4× 400 Gbps interfaces, for a combined total bandwidth of 1.6 Tbps.

## **Features**

## 400G/200G PCS Layer

- 400G over 8× 50G SerDes or 4× 100G SerDes

- 200G over 4× 50G SerDes or 2× 100G SerDes

#### Note

400G/200G do not support 25G SerDes. 16× 25G or 8× 25G configurations are not available.

## 100G PCS Layer

- 100G Base-R PCS according to IEEE 802.3 Clause 82 specification

- 2× SerDes lane with 53 Gbps or 1x SerDes lane with 106 Gbps

- 4× SerDes lane with 25G (KR4) or 26.5G (KP4)

- Supports Reed-Solomon FEC (RS-FEC) implementing RS(528, 514) and RS(544, 514) for 100G-KR and 100G-KP applications respectively

## 10/25/40/50G PCS Layers

- Configurable Base-R PCS compliant with IEEE 802.3 Clauses 49, 82, 107, 133 for 10G, 25G, 50G operation respectively

- Independent 64bit XLGMII MAC interfaces per channel

- Supports Reed-Solomon FEC (RS-FEC) implementing RS(528, 514) and RS(544, 514) for 25G and 50G applications

- Optional support for EEE fast-wake (i.e., transfer of LPI sequences, no deep sleep)

- Optional Base-R (Firecode) FEC according to Clause 74 of IEEE 802.3

## Reed-Solomon FEC (RS-FEC)

- Support for RS(528, 514) (KR) codewords and RS(544, 514) (KP) depending on the mode of operation

- Support for RS(272, 258) low-latency variant

- Support for 25G (Clause 108) and 50G (Clause 134) and 25/50G Ethernet Consortium specifications

- Support for error indication to PCS when uncorrectable errors are detected

#### MAC

- 1588 precision timing, one-step operation, for all data rates, 10 to 400G

- IEEE 802.3br is supported in 10...100G by providing two transmit and receive interfaces to the application

## System Multirate and Multichannel

The Ethernet interface can be configured with up to eight lanes of SerDes and PCS. Each lane is independently usable for 10G, 25G, 50G or 100G Ethernet rates:

- Up to four 50G Ethernet channels using two 25 Gbps lanes each

- Up to two 100G Ethernet channels using four 25 Gbps lanes each

- Up to four 100G Ethernet channels using two 50 Gbps lanes each

- Up to two 200G Ethernet channels using two 50 Gbps lanes each

- Up to four 200G Ethernet channels using two 100 Gbps lanes each

- Up to two 400G Ethernet channels using four 100 Gbps lanes each

- One 400G Ethernet channel using eight 50 Gbps lanes

## **Architecture**

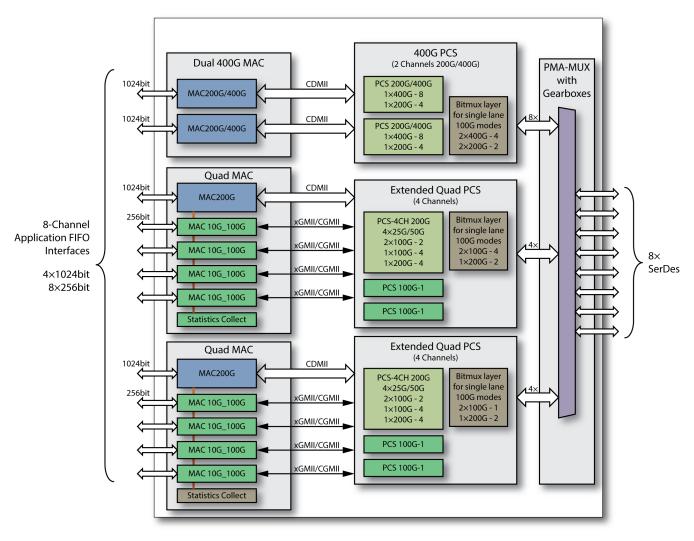

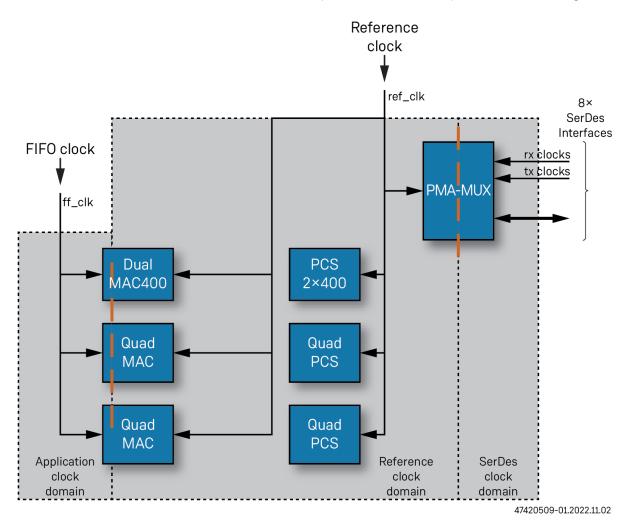

The architecture of each Ethernet interface is shown below.

47419925-01.2020.03.04

Figure 1: Ethernet Interface Block Diagram

# PMA (SerDes)

The physical media attachment (PMA) block consists of eight next-generation SerDes. Each SerDes can operate at up to 106.25 Gbps and down to 10.3125 Gbps. In normal operation the PMA block uses a dedicated mux to connect the SerDes directly to the PCS layer. If the SerDes is required for applications other than Ethernet (or for user-provided Ethernet PCS and MAC), then the PMA mux can be set to connect the SerDes interface directly to the fabric.

#### **Note**

The PMA mux must be switched for all SerDes signals within an interface. Therefore, if any SerDes from an Ethernet interface is used directly, then all SerDes from that group are switched to the fabric and the related Ethernet MAC and PCS are no longer available for use.

## **PCS**

The physical coding sublayer (PCS), connects between the SerDes and the MAC. Consisting of a dual-channel 400G PCS configurable to support either 2× 200G or 2× 400G operation, and a twin Quad-PCS, the components can be configured as a combined four channel PCS supporting up to a single channel of 200G operation, or four channels with up to 100G per channel. The PCS layer provides the coding functions for the various channel rates supported, including Reed-Solomon error correction of RS(528, 514) (KR) and RS(544, 514) (KP) code words. In addition, support for 25G (Clause 108) and 50G (Clause 134) error correction and coding are also supported.

#### MAC

The media access controller (MAC) is constructed from three blocks: one dedicated dual channel 400G MAC for 400G/200G operation which connects to the dual channel 400G PCS, and two instances of a Quad-MAC, each connecting to a Quad-PCS. Each Quad-MAC can support a single channel of 200G, or four channels operating at 100G down to 10G per channel. The dedicated 400G MAC is optimized for higher data rates and the wider bus widths necessary for the faster interfaces. The Quad-MAC is equally optimized for multiple channels of lower data rates.

# **Specifications**

## Channels

Each Ethernet interface can support the following combinations of data rates:

**Table 1: Channel Configurations**

| Mode x<br>Lanes | SerDes<br>Lanes<br>(per<br>Channel) | SerDes<br>Rate per<br>Lane  | Possible<br>No. of<br>Channels | Description (with Coding Options)                       | PMA<br>Width | PMA Interface<br>Frequency                | PMA<br>Electrical |

|-----------------|-------------------------------------|-----------------------------|--------------------------------|---------------------------------------------------------|--------------|-------------------------------------------|-------------------|

| 400G × 8        | 8                                   | 53.125G                     | 1                              | 400G over 8 lanes (2:1 bitmux).                         | 64           | 830.078125 MHz                            | PAM4              |

| 400G × 4        | 4                                   | 106.25G                     | 2                              | 400G over 4 lanes (4:1 bitmux).                         | 128          | 830.078125 MHz                            | PAM4              |

| 200G × 4        | 4                                   | 53.125G                     | 2                              | 200G over 4 lanes (2:1 bitmux).                         | 64           | 830.078125 MHz                            | PAM4              |

| 200G × 2        | 2                                   | 106.25G                     | 4                              | 200G over 2 lanes (4:1 bitmux).                         | 128          | 830.078125 MHz                            | PAM4              |

| 100G × 4        | 4                                   | 25.78125G<br>or<br>26.5625G | 2                              | 100G over 4 lanes (no FEC, RSFEC-<br>KR4 or RSFEC-KP4). | 32           | 805.6640625 MHz<br>or<br>830.078125 MHz   | NRZ<br>or<br>PAM4 |

| 100G × 2        | 2                                   | 53.125G                     | 4                              | 100G over 2 lanes (RSFEC-KP 2:1 bitmux).                | 64           | 830.078125 MHz                            | PAM4              |

| 100G × 1        | 1                                   | 106.25G                     | 8                              | 100G over 1 lane (RSFEC-KP 4:1 bitmux).                 | 128          | 830.078125 MHz                            | PAM4              |

| 50G × 2         | 2                                   | 25.78125G<br>or<br>26.5625G | 4                              | 50G over 2 lanes (RSFEC-KR or RSFEC-KP).                | 64           | 402.83203125 MHz<br>or<br>415.0390625 MHz | NRZ<br>or<br>PAM4 |

| 50G × 1         | 1                                   | 53.125G                     | 8                              | 50G single lane (RSFEC-KP 4:1 bitmux).                  | 64           | 830.078125 MHz                            | PAM4              |

| Mode x<br>Lanes        | SerDes<br>Lanes<br>(per<br>Channel) | SerDes<br>Rate per<br>Lane | Possible<br>No. of<br>Channels | Description (with Coding Options)                                                                                         | PMA<br>Width     | PMA Interface<br>Frequency | PMA<br>Electrical |

|------------------------|-------------------------------------|----------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------|-------------------|

| 40G × 4                | 4                                   | 10.3125G                   | 2                              | 40G over 4 lanes (optional Base-R (Firecode) FEC according to Clause 74 of IEEE 802.3).                                   | 32               | 322.265635 MHz             | NRZ               |

| 25G × 1                | 1                                   | 25.78125G                  | 8                              | 25G single lane (66b or RSFEC-KR).                                                                                        | 32               | 805.6640625 MHz            | NRZ               |

| 10G × 1                | 1                                   | 10.3125G                   | 8                              | 10G single lane (66b).                                                                                                    | 32               | 322.265635 MHz             | NRZ               |

| 200G × 2 +<br>100G × 1 | 2 + (2×1)                           | 106.25G                    | 1 set                          | One channel of 200G over 2 lanes, (4:1 bitmux) plus 2 channels of 100G, each over 1 lane (RSFEC-KP 4:1 bitmux).           |                  | 830.078125 MHz             | PAM4              |

| 200G × 2 +<br>100G × 2 | 2 + (2×2)                           | 106.25G<br>and<br>53.125G  | 1 set                          | One channel of 200G over 2 lanes,<br>(4:1 bitmux) plus<br>2 channels of 100G, each over 2<br>lanes (RSFEC-KP 2:1 bitmux). | 128<br>and<br>64 | 830.078125 MHz             | PAM4              |

## **Bitmux**

Bitmux refers to a layer of multiplexing that occurs between the PCS and the SerDes. This multiplexing provides the ability to widen the data interface to the PCS (and MAC) while reducing the overall system frequency.

For example, 400G-8 requires 8 50G SerDes lanes. From the Channel Configurations (see page 10) table above, it can be seen that when configured as 50G, the SerDes is set to a 64-bit interface, operating at 830MHz. By using a 2:1 bitmux, the data bus is widened to 16 lanes of PCS, with each PCS operating at 415 MHz.

## SerDes

## **SerDes Pad Numbering**

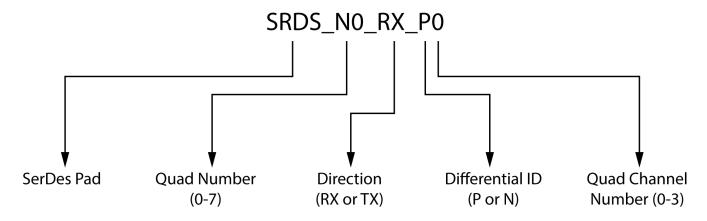

The SerDes pads have a consistent numbering scheme to assist with board layout and simulation.

47419925-02.2021.01.09

Figure 2: SerDes Pad Numbering

In total, for the Speedster7t AC7t1500, there are 32 SerDes lanes, configured as eight quads, each of four lanes. Only a subset of these SerDes are connected to the Ethernet subsystems on a device. These assignments are detailed in SerDes Quad Assignment (see page 12) below.

#### **SerDes Quad Assignment**

Each Ethernet subsystem uses two Serdes Quads, giving eight SerDes lanes in total. The SerDes Quads associated with each Ethernet subsystem are detailed in the following table.

Table 2: SerDes Quads per Ethernet Subsystem

| Device   |                        | Register Name          |                        |                         |  |  |  |  |

|----------|------------------------|------------------------|------------------------|-------------------------|--|--|--|--|

|          | Ethernet Si            | ubsystem 0             | Ethernet S             | Subsystem 1             |  |  |  |  |

|          | Lower Quad (Lanes 0-3) | Upper Quad (Lanes 4-7) | Lower Quad (Lanes 0-3) | Upper Quad >(Lanes 4-7) |  |  |  |  |

|          | SERDES_0 SERDES_1      |                        | SERDES_0               | SERDES_1                |  |  |  |  |

| AC7t1500 | SRDS_N6                | SRDS_N7                | SRDS_N4                | SRDS_N5                 |  |  |  |  |

#### SerDes Lane Mapping

In order to provide additional flexibility for board layouts, the internal SerDes lanes can be remapped to the SerDes pads. This mapping flexibility allows a single board design to support a number of common connector standards. The eight internal SerDes channels are mapped into a different sequence of SerDes pads, numbered as SerDes Lane ID 0-7, as shown in the SerDes Lane Mapping (see page 12) table below. This mapping is independent of the SerDes speed. For any single design, the mapping is static. Mapping is selected during the Ethernet subsystem configuration and is set by the generated bitstream. See the Ethernet Interface section in Speedster7t Ethernet IP Software Support in ACE (see page 86).

Table 3: SerDes Lane Mapping

| SerDes Lane ID | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|----------------|---|---|---|---|---|---|---|---|

| Linear         | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| QSFP-28        | 0 | 2 | 1 | 3 | 4 | 6 | 5 | 7 |

| QSFP-DD        | 0 | 2 | 4 | 6 | 5 | 7 | 1 | 3 |

In the SerDes Lane Mapping (see page 12) table, above, the top row represents the device pads. Thus, SerDes Lane ID 0 would equate to pins SerDes Quad 0, Lane 0 ( $SRDS_N0_TX_P0$  etc.). SerDes Lane ID 1 would be pins SerDes Quad 0, Lane 1 ( $SRDS_N0_TX_P1$  etc.). The lower rows represent which internal SerDes lane is mapped to the corresponding SerDes Lane ID. For example, if QSFP-28 is selected, then SerDes Lane ID 1 is driven by the internal SerDes channel 2. SerDes Lane ID 1 pads equate to pad pairs  $SRDS_N0_TX_N1/P1$  and  $SRDS_N0_TX_N1/P1$ .

# System Latency

When considering latency, consider the whole system end-to-end latency. Although SerDes (PMA) latency values are often published, these neglect the significant latency introduced by the MAC and PCS layers.

For the Speedster7t FPGA, the following transmit and receive latencies have been measured between the SerDes pad and the NAP ingress and egress interface.

Table 4: Speedster7t SerDes Transmit and Receive Latencies

| Rate | Configuration     | TX latency | RX latency |

|------|-------------------|------------|------------|

| 10G  | 1x10G Single NAP  | 204ns      | 204ns      |

| 25G  | 1x25G Single NAP  | 360ns      | 360ns      |

| 50G  | 1x50G Single NAP  | 215ns      | 215ns      |

| 50G  | 2x25G Single NAP  | 235ns      | 235ns      |

| 100G | 2x50G Single NAP  | 177ns      | 177ns      |

| 100G | 4x25G Single NAP  | 150ns      | 150ns      |

| 400G | 8x50G packet mode | 165–187ns  | 167–189ns  |

# Chapter - 2: System Architecture

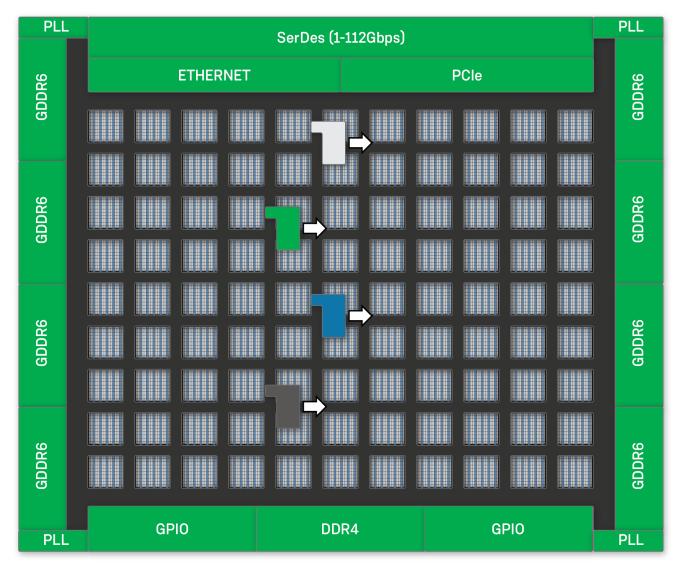

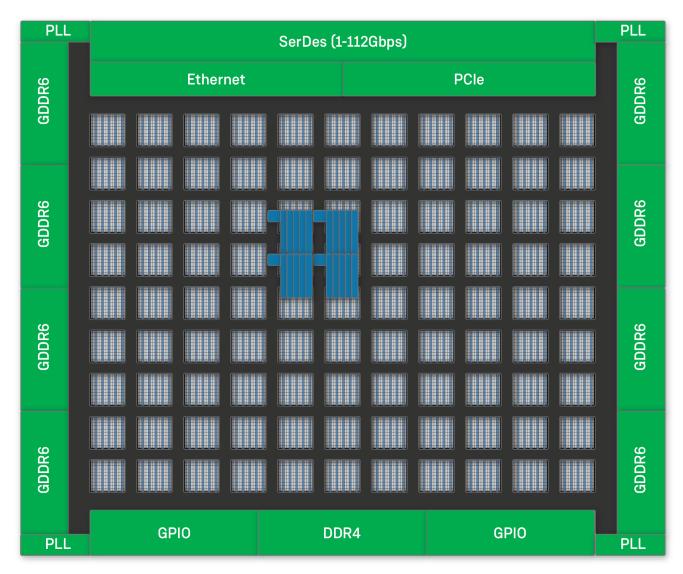

# Ethernet Interface System Architecture

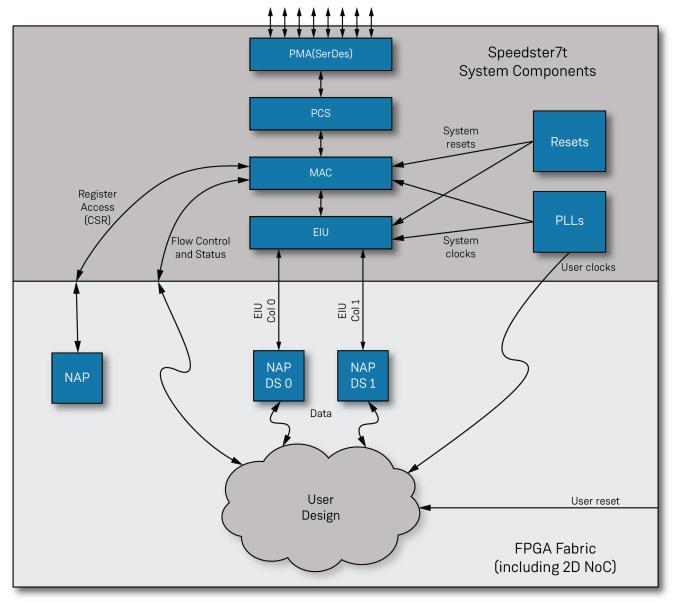

Due to the fully integrated architecture of the Speedster7t FPGA, the connections to and use of the Ethernet interface subsystem are different from what might be expected. In previous FPGA architectures, an RTL wrapper which contained the Ethernet interface (perhaps including models of the SerDes) would be generated. This wrapper would then be instantiated within a design and directly connected to the clock, reset, status and data ports. It is expected that the correct clock and reset strategies are followed, and the integrity of the data connections are confirmed.

With a Speedster7t FPGA, the usage methods and connections are very different. The full Ethernet interface, containing MAC, PCS and PMA (SerDes) is fully integrated within the Speedster7t FPGA system components. The MAC connects via an Ethernet interface unit (EIU (see page 17)) directly to the 2D network-on-chip (NoC). These components and the connections between them are not user accessible and the user design cannot connect directly to the Ethernet interface components. This architecture is detailed below (see page 15).

70522135-01.2022.11.01

Figure 3: Ethernet Interface System Architecture

## Data Flow

The basic data flow of a user Ethernet design is as follows:

- Transmit data, in the form of whole packets, is input to a NAP

- The packet flows up the 2D NoC column to the EIU (see page 17)

- Within the EIU, the packet can be passed through or stored and forwarded depending on the required mode

- For the advanced modes (Packet and Quad Segmented Modes (see page 18)) the EIU assembles and formats the packets accordingly

- The whole packet is transmitted in parallel form to the MAC which processes the packet adding preambles and FCS

- The packet is passed through the PCS to the SerDes, and on to the serial pins of the device

Packet reception is a reverse of the above sequence.

With reference to the above architecture (see page 15), connections must be made to the Ethernet interface using the following methods.

#### **Data Connections**

Connections to the Ethernet data streams are made using network access points (NAPs) placed within the 2D NoC. The 2D NoC greatly simplifies access to the Ethernet interface with simplified data streams presented to the user design.

#### Note

For data streams, the user design only connects to the NAPs and not directly to the MAC or EIU.

For full details of the NAP data connections, refer to NAP Data Connections (see page 19).

## Status and Flow Control Signals

Although the data streams, and accompanying metadata are delivered directly from the NAP, flow control and MAC status are connected directly to the FPGA fabric using the Ethernet direct-connect (DC) interface. When the Ethernet interface is configured within ACE, the appropriate flow control and status signals are created and set to be connected via the DC Interface to the FPGA fabric. Direct connections can then be made to these signals within the user design. These signals are detailed in the Direct-Connect Interface table (see page 30).

#### Note

The names and types of signals vary according to the configuration of the various MACs. Each MAC type has a different set of control and status signals.

## Control and Status Registers

Access to the internal Ethernet controller registers is also performed via the 2D NoC. The access is performed using a NAP set for AXI-4 mode which is used to access the control and status register (CSR) address space. This NAP can access any of the control registers in any of the interface subsystems on the Speedster7t FPGA. Similar to the data streams, the user design does not connect directly to the MAC or PCS. Instead, access to the CSRs is only supported via the 2D NoC.

#### Note

Correct configuration of the Ethernet interface is performed at power-up using the ACE-generated configuration. Typically, a user design would only require CSR access to monitor status or to enable or disable extended features.

## IP Generation and Configuration

Generation and configuration of the Ethernet interface is performed using ACE I/O Designer as detailed in Speedster7t Ethernet IP Software Support in ACE (see page 81). The configuration created within ACE sets the appropriate channel modes while ensuring the correct clocks and frequencies are provided to the Ethernet interface. ACE subsequently generates the following files:

- Ethernet Interface Bitstream File This file is merged with other bitstream files during final bitstream

assembly and programs the Ethernet interface upon FPGA power-up, ensuring the Ethernet interface is

ready for operation when the device enters user mode.

- **Simulation Configuration File** This file is input to the simulation environment to set Ethernet interface configuration.

With the above generation and configuration flow combined with the fully integrated nature of the Speedster7t FPGA, ensuring that the correct clocking and reset strategies are followed is no longer the responsibility of the user. The Speedster7t FPGA, combined with ACE, manages these low-level tasks freeing users to concentrate on the core parts of their design.

## **FIU**

The Ethernet interface unit (EIU) is unique to the Speedster7t family of FPGAs. There is an EIU for each Ethernet interface and each instance manages the connection of the MAC data interfaces to the 2D NoC. The EIU adapts the traffic flow and performs clock domain crossings between the 2D NoC and the MAC. It is further responsible for dividing the traffic when one of the 400G or 200G packet or quad modes is selected. For all modes, the EIU is responsible for packetizing the traffic so it can be sent down the appropriate 2D NoC column to the correct NAP endpoint.

## NAP Columns

Each EIU supports two 2D NoC columns on which the Ethernet NAP endpoints can be located. The EIU only sends and receives packets to NAPs placed within those two columns. The particular columns on which an EIU is connected for each Ethernet interface is detailed in the table below (see page 17). Columns are numbered from 1, starting on the West side.

Table 5: Ethernet 2D NoC columns

| Device   | Ethernet S    | Subsystem     | Total 2D NoC Columns |

|----------|---------------|---------------|----------------------|

|          | 0             | 1             |                      |

| AC7t1500 | Columns 1 & 2 | Columns 4 & 5 | 4                    |

## Memory Buffering

The EIU has memory buffering primarily to handle the higher line rate packet division and rearrangement. In addition, the buffering is used for clock crossing and packetization. The EIU buffering operates in two modes according to the selected line rate:

For 200G and 400G Packet and Quad Segmented Modes (see topic (see page 18), below), the EIU

operates in a store-and-forward mode. Each whole packet is buffered until it is fully received from the 2D

NoC, and then it is forwarded to the MAC. A similar scheme operates for received packets.

• In all other modes, no buffering is performed; therefore, the EIU should be considered as a transparent block with minimal buffering. This mode places frequency and throughput restrictions on the NAPs. These restrictions are discussed below.

Each NAP only has a shallow buffer in order to support clock domain crossing. For a system design, the NAPs should also be considered transparent elements with minimal or no buffering capability.

### Clocks

The EIU bridges between the 2D NoC core operating frequency of 2 GHz and the MAC ff\_clk frequency domains. Each of these clock domains are user configurable. The 2D NoC operating frequency is fixed and a 2 GHz clock must be provided as detailed in Ethernet IP Software Support in ACE (see page 81). The minimum MAC ff\_clk frequencies are defined in the Reference and FIFO Clock frequencies (see page 40).

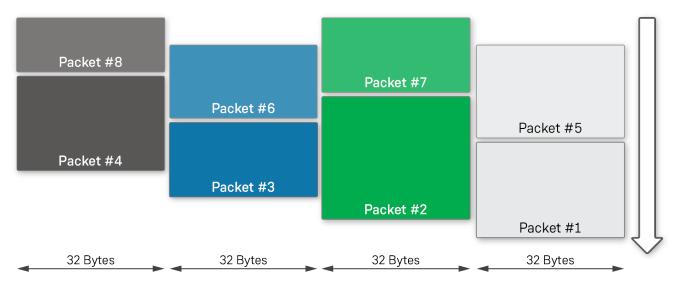

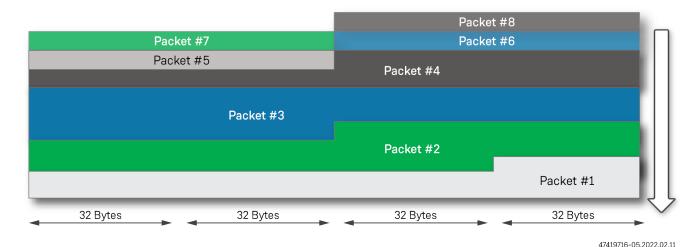

## Packet and Quad Segmented Modes

At higher data rates, 200G and 400G, it is impractical to transmit the full bandwidth through a single NAP (for 400 Gbps, this rate would require an operating frequency of 2 GHz for the associated fabric logic). Therefore, the EIU and 2D NoC support spreading the bandwidth across four NAPs. There are then two operating modes for these four NAPs:

- Quad segmented mode (QSI) The four NAPs are combined to form a single 1024-bit bus. The packet

is rotated around the four NAPs such that a new packet starts on the lane after the previous packet ended.

For example, with the NAPs identified as NAP-1 to NAP-4, then if the end-of-packet (EoP) word is output

on NAP-2, the next packet asserts its start-of-packet (SoP) word on NAP-3.

- Packet mode The four NAPs, (400G), or two NAPs, (200G), each process a whole packet, providing

four or two 100G streams to the fabric. Each NAP operates through its 256-bit data bus interface. The EIU

transmits the next available packet to whichever NAP is not currently transmitting a packet.

For additional details on each of these modes, including diagrammatic representations of the packet structure, refer to Speedster7t Ethernet 2D NoC Connectivity. (see page 34)

#### **Mode Considerations**

The two schemes each have advantages and disadvantages:

- For QSI, packet ordering is guaranteed as the NAPs present a single 1024-bit bus for both transmit and

receive. However, the width of the bus can create routing challenges, or difficulties with interfacing the

data to other interface subsystems, such as memory. The NAP native data width is 256 bits, requiring

buffering and pipelining for the 1024-bit bus to be written to another NAP. In addition, the requirement to

barrel shift the packet around the bus for different packet start lanes can add complexity to a design.

- Packet mode has the advantage of having whole packets contained within a single 256-bit bus, which can

then be easily connected to other NAPs, and hence to other interface subsystems or other parts of the

design. However, in packet mode the four streams are separate with no guaranteed packet ordering. In

many systems, this lack of ordering is not an issue. However, if point-to-point communication is being

used and packet ordering is required, then packet ordering must be implemented. This implementation

can be accomplished using the packet sequence number included in the NAP packet header.

#### Note

The Ethernet standard does not guarantee packet ordering due to the architecture of multiple routes through a network. Packet sequence ordering is supported in higher level protocols such as TCP/IP.

#### Warning!

For packet mode transmission, the Ethernet subsystem forwards a packet as it is delivered from the EIU. This ordering is not only dependent upon the order that packets are input to their respective NAPs, but also on the buffering within the NAP, 2D NoC and EIU. As a result, it is not possible to implement transmit packet ordering in packet mode.

The choice as to which mode is most suitable is based on many factors. These include the ease of interfacing to the 1024-bits of Quad Segmented mode, or the requirement for packet ordering performed at a hardware level. For reference, the two approaches are implemented within the *Speedster7t Ethernet Reference Designs Guide* (RD019). Refer to this Knowledge Base article for access.

## Configuration

The EIU configuration is controlled by parameters set on each NAP within the user design. These parameters set the NAP column location, channel speed, channel mode (packet or QSI), etc. These parameters are then used by both the simulation environment and ACE to ensure the EIU is correctly configured.

## NAP Data Connections

The data streams to and from the Ethernet MACs are interfaced to the user design with the use of NAPs. The specific NAP component is an ACX\_NAP\_ETHERNET primitive, full details of which can be found in the "Speedster7t Network on Chip Primitives" chapter of the *Speedster7t Component Library User Guide* (UG086). When connected to the EIU (see page 17), the NAP connections are as listed below.

**Table 6: Ethernet NAP Data Ports**

| Name         | Direction | Description                                                                                                                                                                     |  |  |

|--------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| rstn         | Input     | Asynchronous reset input. This signal resets the NAP interface. This signal does not affect the 2D NoC.                                                                         |  |  |

| output_rstn  | Output    | (Do not use) Reset output from NAP to fabric logic. Intended for use with Partial Reconfiguration. Signal controlled by write to configuration space. Currently fixed to 1 'b0. |  |  |

| clk          | Input     | All operations are fully synchronous and occur upon the active edge of the clk input.                                                                                           |  |  |

| tx_ready     | Output    | Asserted high when the NAP can accept data.                                                                                                                                     |  |  |

| tx_valid     | Input     | Assert high to issue a word of data to the NAP.                                                                                                                                 |  |  |

| tx_dest[3:0] | Input     | The 4-bit destination ID for the Ethernet packets. This value must be fixed to 4 ' hf to indicate that packets must be sent to the EIU reserved address.                        |  |  |

| tx_sop       | Innut     | Start of packet and end of packet indicators. These signals are required to be set for each packet                                                                              |  |  |

| tx_eop       | Input     | transmitted to the Ethernet subsystem.                                                                                                                                          |  |  |

| Name           | Direction | Description                                                                                                                                                                                                                                                                                         |  |  |

|----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| tx_data[292:0] | Input     | Ethernet packet to be transmitted to the EIU.  tx_data[255:0]: Packet data  tx_data[260:256]: Mod data. Valid when tx_eop is set  tx_data[290:261]: Transmit flags or timestamp. Timestamp is valid when tx_sop is set.  Transmit flags are valid on other packet cycles.  tx_data[292:291]: Unused |  |  |

| rx_ready       | Input     | Asserted high by user logic to indicate it is ready to receive data.                                                                                                                                                                                                                                |  |  |

| rx_valid       | Output    | Asserted high with each valid rx_data word.                                                                                                                                                                                                                                                         |  |  |

| rx_src[3:0]    | Output    | The 4-bit transmission source ID indicating the row that originated the data. This value is always 4 h f to indicate that the packet was received from the EIU. This output is generally unused.                                                                                                    |  |  |

| rx_sop         | Output    | Start of packet and end of Ethernet packet indicators.                                                                                                                                                                                                                                              |  |  |

| rx_eop         | Output    | Start of packet and end of Ethernet packet indicators.                                                                                                                                                                                                                                              |  |  |

| rx_data[292:0] | Output    | Received Ethernet Packet.  • rx_data[255:0] : Packet data  • rx_data[260:256]: Mod data. Valid when rx_eop is asserted.  • rx_data[290:261]: Receive flags or timestamp. Timestamp is valid when rx_sop is set. Receive flags are valid on other packet cycles.  • rx_data[292:291]: Unused         |  |  |

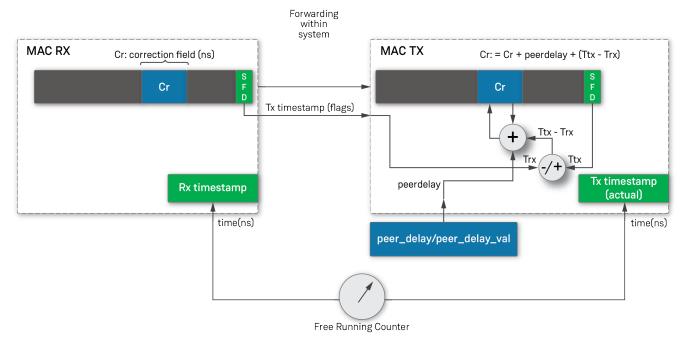

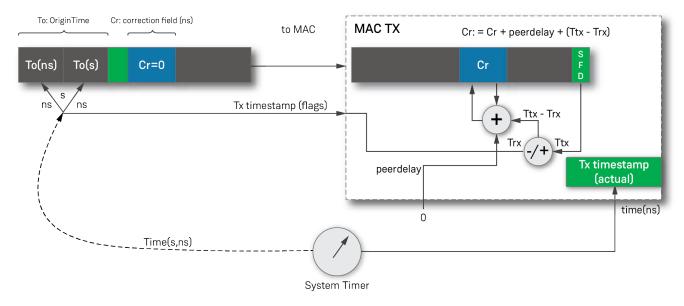

## **Timestamp**

For both transmit and receive, when SoP is asserted, the flag field, data[290:261], is set to equal the timestamp value:

- For transmission, the user design can insert a value into the flag field aligned with tx\_sop. This value is then captured by the outgoing MAC. If IEEE-1588 one-step correction is enabled, this timestamp value is used to update the correction field.

- For reception, if the user design is providing a timestamp count to the MAC, then the packet reception timestamp is captured (at the time the packet arrives within the MAC) and this value is provided into the flag field coincident with rx\_sop.

For full details of how the timestamp fields are generated and used, including IEEE-1588 1-Step updating, refer to IEEE Timestamping. (see page 68)

## Transmit Flags

In addition to the timestamp, during the remaining packet period, the flag field can contain a number of important flags to indicate packet status.

Table 7: Ethernet NAP Transmit Flags

| Slice <sup>(1)</sup> | Direction<br>(relative to<br>NAP) | Flag Name    | Description                                                                                                                                                                                                                                                                                         |

|----------------------|-----------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flag[16:0]           | Input                             | ID           | One-step update control vector. See IEEE Timestamping (see page 68)                                                                                                                                                                                                                                 |

| Flag[17]             | Input                             | Frame        | Set to indicate an IEEE 1588 event frame. See IEEE Timestamping (see page 68)                                                                                                                                                                                                                       |

| Flag[18]             | Input                             | Tx Error     | • 1 'b1 – Frame is transmitted with an incorrect CRC (no error control code is inserted). If CRC insert is set to 1 'b0, (CRC already in frame from application) then one bit within the last 4 bytes of the frame is changed to corrupt the CRC.  • 1 'b0 – No change to transmitted frame or CRC. |

| Flag[19]             | Input                             | CRC insert   | Add FCS field to transmitted frame.  1 'b1 - Transmit MAC appends a CRC (FCS) field of 4 bytes to the transmitted frame  1 'b0 - Transmit MAC does not append an FCS to the transmitted frame.                                                                                                      |

| Flag[20]             | Input                             | CRC invert   | Invert any inserted FCS field  • 1 'b1 – When set to 1 'b1, the CRC of the frame is inverted whenever CRC (flag[19]) or CRC override (flag[21]) are set.  • 1 'b0 – CRC is not inverted.                                                                                                            |

| Flag[21]             | Input                             | CRC override | CRC override. Only effective when CRC (flag[19]) = 1 'b0 .  • 1 'b1 - The CRC field of the frame passed to the MAC is overridden.  • 1 'b0 - The CRC field of the frame passed to the MAC is not modified.  If CRC (flag[19]) = 1 'b1, then CRC override has no effect.                             |

| Flag[22]             | Input                             | Class A      | Class A packet. Used for AVB rate limiting.                                                                                                                                                                                                                                                         |

| Flag[23]             | Input                             | Class B      | Class B packet. Used for AVB rate limiting.                                                                                                                                                                                                                                                         |

| Flag[29:24]          | Input                             | Unused       | Must be set to 6 b0.                                                                                                                                                                                                                                                                                |

| Slice <sup>(1)</sup> Direction (relative to NAP) Flag Name | Description |

|------------------------------------------------------------|-------------|

|------------------------------------------------------------|-------------|

#### **Table Notes**

1. If the user design does not require any of the transmit flags or the transmit timestamp field, the appropriate fields should be set to 1 'b0.

## **Transmit FCS Flags**

There are three flags that control CRC (FCS) insertion on transmitted frames. The insertion and modification is performed by the relevant transmit MAC. The CRC-32 polynomial is as specified in the 802.3 specification.

The following table lists the effects of these three flags in combination.

**Table 8: MAC FCS Transmit Flags**

| CRC<br>Insert | CRC<br>Override | CRC<br>Invert | Description                                                                                               |  |  |  |

|---------------|-----------------|---------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| 0             | 0               | х             | Pass-thru. The frame is not modified.                                                                     |  |  |  |

| 1             | x               | 0             | Append a CRC-32 field to the frame.                                                                       |  |  |  |

| 1             | х               | 1             | Append an inverted CRC-32 field to the frame.                                                             |  |  |  |

| 0             | 1               | 0             | Overwrite the CRC-32 field in the frame (calculates a new CRC-32 based on the frame data).                |  |  |  |

| 0             | 1               | 1             | Overwrite the CRC-32 field in the frame (calculates a new CRC-32 based on the frame data and inverts it). |  |  |  |

## Receive Flags

In addition to the timestamp, during the remaining packet period, the received flag field can contain a number of important flags to indicate packet status.

Table 9: Ethernet NAP Received Flags

| Slice                  | Direction<br>(relative<br>to NAP) | Flag<br>Name    | Description                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|------------------------|-----------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Flag[0]                | Output                            | Error           | Frame error indicator.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Flag[1] <sup>(1)</sup> | Output                            | Length<br>Error | Set to 1'b1 if the frame has an invalid length. This can be either a too short frame (less than 64 bytes), or a too long frame (length greater than the value programmed in register FRM_LENGTH), or a frame which has a different amount of payload than specified in the frame payload length field. Frames below 64 bytes in length might not be delivered to the NAP. |  |  |  |

| Slice                  | Direction<br>(relative<br>to NAP) | Flag<br>Name      | Description                                                                                                                                                                                                                                                                                       |

|------------------------|-----------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flag[2]                | Output                            | CRC<br>Error      | Set to 1'b1 if the frame was received with a CRC field that did not match the CRC calculated by the receive MAC. The frame is invalid.                                                                                                                                                            |

| Flag[3]                | Output                            | Decode<br>Error   | Set to 1'b1 if the frame was received with an unknown control character. The frame is invalid.                                                                                                                                                                                                    |

| Flag[4] <sup>(1)</sup> | Output                            | FIFO<br>Overflow  | Set to 1'b1 if a FIFO overflow was detected during frame reception. The received frame is truncated by the receive MAC and is invalid.                                                                                                                                                            |

| Flag[5] <sup>(1)</sup> | Output                            | Short<br>Frame    | Set to 1'b1 if a fault sequence (CDMII 0x9c) was detected while receiving the frame, or if the frame is a short frame (had less than 64 bytes on the line). If set due to a short frame the Length Error field is also set.                                                                       |

| Flag[6] <sup>(2)</sup> | Output                            | Inverted<br>CRC   | Set to 1'b1 if the frame was received with a CRC that matches the inverted CRC (inverted via XOR'ing the CRC with the value in the register CRC_INV_MASK) calculated by the receive MAC. When such frame is received by the MAC, the frame is still considered erroneous (CRC Error is also set). |

| Flag[7]                | Output                            | Transmit<br>Error | Set to 1'b1 if a transmit error control character (0xFE) has been received from the line. The frame is invalid.                                                                                                                                                                                   |

| Flag[8]                | Output                            | VLAN              | Set to 1'b1 to indicate that the frame is a VLAN frame (containing at least one VLAN tag).                                                                                                                                                                                                        |

| Flag[13:9]             | Output                            | Sequence<br>ID    | Frame sequence indicator. Details the order that the packet was output from the MAC. Used particularly in packet mode to reassemble the original packet sequence.                                                                                                                                 |

| Flag[29:14]            | Output                            | Unused            | Set to 16 'b0.                                                                                                                                                                                                                                                                                    |

#### **Table Notes**

- 1. A frame with length error due to FRM\_LENGTH violation or FIFO Overflow is truncated and the last bytes of the frame might contain arbitrary data.

- 2. The user application must monitor Inverted CRC and ignore the error indication in order to accept these frames if so required.

## **Receive Sequence ID**

The receive sequence ID is a 5-bit count which indicates the order in which packets were transmitted from the EIU (see page 17):

- For a single stream (all data rates up to and including 100G), a continuous count of receive sequence IDs is received at the single NAP.

- For Quad Segmented Mode (see page ) (200 and 400G), the same sequence ID is present on all segments of the same packet.

For Packet Mode (see page ) (200 and 400G), the next sequence ID in order could be presented at

any of the four possible NAP endpoints. If receive packet ordering is required, then each NAP must be

checked to locate the next packet in sequence.

#### **Receive FCS Control**

In the same way that the transmit MAC can insert CRC (FCS) fields into the outgoing frame, the receive MAC can optionally forward the received FCS field to the application, or it can remove it. Error checking of the frame against the FCS is still performed regardless of whether the FCS itself is forwarded or not.

Receive forwarding of the FCS is controlled by the COMMAND\_CONFIG register, bit[6], in each MAC. For full details of the programming interface refer to the Register Map (see page 45)

## Transmit Clock Frequencies

At all data rates, the complete Ethernet transmission subsystem must ensure that an Ethernet packet is transmitted as a contiguous whole. No part of the system must be allowed to run empty between a start of packet (SoP) and an end of packet (EoP). This restriction places differing requirements on the NAPs based on the selected data rate.

#### 10G/25G/50G/100G

In these modes the EIU is operating with no buffering. Therefore, it can be considered that the packet is transmitted directly from the NAP to the MAC. In this case, the NAP must operate at a sufficient frequency that matches the required line rate so that when the longest potential frame is transmitted, the whole frame can be sent within the required time.

### Minimum Ideal Packet Size Frequencies

Assuming a system needs to support jumbo frames (9000 bytes with a NAP data width of 256 bits), the following minimum transmit frequencies are required to not starve the MAC during packet transmission.

Table 10: NAP Ideal Packet Sizes Minimum Transmit Frequencies

| Data Rate<br>(Gbps) | Frequency<br>(MHz) |

|---------------------|--------------------|

| 10                  | 40                 |

| 25                  | 98                 |

| 50                  | 195                |

| 100                 | 390                |

#### **Note**

The transmit frequencies above only achieve the full stated line rate if all packets are of a length that fits the NAP data width exactly. Thus, all packet lengths are a multiple of 32 bytes.

The table above lists the minimum frequencies required for packets that are exact multiples of the NAP data width (32-bytes). For general operation over any packet size, it is necessary to increase the transmit frequency in order allow for loss of throughput caused when the packet width is not a multiple of 32-bytes. In order to calculate the worst-case frequency requirements, it is also necessary to consider any extra bytes, or byte intervals that are added to a packet before transmission.

#### Packet Overhead

The following bytes (or byte intervals) are added to an Ethernet packet on transmission:

- Preamble = 8 bytes

- Interpacket Gap (IPG) = Originally 12 bytes for lower Ethernet rates. For 10G and 25G the IPG is reduced to 5 bytes. For 50G, 100G, 200G and 400G it is reduced to 1 byte.

- Frame CheckSum (FCS) = 4 bytes. This can be generated as part of the packet to the NAP or added by the MAC, (as in the Achronix supplied designs). Similarly, it can be removed on reception by the MAC or passed through to the NAP. Any FCS added by the MAC is expressed as MAC\_FCS in the calculations below.

#### Minimum Non-Ideal Packet Size Frequencies

The general equation to calculate the required rate is:

Freq = Number of cycles to write packet to NAP × Data Rate / ((Packet Length + Preamble + IPG + MAC\_FCS) × 8)

The worst case length packet to transmit from the NAP is 65 bytes. This requires 3 cycles of the NAP  $tx_clk$ . The equation for a 65-byte packet, at a transmit rate of 100Gbps, with an IPG of 1 and the FCS created by the user design is then:

Freq =

$$3 \times 100G / ((65 + 8 + 1 + 0) \times 8) = 506.7MHz$$

.

The table below details the minimum non-ideal packet size transmit frequencies for both FCS from the MAC and FCS from the NAP.

Table 11: NAP Non-Ideal Packet Sizes Minimum Transmit Frequencies

| Data Rate (Gbps)   | IPG (bytes) | Frequency (MHz) |              |  |

|--------------------|-------------|-----------------|--------------|--|

|                    |             | FCS from NAP    | FCS from MAC |  |

| 10                 | 5           | 48              | 46           |  |

| 25                 | 5           | 121             | 115          |  |

| 50                 | 1           | 254             | 241          |  |

| 100 <sup>(1)</sup> | 1           | 507             | 481          |  |

#### **Table Notes**

1. The maximum rate at which a single NAP operates is 100G. For 200G and 400G line rates, the throughput is distributed across multiple NAPs.

If the user application determines to use larger IPG values, then the required frequency can be calculated using the formula above.

#### 200G/400G

For these line rates, the EIU operates in a store-and-forward mode, as it has to process each packet based on the stream configuration of quad segmented or packet mode. Therefore, there are no requirements on the minimum transmit frequency. The NAP can transmit at any frequency (up to a maximum of 507MHz) as the EIU waits until it has received a whole packet (including jumbo frames) before transferring that packet to the MAC. To achieve maximum throughput, the NAPs should operate at 507MHz as detailed in the table above (see page 25)

## Receive Clock Frequencies

For received packets, the the same requirements exist that a packet must not overflow during any stage as it is input to the MAC and sent via the EIU to a NAP.

#### 10G/25G/50G/100G

For these data rates the EIU is operating in transparent mode — a packet traverses directly from MAC to NAP. As the receive path is designed for packets of any length, including worst-case lengths of  $n \times 32 + 1$  bytes, the receive operating frequency must be high enough to support these worst-case scenarios.

**Table 12: NAP Lower Data Rate Receive Minimum Frequencies**

| Data Rate<br>(Gbps) | Frequency<br>(MHz) |

|---------------------|--------------------|

| 10                  | 48                 |

| 25                  | 121                |

| 50                  | 254                |

| 100                 | 507                |

#### 200G/400G

At these data rates, the EIU transmits packets directly to the NAP. The NAP receive clock rate must be sufficient to match the EIU transmission rate.

Table 13: NAP Higher Data Rate Receive Minimum Frequencies

| Data Rate<br>(Gbps) | Frequency<br>(MHz) |

|---------------------|--------------------|

| 200                 | 507                |

| 400                 | 507                |

#### Note

For 200G quad mode (using four NAPs) the receive frequency requirement of 507MHz gives a total potential bandwidth of greater than 400G. However, this receive frequency is required so that all NAPs in an EIU column can operate at the full bandwidth of up to 507MHz.

## Combined TX and RX Frequencies

Although it is possible to configure the NAPs as either transmit or receive only, in most scenarios it is expected that the same NAP is used for both transmit and receive. In these configurations, the higher of the transmit or receive clock frequencies must be met for the NAP single clock.

## Express and Pre-emptive MACs

To support the IEEE 802.3br standard, the Quad-MACs support both express and pre-emptive MAC channels for all Ethernet channel rates of up to 100G. For each of the four Quad-MAC channels, there are two interfaces, named pmac and emac. These names apply to both the direct connect signals and the register names. The preemptable MAC, (pmac), interface is the low priority interface where frames can be pre-emptable frames. MAC, (emac) interface is the high priority interface where frames are sent ahead of preemptable frames.

The selection of the appropriate MAC channel is made in the instantiation of the ACX\_NAP\_ETHERNET with the  $tx\_eiu\_channel$  and  $rx\_eiu\_channel$  parameters (see the *Speedster7t Component Library User Guide* (UG086)). Referring to the ACX\_NAP\_ETHERNET description table, **EIU Channels**, observe that EIU lanes 16-19, and 24-27 are used for pre-emptive MAC channels, and lanes 20-23 and 28-31 are used for express MAC channels.

#### Note

If the pre-emptive EIU channels are selected for a NAP, ensure that the pmac has been enabled as detailed below. If the channel is not enabled, no Ethernet traffic is sent or received via the NAP.

If only one MAC channel is required, the express MAC (emac) should be used.

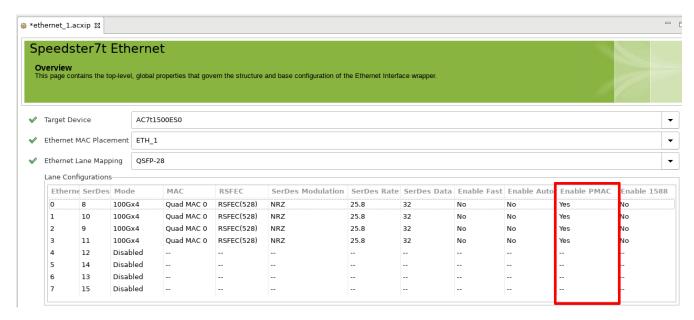

# **Enabling PMAC**

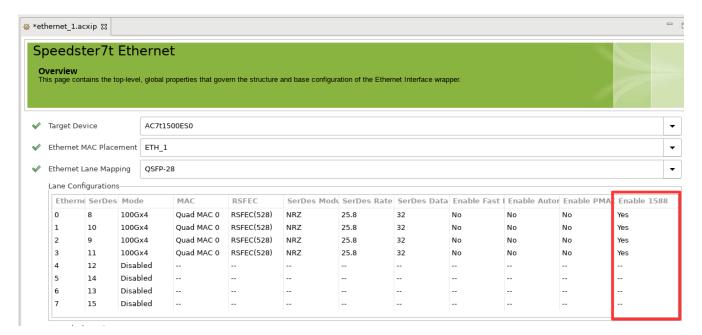

To enable the pre-emptive MAC (pmac), in the ACE Ethernet IP configuration wizard, set the **Enable PMAC** option to **Yes**. This is shown below for a 100G (4 x 25G) channel:

Figure 4: Enabling PMAC Within ACE

#### Note

Pre-emptive channels are only available for Ethernet channel rates of 100G or less. Enable PMAC cannot be set for channel rates of 200 or 400G.

## Flow Control

Flow control is a key factor in any Ethernet system design to ensure that at no stage in the packet data path are any packets dropped or lost. The usual cause of these issues are buffers over or under-flowing. Due to the integrated nature of the Ethernet subsystem, with data delivered by the EIU (see page 17) and 2D NoC, there are several buffers in the path from NAP to SerDes. The following describes what is required from a user design at a system level to ensure there are no packet losses.

## Transmit Rate Limiting

#### 400G and 200G

Both 400G and 200G rates operate in either packet or quad segmented (QSI) modes. In both of these modes the EIU (see page 17) stores and forwards the packets from the NAPs to the MAC. These EIU buffers are sufficient to store a jumbo frame. At the same time, the NAPs alert the user design via the NAP tx\_ready signal when they are able to transmit the next packet, or part of a packet in the case of QSI mode (see the Ethernet NAP Data Ports (see page 19) table). The user design does not need to have its own transmit rate control. Instead, it must use the NAP tx\_ready signal to control packet transmission.

#### 100G and Below

For rates of 100G and below, the NAP is transmitting directly through the 2D NoC and EIU to the MAC. There is inherent latency in this data path meaning that it is possible for a NAP to overflow the MAC before the MAC is able to indicate that it is full. In addition, in the case where a NAP is both receiving and transmitting, the operating frequency is then high enough to support worst-case length packets. With these higher frequencies, it is also possible that the NAP can exceed the transmit bandwidth, leading to overflows and data loss. Thus, for a 100G configuration with a NAP frequency set at 507 MHz, each NAP has a theoretical bandwidth of 130 Gbps, which is in excess of what the EIU would support from a single NAP.

#### Warning!

Based on the above, it is necessary to implement transmission rate limiting for an Ethernet NAP to ensure that the overall data rate is not exceeded when using 100G or below Ethernet NAPs.

In the example above, the maximum of 130 Gbps is 13/10 faster than the MAC and EIU can sustain. Therefore, in the *Speedster7t Ethernet Reference Designs Guide* (RD019), a transmit rate limiter control block is included which monitors the rate and maintains a 10/13 ratio maximum duty cycle for all transmissions. A version of this block or an equivalent should be used to ensure the correct transmit data rate is maintained.

#### Note

When using lower data rates with the EIU operating in transparent mode, it is suggested that any transmit flow control is performed between packets, rather than breaking up a single packet transmission. However, if very large packets are used, it might be necessary to insert flow control breaks at intervals within the packet.

## Receive Flow Control

Similarly to transmission, the reception of Ethernet traffic should not rely on buffering within the EIU or NAP. Therefore, any design should be structured to receive the full packet from a NAP without de-assertion of the NAP  $rx_ready$  signal. Even for 400G and 200G rates using packet or QSI mode, although the EIU uses store-and-forward on the packets, when transmission of a packet to a NAP has started, the EIU expects to be able to deliver the whole packet as a contiguous stream.

In the Speedster7t Ethernet Reference Designs Guide (RD019), where this receive flow control occurs, a FIFO is connected to the NAP to ensure that full packets can be received uninterrupted. Receive flow control is then enacted on the FIFO output as opposed to the NAP output. The receive FIFO can be composed of either four ACX\_LRAM2K\_FIFO (each set to 72-bit width each) or two Speedcore7t BRAM72K\_FIFO (set to 144-bit width each).

#### Note

It is strongly recommended, for all Ethernet data rates, that receive flow control is performed between packets, rather than during a single packet transmission.

# **Direct Connect Interface Signals**

## **Prefix**

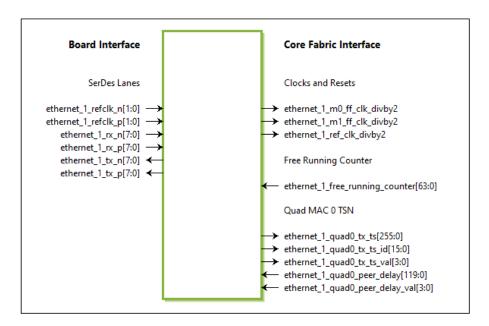

Configuration of the Ethernet Interface is performed using ACE I/O Designer, as detailed in Ethernet IP Software Support in ACE (see page 81). Each Ethernet Interface is named during generation. The Ethernet Interface name is prefixed to each signal name to distinguish different Ethernet Interfaces and to aid in having separate logical names for each instance. In the tables below, this prefix is shown as cprefix>\_ on each signal name.

## **MAC Identifier**

The control and status lines use identifiers to logically group signals from the same MAC:

- m[1:0] is for 400G/200G MAC

- quad0 is for QUAD0 MAC

- quad1 is for QUAD1 MAC

This identifier follows the prefix field in the signal name table below.

Table 14: Ethernet Controller Direct Connect Interface

| Pin Name <sup>(1)</sup>                                | Direction (4) | Width | Comments <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Clock                                                     |  |  |  |

|--------------------------------------------------------|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| Quad MAC <sup>(2)</sup>                                |               |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                           |  |  |  |

| <pre><prefix>_quad<n>_tx_hold_req</n></prefix></pre>   | Input         | 4     | Per channel 100G MACs. Holds and preempts the pmac transmission, if needed, allowing emac traffic to be transmitted. Can be used either for test and debug or when a higher layer function anticipates an emac frame being written and must prepare the MAC instead of requiring the MAC to prepare automatically based on the nonempty status of the eMAC FIFO.                                                                                                        | Synchronous to ff_clk_divby2.                             |  |  |  |

| <pre><prefix>_quad<n>_lpi_txhold</n></prefix></pre>    | Input         | 4     | Per channel 100G MACs. Prevents MAC transmission of a frame even if data is stored in the FIFO.                                                                                                                                                                                                                                                                                                                                                                         | Asynchronous Input. Synchronized internally to ref_clock. |  |  |  |

| <pre><prefix>_quad<n>_mac_stop_tx</n></prefix></pre>   | Input         | 4     | Per channel control of MAC transmit. When the respective input for each lane is asserted (1'b1), the MAC transmit state machine stops after any outgoing frame has been sent completely (does not corrupt outgoing frames). If further frames are available in the transmit FIFO, the MAC does not begin transmitting them until the respective mac_stop_tx is de-asserted (1'b0).                                                                                      | Synchronous to ref_clock_divby2.                          |  |  |  |

| <pre><prefix>_quad<n>_emac_xoff_gen</n></prefix></pre> | Input         | 32    | Transmit flow control generate (8 bits per channel) to emac/pmac. When PFC pause                                                                                                                                                                                                                                                                                                                                                                                        | Asynchronous input synchronized to ref_clock.             |  |  |  |

| <pre><prefix>_quad<n>_pmac_xoff_gen</n></prefix></pre> | Input         | 32    | mode is enabled, an 8-bit input vector is used to signal the creation of PFC control frames. When link pause mode is enabled, only the 0 bit per channel (bits 0,8,16,24) is used.                                                                                                                                                                                                                                                                                      |                                                           |  |  |  |

| <pre><prefix>_quad<n>_pmac_pause_on</n></prefix></pre> | Output        | 32    | Transmit paused/class congestion indication (8-bit value per channel) from emac/pmac. Bit 0 per channel (bits 0,8,16,24) is also used to indicate link pause. When asserted to 1'b1, indicates a running pause counter has been started because an Xoff frame (pause/PFC) was received. In link pause mode, the transmitter is also stopped when the command_config bit, PAUSE_PFC_COMP, is not set. When the PAUSE_PFC_COMP bit is set, the transmitter is not stopped | Synchronous to ref_clock_divby2.                          |  |  |  |

| Pin Name <sup>(1)</sup>                                                                  | Direction (4) | Width | Comments <sup>(6)</sup>                                                                                                                                                                                                                                                                                                           | Clock                                         |

|------------------------------------------------------------------------------------------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| <pre><prefix>_quad<n>_emac_pause_on</n></prefix></pre>                                   | Output        | 32    | and it is the responsibility of the application to assert mac_stop_tx to implement proper flow control.                                                                                                                                                                                                                           |                                               |

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> | Output        | 4     | General-purpose indication that the emac/pmac is configured to react on pause frames (1 bit per                                                                                                                                                                                                                                   | Synchronous to                                |

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> | Output        | 4     | channel). It is a direct result of the inverted COMM AND_CONFIG (PAUSE_IGNORE) control bit.                                                                                                                                                                                                                                       | reg_clock.                                    |

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> | Output        | 4     | General-purpose indication that the emac/pmac datapaths have been enabled. It is a direct                                                                                                                                                                                                                                         | Synchronous to                                |

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> | Output        | 4     | result of both the COMMAND_CONFIG (TX_EN and RX_EN) control bits. Per channel from 100G MACs. Can be left unconnected if not used.                                                                                                                                                                                                | reg_clock                                     |

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> | Output        | 4     | FIFO overflow truncation error indication (1 bit per channel). Asserted when the FIFO write                                                                                                                                                                                                                                       |                                               |

| <pre><prefix>_m<n>_ffe_tx_ovr</n></prefix></pre>                                         | Output        | 4     | control logic truncates a frame as either the FIFO had overflowed, or the frame transferred is larger than the FIFO when operating in storeand-forward mode.                                                                                                                                                                      | Synchronous to ff_clock_divby2.               |